基于MEMS強鏈和FPGA的USB移動硬盤數據加解密系統

3. 物理密鑰與密碼認證

物理密鑰是相對于邏輯密鑰而言的,邏輯密鑰通常以二進制形式存在于芯片內部ROM 區, 容易被破解。而物理密鑰固化在機械結構內部。本設計采用的反向嚙合齒輪集鑒碼機構所蘊含 的密鑰就屬于物理密鑰。它的結構相當隱含,不是專業人士即使知道了鑒碼機構,也很難推出 其密碼。

密碼認證開始時,USB 控制器把接收到的來自PC 的24 位待驗證二進制密碼以脈沖的形 式傳遞給強鏈。強鏈的電機會根據脈沖驅動碼輪。若密碼正確,反干涉齒輪*無摩擦的走通 一周回到原位;只要有一位密碼錯誤,反干涉齒輪*在該位卡死。USB 控制器根據強鏈的反 饋信號作出判斷,如果驗證通過,則將該系統枚舉成一個可移動磁盤,并把該正確密碼傳遞給 FPGA,作為AES 加密算法的密鑰;否則向PC 機返回驗證失敗的信息。

4. ATA 協議控制器的實現

從密碼認證通過,枚舉開始的那一刻起,USB 控制器得到了對硬盤的訪問權。 根據 ATA 協議,對支持Ultra DMA 傳輸方式的IDE 硬盤而言,操作歸結為兩種,對硬盤接 口寄存器讀寫以及對硬盤扇區進行Ultra DMA 批量扇區。為了對硬盤數據進行加解密,我們把 FPGA 插入連接GPIF 接口和硬盤接口的IDE 總線,這樣所有控制信號和數據信號都要通過 FPGA,受到FPGA 的監視和控制。

FPGA 必須實現有限狀態機,能夠對信號進行協議解析,區 分出那些需要加解密的扇區數據,也就是在Ultra DMA 傳輸過程中出現在數據總線上的數據。 在PIO 狀態時,FPGA 讓所有信號保持直通,因而讀寫硬盤接口寄存器的操作不受任何影響,但狀態機監測對硬盤接口寄存器的寫入操作。一旦發現寫入命令寄存器的命令代碼為DMA 讀 (0xC8 或0x25)或DMA 寫(0xCA 或0x35)命令,則有限狀態機進入DMA 狀態。

因為考慮到數據經加解密模塊會有200ns 左右的延時,如果控制信號仍然直通一定不能滿 足DMA 傳輸協議的時序要求,所以理想的辦法是把控制信號也延時相應的時間。

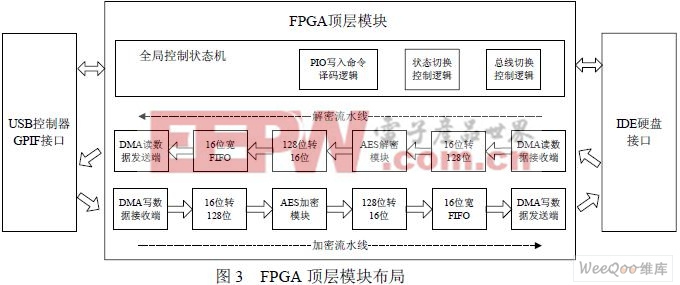

延時多少的確定很困難,況且也沒有必要,我們采取的方法是設計了三個主要模塊:數據 接收模塊、數據處理模塊和數據發送模塊,連成一條處理流水線,這樣既能對數據流進行完全 時序化的控制,又能維持較高的數據吞吐。如圖3 所示。數據接收模塊的任務是把硬盤發送過來的讀扇區數據或者USB 控制器發送來的寫扇區數 據正確的接收和緩存;數據處理模塊的任務是對扇區數據進行加密或解密處理;數據發送模塊 的任務是把處理完的結果數據發送出去。

由于數據流是雙向的,所以兩個方向上各有一條數據 收發流水線。在一次DMA 傳輸中,只有一條流水線是工作的,且它們暫時獲得IDE 總線的控 制權。

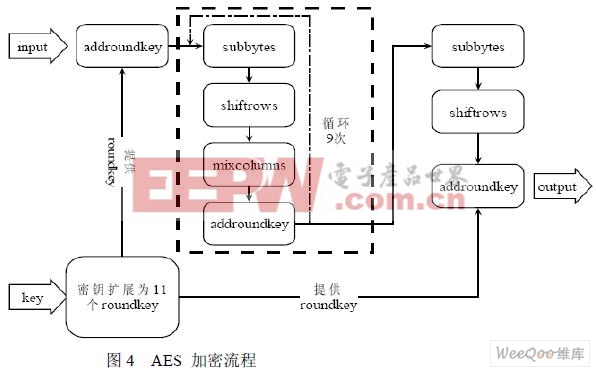

不失一般性,我們討論下執行DMA 讀命令的全過程。首先,在PIO 狀態下將DMA 讀命 令的代碼0xC8(或0x25)寫入硬盤的命令寄存器。此后狀態機進入DMA 讀狀態,總線切換給 DMA 讀數據接收模塊和DMA 讀數據發送模塊。DMA 讀數據接收模塊與硬盤進行握手確認, 啟動UDMA 讀傳輸,此后每當硬盤DMA strobe 信號(DMA 同步信號)發生跳變,就對16 位 硬盤數據總線進行采樣,并更新CRC 接收校驗;每采樣8 次則整合成一個128 位并行數據,提 供給AES 解密模塊,該模塊取走這128 位數據開始新一輪AES 解密迭代運算,同時輸出前一 輪處理完的128 位解密數據,并拆分為8 個16 位并行數據,陸續存入一個16 位寬的FIFO。與 此同時,DMA 讀數據發送模塊查詢到FIFO 中出現了數據,就開始不斷的從中讀取,并放在16 位數據總線上提供給USB 控制器,每放一次數據,便翻轉一次DMA strobe 電平使得USB 控制 器的GPIF 接口能夠同步接收數據,同時更新CRC 發送校驗。

當硬盤把所有指定數量的加密數據都發送給FPGA 后會收到FPGA 的CRC 接收校驗反饋, 若與硬盤內部的CRC 校驗一致,則硬盤認為這次DMA 讀命令被正確執行。

當 FPGA 把所有處理完的解密數據都發送給USB 控制器后也會收到USB 控制器的CRC 校 驗反饋,若與FPGA 內部的CRC 發送校驗一致,則可以認為一次完整的含解密的DMA 讀命令 被正確執行。

評論