基于USB 2.0協議的高速圖像傳輸系統

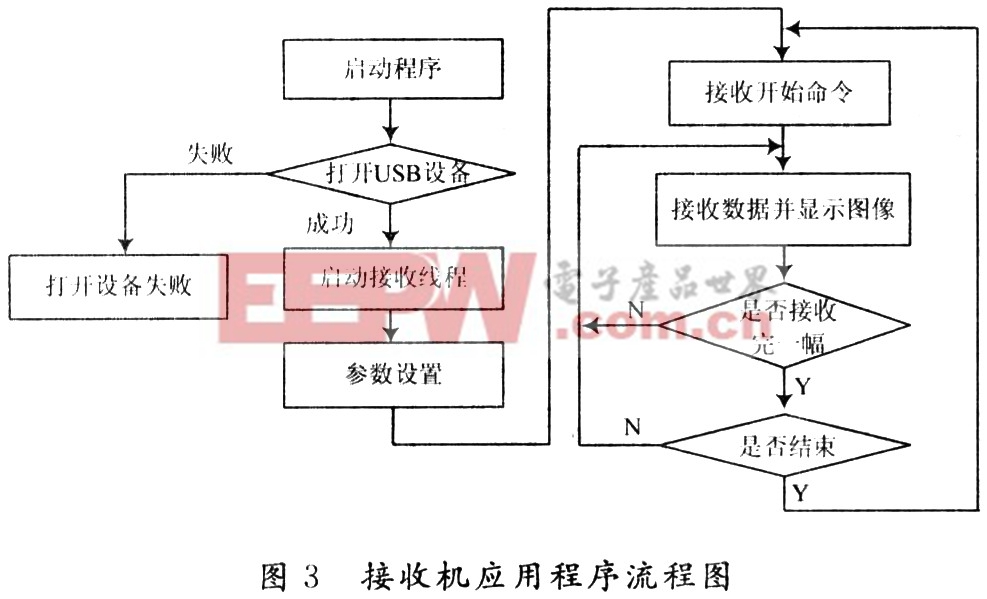

接收端應用程序流程圖如圖3所示。發送端應用程序流程類似,少了判斷圖像是否完整一幅,而多了傳輸完畢之后的圖像數據校驗。本文引用地址:http://www.104case.com/article/202594.htm

2 系統仿真及實現

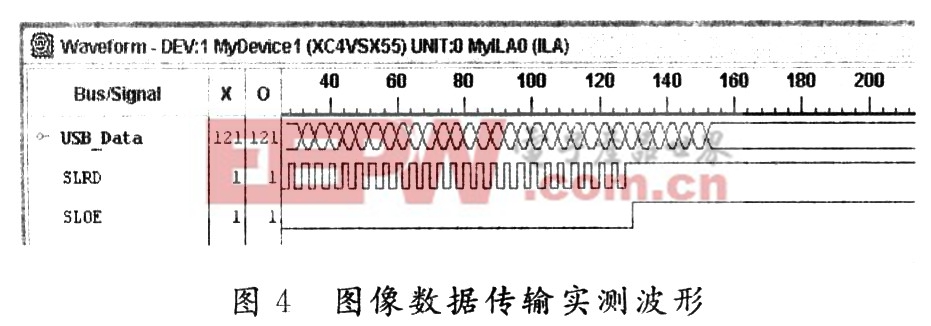

圖4所示為圖像發送系統主要端口的ChipScope實測波形,所用FPGA為V4-XC4VSX55。

USB_Data為傳輸的圖像數據。數據長度為16位,SLRD為異步讀取FD總線的時鐘,采用USB時鐘源48 MHz四分頻得到,FIFO指針在每次SLRD激活到撤消激活變化時累加,即每變化一次,讀取FIFO里16 b緩存數據一次。SLOE引腳為讀寫使能信號,默認低電平有效。從該實測圖可以看出,三路信號均符合異步讀取的時序要求。

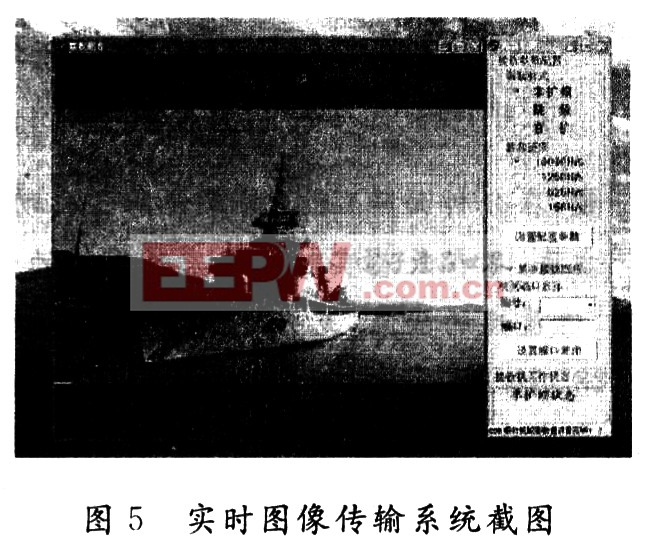

主機接收端應用程序采用Delphi語言編寫,圖像傳輸它采取傳輸的同時顯示圖像的形式。從上位機應用程序截取一幅接收圖像如圖5所示。該應用程序主要用于各種調制方式下圖像的傳輸。可以看到傳輸圖像清晰完整,連續顯示沒有滯后,沒有噪聲斑點。圖像經過USB接口傳輸后沒有數據丟失,比較清晰。實驗證明,圖像傳輸過程中,沒有出現丟幀的情況。滿足實時高速的圖像傳輸。

3 結 語

USB 2.0技術以其高速傳輸和使用方便受到廣泛的關注,其應用也必將越來越廣泛。上述設計方案有效地解決了圖像傳輸過程中的高速通信問題。系統中采用異步方式傳輸,采用芯片所提供四分頻時鐘,最高速率可達到192 Mb/s。采用FPGA和USB 2.0相結合的方式,數據處理能力得到極大的提高,由于采用CY7C68013A的Slave FIFO模式,可使用外部FPGA并按照用戶需求設計,增強使用功能的多樣性和靈活性。該方案亦可應用于大容量、高速度的實時數據采集,音頻及視頻傳輸等領域。

評論