USB2.0接口傳輸的FPGA控制與實現

2 系統的設計實現

系統結構如圖l所示,本設計中,應用程序是用戶界面;USB驅動用于連接用戶和底層硬件;USB2.O控制器68013用于FPGA和PC間的數據交互。

2.1 硬件結構

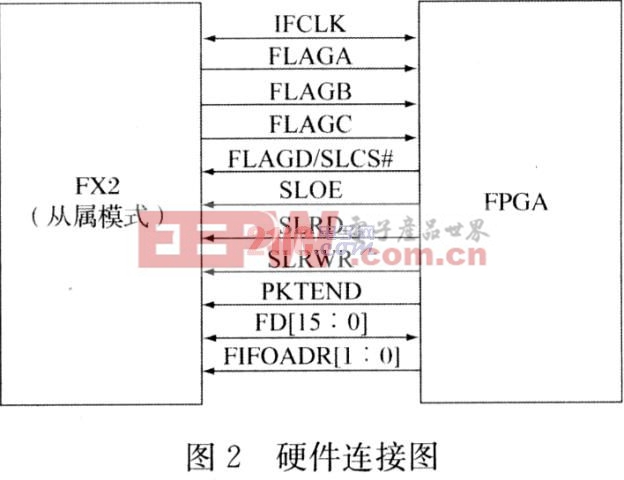

本系統硬件連接主要是由FPGA和USB2.0控制器,如圖2所示。同時也可以根據實際系統的需要,用FPGA實現預定功能,硬件接口模式有Slave FIFO和GPIF兩種接口模式。本方案采用Slave FIFO模式,當EZ-USB FX2工作于Slave FIFO時,外圍電路可像普通FIFO一樣對FX2中的端點2、端點4、端點6、端點8的數據緩沖區進行讀寫。圖2展示了這種模式下FX2和外圍電路的典型連接,其中,IFCLK為接口時鐘,可由芯片CY7C68013產生(30 MHz/40 MHz),也可由外部輸入(5MHz/48 MHz);FLAGA-FLAGD為FIFO標志管腳,用于映射FIFO的當前狀態;SLCS#為從屬FIFO的片選信號,低電平有效;FD[15∶O]為16位雙向數據總線;FIFOADDR[1∶O]用于選擇和FD連接的端點緩沖區;SLOE用于使能數據總線FD的輸出;SLRD和SLRWR可分別作為FIFO的讀寫選通信號;外圍電路可通過使能PKTEND管腳向USB發送一個IN數據包,而不用考慮該包的長度。

2.2 系統軟件

系統軟件設計主要包括3部分:VHDI代碼、USB固件程序(Firmware)以及應用程序。

評論