兩家歐洲大學研發300Gb/s 150GSa/s 7 位 DAC

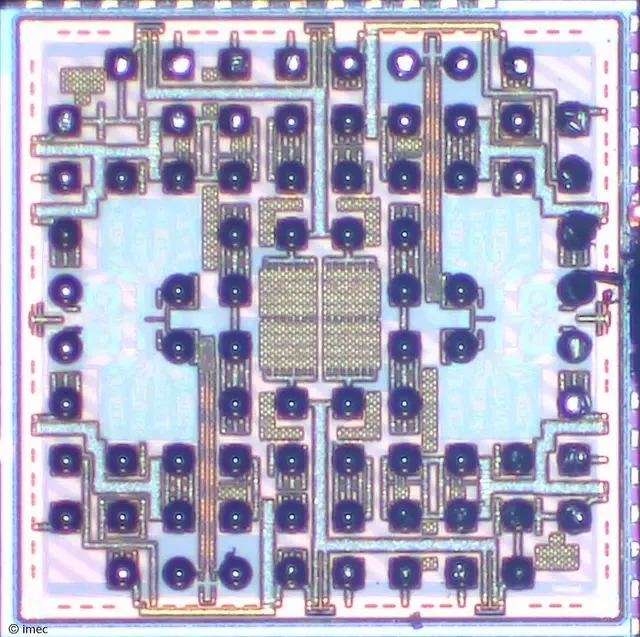

根特大學和比利時安特衛普大學的 imec 研究小組 IDLab 開發了一種采用 5nm FinFET CMOS 工藝制造的 7 位 150 GSa/s DAC,使用 PAM-4 調制可實現高達 300 Gb/s 的數據速率。

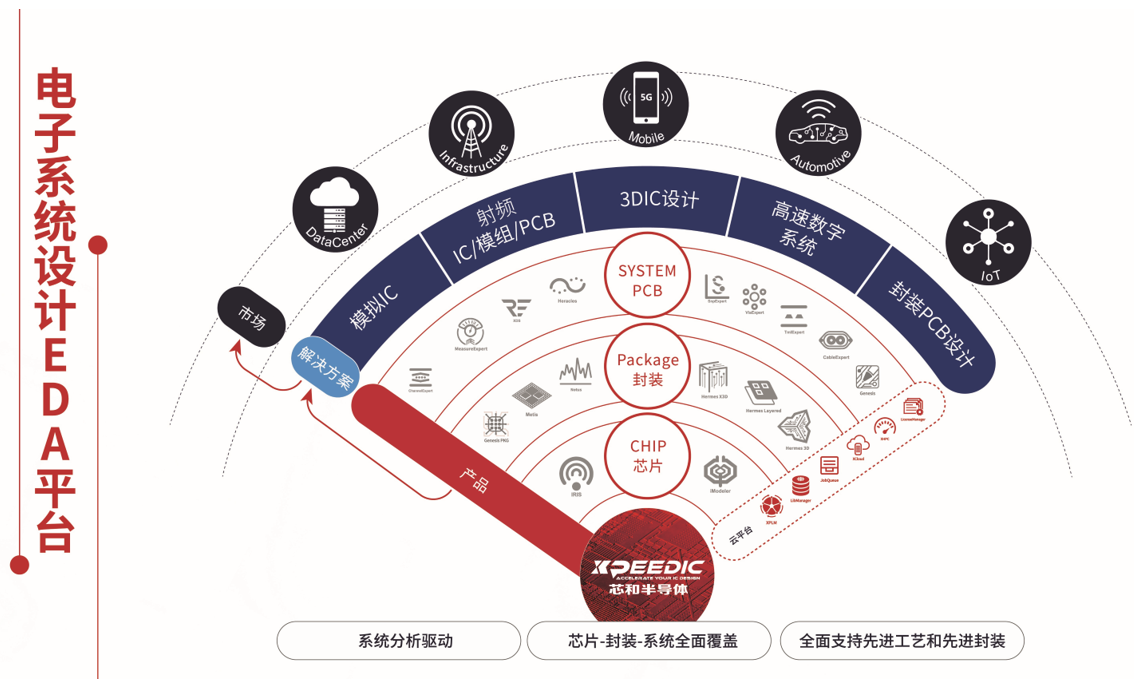

本文引用地址:http://www.104case.com/article/202506/471654.htmDAC 旨在滿足對更快數據中心鏈路日益增長的需求,將速度和能效相結合,為有線數據轉換設定了新標準。

隨著機器學習和 AI 等數據密集型應用程序變得越來越普遍,數據中心對更高數據傳輸速率的需求持續激增。

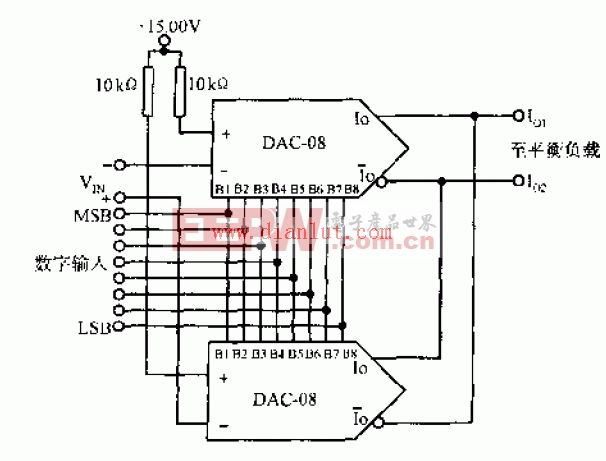

因此,超高速 ADC 和 DAC 對于確保下一代有線系統中的數據流至關重要。傳統架構經常不足,導致信號衰減和功率效率低下。

與此同時,隨著部署在大型數據中心基礎設施內的互連數量的增長速度超過計算量的增長速度,電源效率變得越來越重要。

PAM-4 已成為數據中心的首選調制方案,無需更多帶寬即可實現更快的數據傳輸。

這款 7 位 DAC 專為下一代數據中心鏈路而設計,目標是數據速率超過 200 Gb/s,并最終達到每通道 400 Gb/s。為了有效地管理這些速度,在 5nm FinFET 等高級 CMOS 節點中實施了必要的信號處理。因此,DAC 也必須在同一技術節點內實現。在縮放 CMOS 節點中集成如此復雜的架構,利用了 imec 在先進集成電路設計方面的獨特專業知識,“imec 高速收發器項目經理 Peter Ossieur 說。

為了優化電源效率,imec 對 DAC 架構進行了創新,將單晶電池的數量從 127 個大幅減少到 34 個。這最大限度地減少了開關活動,有效地降低了功耗(在 0.9V 和 0.96V 電源下降至 621 mW),而不會影響速度。這種減少還減少了寄生效應,從而在更高的數據速率下實現更精確的信號轉換。

Ossieur 補充道:“展望未來,該團隊旨在通過瞄準基于 3nm CMOS 技術的下一代 ADC 和 DAC,滿足對更快數據鏈路日益增長的需求。重點是將采樣率提高一倍,達到 300GSa/s,并將帶寬推高到 100GHz 以上。為了實現這樣的速度,imec 將利用其在模擬設計方面的專業知識,現在還將解決針對飛秒級精度的超低抖動時鐘生成電路的設計問題。

評論