PCIe 7.0規范發布,翻倍狂飆128GT/s

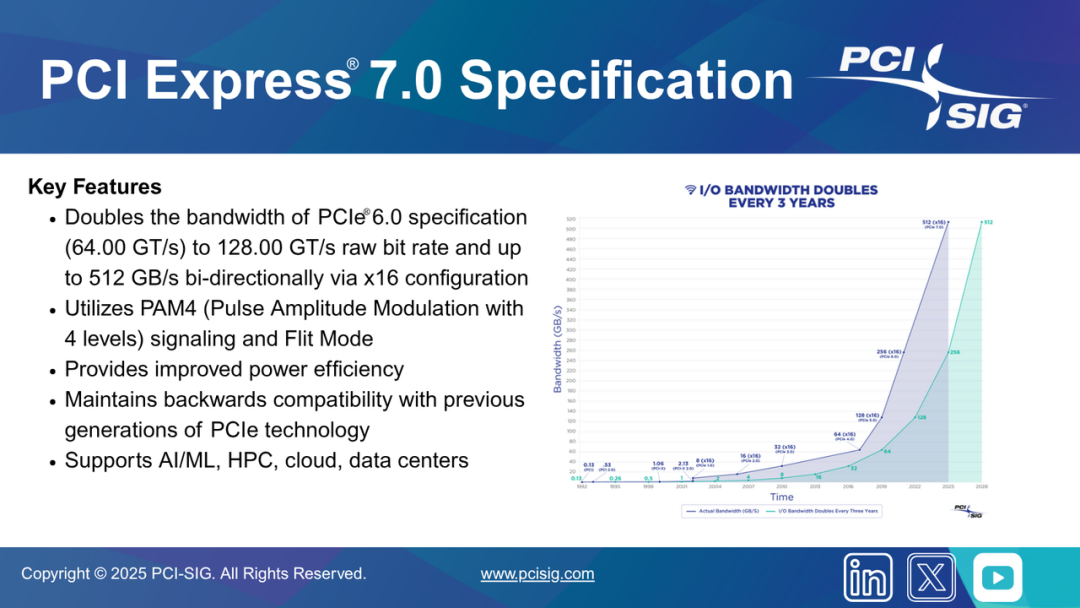

PCI-SIG 正式發布了 PCIe 7.0 規范。這是繼 PCIe 6.0 發布三年多以來的一次重要更新,新一代標準再次實現了傳輸帶寬的翻倍提升。

本文引用地址:http://www.104case.com/article/202506/471381.htm

PCIe 7.0 的原始比特率達到了 128.0 GT/s,在常用的 ×16 配置下,實際數據傳輸速度最高可達雙向每秒 512GB。這意味著,即便是在 ×4 的配置下,PCIe 7.0 的帶寬水平也可媲美上一代 PCIe 5.0 在 ×16 下的表現。

和 PCIe 6.0 一樣,PCIe 7.0 同樣采用了 PAM4 信號編碼方式,并進一步優化了能效表現。新的規范在提升性能的同時也保持了與此前各代 PCIe 技術的兼容性。目前,下一代 PCIe 8.0 的規劃工作也已同步展開。

PCI-SIG 主席兼首席執行官 Al Yanes 表示:「在過去二十多年中,PCIe 技術一直是高性能、低延遲 I/O 連接的首選解決方案。我們很高興宣布 PCIe 7.0 規范正式面世,這延續了我們一直以來每三年將 I/O 帶寬提升一倍的發展節奏。」

他同時指出,隨著人工智能應用的快速演進,對數據傳輸能力的需求持續增長。新一代 PCIe 技術能夠有效支持如超大規模數據中心、高性能計算、汽車電子以及航空航天等高帶寬需求領域的未來發展。

More Than Moore 首席分析師兼首席執行官 Ian Cutress 表示:「PCIe 規范的最終版本發布是一個特殊的時刻,盡管業界圍繞高速信號制定標準非常復雜,但通過 PCIe 技術實現的計算和網絡需求的增長卻達到了前所未有的水平。數據中心已準備好開始部署基于 PCIe 7.0 技術的網絡,而且幾乎我接觸到的每一家 ASIC 公司都已與 IP 提供商接洽,并準備從中獲益。盡管 PCIe 6.0 的部署已經非常流行且備受關注,但 PCIe 7.0 規范比以往任何版本都更受關注。」

PCIe 7.0 標準將于 2027 年完成預發布測試 (Pre-FYI),初始集成商名單預計將于 2028 年發布。

光學感知重定時器 ECN

除了發布規范之外,PCI-SIG 還宣布了新的光纖互連規范修訂,以實現更高的 PCI Express (PCIe) 技術性能。「光學感知重定時器工程變更通知 (ECN)」修訂了 PCIe 6.4 規范和新的 PCIe 7.0 規范,納入了基于 PCIe 重定時器的解決方案,從而提供了首個通過光纖實現 PCIe 技術的行業標準化方法。

PCI-SIG 總裁兼主席 Al Yanes 表示:「我們看到了基于 PCIe 技術的行業標準光互連的需求,而 Optical Aware Retimer ECN 是添加模塊化光解決方案的第一步。我們預計該技術將首先應用于人工智能/機器學習和云等數據中心應用。隨著 PCIe 技術逐漸普及,我們預見到眾多細分市場將出現創新用例。」

光學感知重定時器 ECN

無縫支持各種光學技術,用于現有符合 PCIe 6.4 和 7.0 規范的交換機、根復合體和端點硅片設計之間的光學互連

擴大機架和艙室的覆蓋范圍

允許跨電域和光域進行多路復用和數據映射

比銅纜解決方案更緊湊的實現

PCIe 標準發展歷程

自 2003 年推出以來,PCIe 發展至今已經從最初的 1.0 升級到了 7.0,下面我們來簡單了解下 PCIe 標準的演進歷史以及各代 PCIe 標準之間的主要差異

最早第一代 PCIe 1.0 標準于 2003 年推出,支持每通道 2.5GT/S 的傳輸速率和每通道 250MB/S 的數據速率。

2007 年初,第二代 PCIe 推出,每通道傳輸速度為 5 GT/s,吞吐量(帶寬)也增加了一倍,達到每通道 500MB/s,但由于 8b/10b 編碼方案的開銷占比為 20%,因此單 lane 的傳輸帶寬為 4 Gb/s。

PCIe 3.0 及以后的版本使用更高效的 128b/130b 編碼,將開銷占比降低到了 1.5%。通過減少開銷占比,PCIe3.0 的單 lane 傳輸帶寬相比 PCIe2.0 翻倍,達到 8 Gb/s,同時保持了與 PCle 2.0 版本軟件和機械接口的兼容性。PCIe 3.0 規范包含了 Base 和 CEM(卡機電)規范,其中基本規范里的電氣部分定義了集成電路級的電氣性能,并支持 8 GT/s 信令。

PCIe 4.0 標準是在 2017 年推出。與前一代相比,PCIe 4.0 將傳輸速率從 8 Gb/s 提高至 16 Gb/s,并與前幾代技術從軟件到時鐘架構再到機械接口充分兼容。PCIe 4.0 在規范中增加了計時器部分以擴展通道的范圍,并特別增加了系統的復雜性測試。

2019 年 5 月推出了 PCIe 5.0 規范,將傳輸速率提高一倍,達到 32 GT/s,同時保持低功耗和與前幾代的向后兼容性。PCIe 5.0 承諾通過 x16 配置達到 128 GB/s 的吞吐量,在數據中心可實現 400GE 的速度。PCIe 5.0 和 400GE 的速度共同支持人工智能(AI)、機器學習、游戲、視覺計算、存儲和網絡等應用。PCIe 5.0 使用 128b/130b 編碼方案,該方案在 PCIe 3.0 和兼容的 CEM 連接器中首次亮相。

2022 年 1 月推出了 PCIe 6.0 規范,它是第一個使用脈沖幅度調制 4 級(PAM4)信號編碼的 PCI Express 標準,使 PCIe 6.0 設備在保持相同信道帶寬的情況下能實現 PCIe 5.0 設備兩倍的吞吐量。PCIe 6.0 技術最高可達 64 GT/s,同時保持低功耗和向后兼容。PCIe 6.0 承諾通過 x16 配置達到 256GB/s 的吞吐量,在數據中心實現 800GE 速度。

評論