解決無線SoC系統設計中的 RF 耦合問題

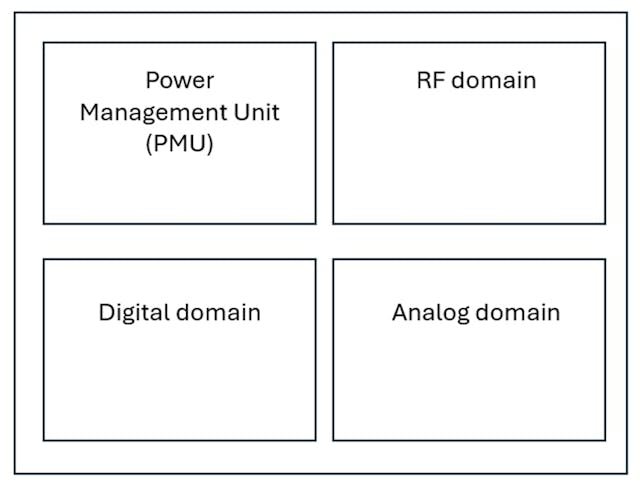

無線片上系統 (SoC) 設計需要在同一芯片上實現所有電路域。這使制造商能夠降低成本并支持完整性。另一方面,這些域之間的串擾可能會出現問題,并會降低整體性能。

本文引用地址:http://www.104case.com/article/202503/468376.htm電磁干擾 (EMI) 是由輻射射頻 (RF) 信號引起的。在系統設計中,可以使用各種技術來降低 EMI。例如,輻射射頻可以通過濾波和屏蔽來解決;然而,這并不能減輕片上 RF 耦合。

RF 耦合通道

RF 耦合是 RF 域和其他域之間串擾的一個例子(圖 1)。無線發射器需要產生 ~10 dBm 范圍內的輸出功率。功率放大器 (PA) 產生這些級別的功率,同時有時包含片上電感或變壓器。

由于電感的電磁輻射,一小部分發射功率可以耦合到 SoC 內的其他域。無論耦合分量是處于相同的發射頻率還是諧波,都會降低收發器的性能。當 integrated frequency synthesizer 的輸出信號頻譜變得雜散時,這一點就變得很明顯了。

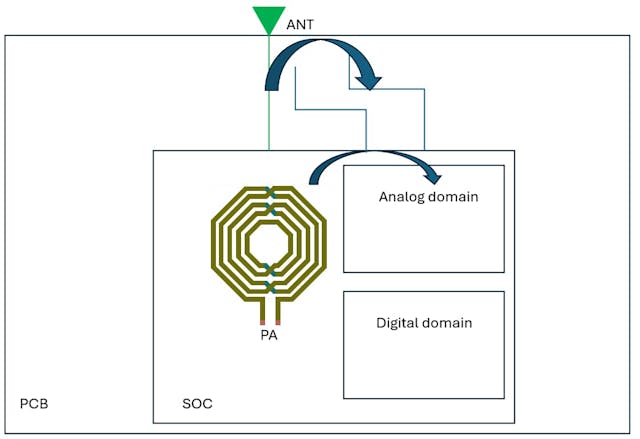

相同的耦合機制可能發生在 SoC 外部的 PCB 級別,天線將輻射并影響附近其他域的關鍵 PCB 布線(圖 2)。

減少 RF 耦合

通常,任何以任意頻率 (f1) 運行的區塊都被視為以另一個頻率 (f2) 運行的受害者區塊的攻擊者,反之亦然。當一個頻率是另一個頻率的精確整數倍時,可能會有異常。

攻擊者影響受害者的鏈接包括:

供應網絡

寄生電容耦合

寄生磁耦合

基板耦合

減少供應網絡耦合

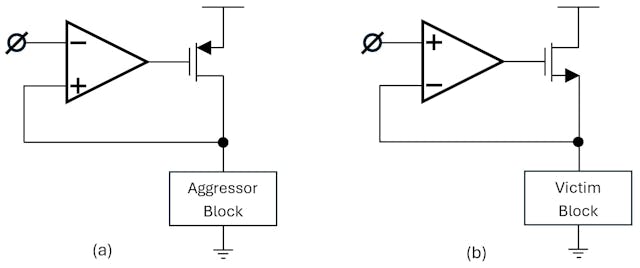

可以使用不同的穩壓器來減少通過電源網絡的耦合。考慮一個對 supply noise 不敏感的 aggressor block。這樣的模塊應由并聯穩壓器供電,1 如圖 3a 所示。反向電源抑制比 (PSRR) 是穩壓器輸出到其電源的信號傳輸函數,它很小。

同樣,對電源噪聲敏感的模塊對電源污染的影響可以忽略不計,應由串聯穩壓器1 供電(圖 3b)。正向 PSRR 是電源噪聲到穩壓器輸出的傳輸,在串聯穩壓器中很小。

減少電源網絡耦合的另一種常見方法是在每個模塊附近添加充足的電源去耦電容。但是,必須仔細執行此作,以最大限度地擴大去耦電容有效的頻率范圍。

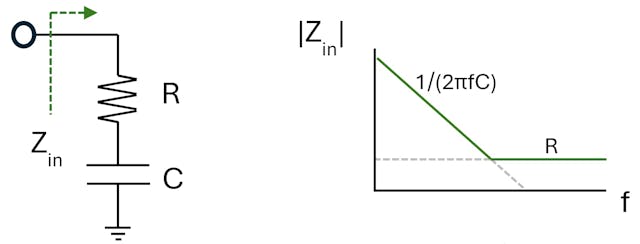

應將去耦電容布線的寄生電阻降至最低,以提高其品質因數。當 MOS 器件實現去耦電容器時,應盡量減少單元去耦電容器的長度,以減小其通道電阻。2 與寄生電阻串聯的電容器的阻抗在高頻時達到寄生電阻值飽和(圖 4)。

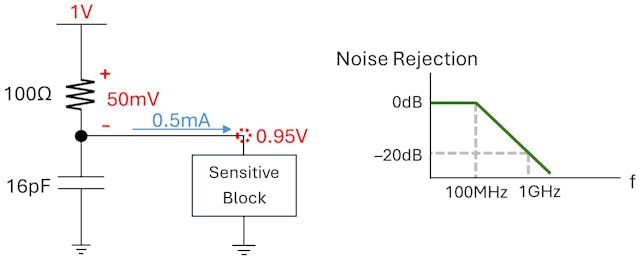

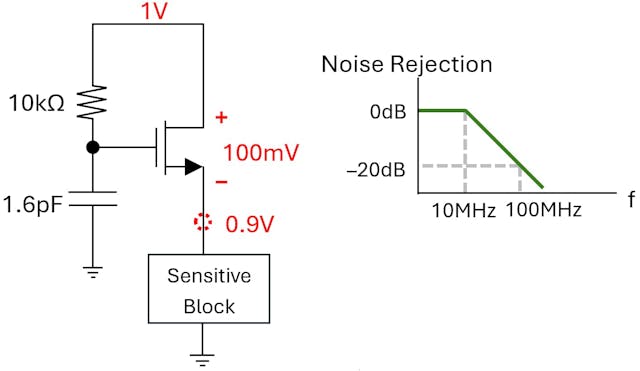

減輕電源網絡耦合的一種不常用的技術是添加無源或有源電源濾波器。1 設計工程師最初可能會拒絕這個想法,因為存在相關的電源電壓裕量損失。但是,考慮一個具有 1 V 電源且功耗為 0.5 mA 的模塊(圖 5)。

插入 100 Ω 電阻器可將電源裕量僅減少 50 mV。當添加的濾波器電容為 16 pF 時,1 GHz 的電源噪聲衰減 20 dB。對于利用原生 NMOS 器件的面積高效有源濾波器,也可以提出類似的論點(圖 6)。

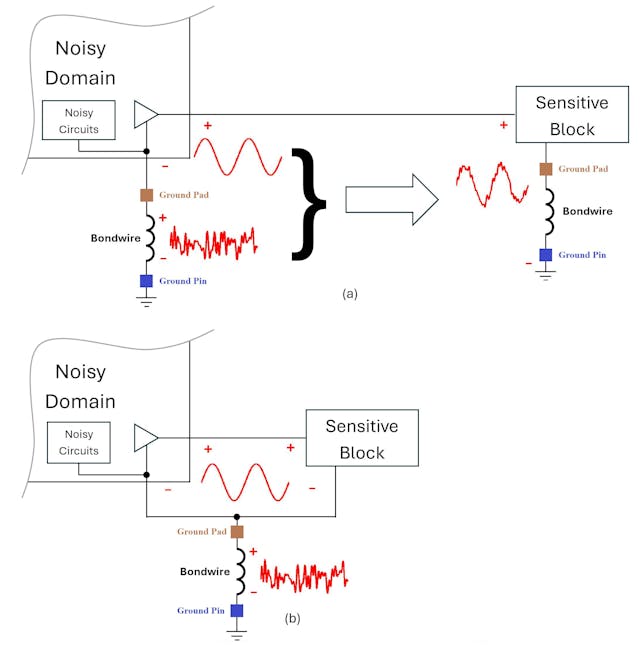

最后,將不同模塊的接地連接分開并將它們連接到不同的焊盤可能會導致嚴重的問題。3 分離會污染敏感塊,而不是隔離它們。這種違反直覺的機制如圖 7 所示。

減少寄生電容耦合

Parasitic capacive coupling 在 layout 級別處理。敏感和嘈雜的節點應使用其參考電源軌進行屏蔽。接地平面設計也可以提供幫助。

電容與導體之間的距離成反比;因此,增加 traces 之間的間距會有所幫助。

減少寄生磁耦合

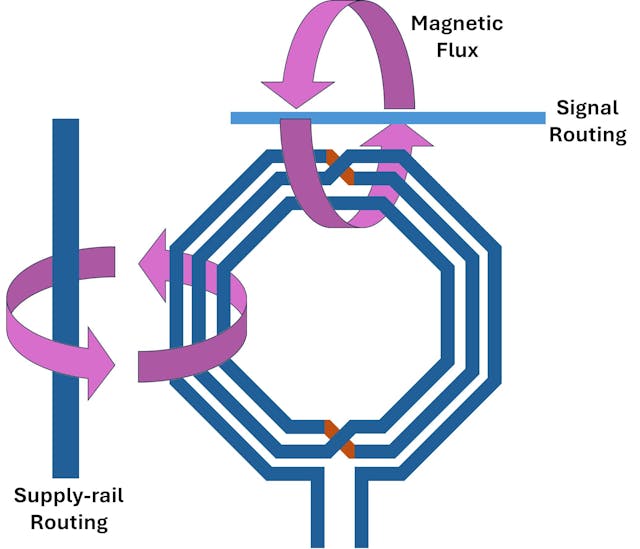

當長路線具有相同的方向時,它們可以相互磁耦合。當耦合發生在通往螺旋線圈一側的長平行路線之間時,這種效果更為明顯(圖 8)。當線圈同時承載高頻和大幅度的電流時,情況會變得更糟,就像功率放大器一樣。

為了減少這種磁耦合,敏感路線應盡可能遠離線圈和其他噪聲路線。此外,當布線彼此正交時,磁耦合會大幅減小。

減少基板耦合

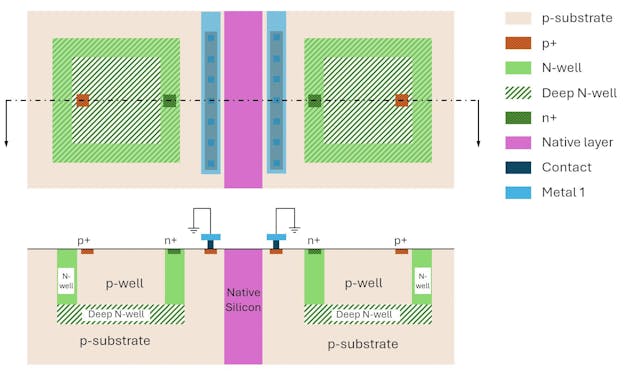

有時,噪聲耦合會通過襯底發生。為了克服這個問題,可以使用深 N 孔層將不同的電路隔離到井中。此外,應在隔離域之間添加高電阻率固有層,相鄰的體連接為不同的接地焊盤提供低阻抗路徑。這種技術如圖 9 所示。

最后,可以遵循一些準則來進一步減少噪聲從一個域到另一個域的傳輸。應盡可能使用差分信號進行域間連接。這最大限度地減少了參考節點噪聲的傳遞。此外,可以故意削弱一個域邊界的信號驅動器,以最大限度地減少所有信號到其他域的電傳輸。這種方法在處理 CMOS logic 信號(例如高速 clocks 和數字總線)時非常有效。

不要忽視耦合復位技術

無線 SoC 系統中的 RF 耦合可能是一個真正的問題,可能會降低整體性能。在設計 SoC 布局規劃并識別 aggressor 和 victim blocks 時,應特別注意。應實施耦合歸約技術以獲得所需的高性能。

評論