基于PC104(Plus)總線的數據接收存儲顯示系統設計

為了滿足PLX9054上電啟動速度的要求,其時鐘應由晶振直接提供。

系統上電后,PLX9054NFPGA發出復位命令

運算后可得到化簡結果![]() ,然后令

,然后令![]()

![]() ;之后再在FPGA內部將

;之后再在FPGA內部將![]() 、

、![]() 做與運算,可得到

做與運算,可得到![]() ,然后判斷

,然后判斷![]() ,若為低,則FPGA向PLX9054發出中斷

,若為低,則FPGA向PLX9054發出中斷![]() 。這樣就能保證兩片FIFO的數據根據優先級不斷向上發送。

。這樣就能保證兩片FIFO的數據根據優先級不斷向上發送。

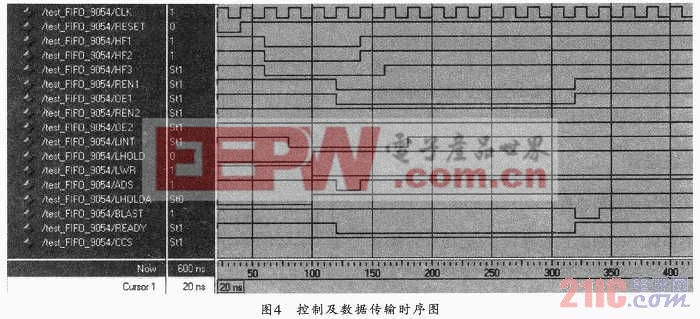

PLX9054響應中斷![]() 后,即可通過LHOLD申請對本地總線進行控制,FPGA則通過LHOLDA作出應答,進而由PLX9054獲得本地總線控制權并啟動DMA傳輸周期。FPGA收到讀信號

后,即可通過LHOLD申請對本地總線進行控制,FPGA則通過LHOLDA作出應答,進而由PLX9054獲得本地總線控制權并啟動DMA傳輸周期。FPGA收到讀信號![]() 和地址選通信號

和地址選通信號![]() 后,產生

后,產生![]() 信號,并在最后一個數據傳送信號

信號,并在最后一個數據傳送信號![]() 有效之前一直保持有效。在此期間,FPGA將根據圖3所示的運算邏輯結果,并按照優先級讀取相應FIFO的數據進行上傳。具體的控制及數據傳輸時序如圖4所示。

有效之前一直保持有效。在此期間,FPGA將根據圖3所示的運算邏輯結果,并按照優先級讀取相應FIFO的數據進行上傳。具體的控制及數據傳輸時序如圖4所示。

由圖4可見,當![]() 同時有效時,其FIFO1的優先級高于FIFO2,故可滿足設計要求。

同時有效時,其FIFO1的優先級高于FIFO2,故可滿足設計要求。

評論