基于USB和FPGA的隨機數發生器驗證平臺

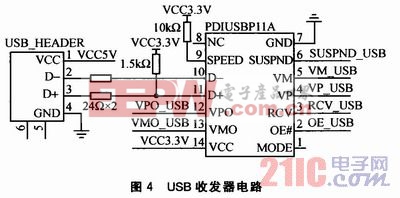

3.2 USB收發器電路

PDIUSBP11A芯片擁有14個可用引腳,其電路原理圖如圖4所示。本文引用地址:http://www.104case.com/article/202456.htm

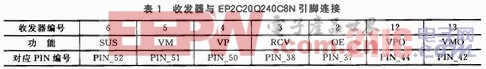

在本設計電路中,將PDIUSBP11A芯片的引腳1和引腳8懸空;引腳7和引腳14分別接地和3.3 V電壓;差分數據信號D+和D-引腳分別經一個阻值為24 Ω的電阻與USB接口的D+和D-相連,同時D+經上拉電阻與3.3 V電壓相連;引腳9經上拉電阻與3.3 V電壓相連,使USB保持在全速工作模式下;其他引腳與FPGA芯片相應的引腳相連接,具體連接方式如表1所列。

3.3 配置芯片及下載電路

Altera編程硬件主要包括MasterBlaster、ByteBlasterMV、ByterBlsterII、USB-Blaster和Ethernet Blaster下載電纜或Altera編程單元(APU)。

本文采用ByterBlsterII下載電纜,選用EPCS4配置芯片,設計實現了AS主動串行配置模式與JTAG下載模式相混合的下載配置電路。

本設計采用AS和JTAG兩種下載方式,可以通過JTAG方式對程序進行調試,同時通過QuartuslI軟件提供的一個可在線操作FPGA片上RAM內容的工具InSystem Memory Content Editor,用戶可以查看和修改RAM的內容。用戶可以預期對RAM中的內容進行修改,并通過該工具查看修改后的結果,兩者進行對比就可驗證程序運行是否正確。此外,在JTAG模式下可以利用jic文件驗證配置芯片是否已經損壞。

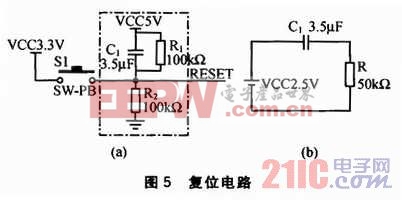

3.4 復位電路

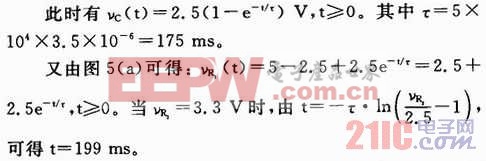

為使驗證系統初始化正確,當整個系統在電源上電時,必須處于復位狀態。一般應保持復位脈沖為高保持兩個機器周期以上,而系統晶體振蕩器達到穩定一般需要150 ms左右。為此,本文設計了基于RC器件的復位電路,如圖5所示。

其中,R1=R2=100 kΩ,C1=3.5μF,對于虛線中的電路,運用戴維南定理把系統上電后電路中除電容支路以外的部分進行化簡,得到的電路如圖5(b)所示。

由此可得,該復位電路能夠正常復位,保證系統正常工作。

3.5 時鐘電路

時鐘由晶振芯片提供,晶振芯片有無源晶振和有源晶振兩種。無源晶振為無極性元件,共有2個引腳,只有在時鐘電路工作控制下才能產生振蕩信號;有源晶振由石英晶體組成,此外還有晶體管和阻容元件,信號穩定,它共有4個引腳,常用的連接方式為:1腳懸空,2腳接地,3腳輸出,4腳接電壓。本設計采用ELV型號為SMD5*7的48MHz晶振。

評論