導航計算機系統中CPLD配置軟件串口更新研究

3 CPLD的JTAG接口編程的軟件設計

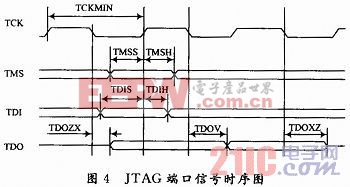

在硬件設計的基礎上,為實現通過DSP的GPIO口模擬JTAG信號時序邏輯來對CPLD進行軟件更新,需嚴格按照JTAG標準中的端口信號時序要求。對于本文所用的CPLD器件,其JTAG端口信號時序關系如圖4所示。本文引用地址:http://www.104case.com/article/202351.htm

由圖4可見,對于JTAG口時序邏輯需考慮如下3項內容:

(1)JTAG接口要求一個最小時鐘周期TCKMIN。

(2)JTAG接口在TCK的上升沿采樣TMS和TDI信號。因此在TCK上升沿之前,TMS和TDI要具有最小分別為TMSS和TDIS的建立時間,同時在TCK下降沿之后要保持最小分別為TMSH和TDIH長的時間。

(3)在TCK的下降沿,JTAT接口輸出新的TDO值,并保持至少TDOV長的時間。

本文所用CPLD的JTAG端口時序參數要求如表1所示。

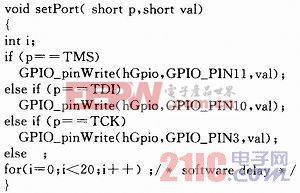

在本文設計的導航計算機系統中,DSP的工作主頻為200 MHz,利用TI公司提供的庫函數,由該DSP的GPIO口模擬的時鐘頻率最大不超過3 MHz,可以滿足表中TCKMIN參數對應的最大10 MHz的要求。對于建立和保持時間等參數要求,可通過軟件延時或定時器實現。由于在本系統的應用中,DSP在上電期間專注于CPLD的軟件更新,所以本文將采用軟件延時來實現這些參數要求,設計的JTAG口信號電平驅動函數模塊代碼如下:

利用上述代碼,模擬實現的JTAG時鐘信號頻率為367.6 kHz。

評論