導(dǎo)航計(jì)算機(jī)系統(tǒng)中CPLD配置軟件串口更新研究

JTAG標(biāo)準(zhǔn)定義了4個(gè)基本單元:測試訪問端口TAP(Test Access Port)、數(shù)據(jù)寄存器、指令寄存器和TAP控制器。TAP端口包含了4個(gè)JTAG信號:測試時(shí)鐘輸入引腳TCK,測試數(shù)據(jù)輸入引腳TDI,測試數(shù)據(jù)輸出引腳TDO和測試模式選擇引腳TMS。數(shù)據(jù)寄存器主要包含2種:BYPASS寄存器和BSR(Botlndary Scan Register)寄存器,其中BSR由BSC(Botmdary Scan Cell)串聯(lián)而成,正是通過BSC掃描鏈電路,來自于TDI上的CPLD配置信息便可移入到芯片內(nèi)部,從而實(shí)現(xiàn)對器件的擦除與編程功能。TAP控制器其實(shí)是一個(gè)包含16個(gè)狀態(tài)的狀態(tài)機(jī),它控制著測試訪問口、指令寄存器和數(shù)據(jù)寄存器。TAP控制器狀態(tài)轉(zhuǎn)換圖如圖2所示。

TAP控制器的狀態(tài)由TMS和TCK兩信號控制。當(dāng)需要將TDI上的數(shù)據(jù)移到指令寄存器中時(shí),可使TAP控制器進(jìn)入Shift-IR狀態(tài);當(dāng)需要將TDI上的數(shù)據(jù)移到數(shù)據(jù)寄存器中時(shí),可使其進(jìn)入Shift-DR狀態(tài)。通過TAP控制器的狀態(tài)轉(zhuǎn)換,可將CPLD的配置信息移入到其內(nèi)部邏輯中。

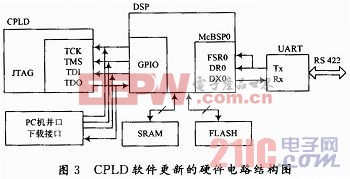

在基于PC的編程方法中,CPLD的配置信息文件存儲在PC里,在PC中運(yùn)行的下載軟件不斷讀取器件的配置信息,并通過其并行接口模擬JTAG測試端口的時(shí)序和邏輯,從而實(shí)現(xiàn)其軟件更新和下載。本文將采用導(dǎo)航計(jì)算機(jī)系統(tǒng)中的DSP來實(shí)現(xiàn)這種編程方法:CPLD的配置文件通過DSP的UART串行口發(fā)送給導(dǎo)航計(jì)算機(jī)系統(tǒng),然后由DSP解析并執(zhí)行配置文件中的指令,通過DSP的I/O口模擬JTAG端口信號行為,來實(shí)現(xiàn)對CPLD器件軟件更新的功能。基于這種方案可以實(shí)現(xiàn)采用普通的串行口方便地對CPLD進(jìn)行遠(yuǎn)端編程和更新。

2 CPLD的JTAG接口編程的硬件設(shè)計(jì)

為實(shí)現(xiàn)本文提出的導(dǎo)航計(jì)算機(jī)系統(tǒng)中基于DSP的CPLD器件軟件更新串行方案,首先需要在硬件方面解決如下3個(gè)問題:

(1)導(dǎo)航計(jì)算機(jī)系統(tǒng)所用DSP至少要有4個(gè)空余的I/O口,分別用于模擬CPLD的4個(gè)JTAG信號時(shí)序信號。

(2)導(dǎo)航計(jì)算機(jī)系統(tǒng)必須包含支持一個(gè)UART通信接口,用于接收CPLD的配置文件。此UART接口不能由CPLD參與控制,以避免CPLD某次編程失敗后,該UART通信口不再可用的問題。

(3)導(dǎo)航計(jì)算機(jī)系統(tǒng)應(yīng)保證足夠的CPLD配置信息文件需要的存儲空間。

本文所用DSP為TI公司的TMS320C6713B芯片,該款DSP支持16個(gè)通用輸入輸出口(GPIO)。在本導(dǎo)航計(jì)算機(jī)系統(tǒng)中,有12個(gè)GPIO口已被占用,多余的4個(gè)GPIO口可用來連接CPLD的4個(gè)JTAG信號引腳。

TMS320C6713B本身并不支持包含UART通信接口,其片上外設(shè)中包含2個(gè)多通道緩沖串行接口(McBSP),McBSP接口支持全雙工串行通信,只是收發(fā)數(shù)據(jù)需要獨(dú)立的收發(fā)幀同步信號。根據(jù)TI公司提供的應(yīng)用技術(shù)報(bào)告,經(jīng)過對軟件或硬件進(jìn)行改造設(shè)計(jì),McBSP接口可以支持UART通信標(biāo)準(zhǔn)。軟件修改方法是通過將McBSP接口配置成通用I/O接口來模擬UART時(shí)序;硬件修改方法是將McBSP接口配置在串行口模式,McBSP接口中接收幀同步信號FSR來自于UART的發(fā)送數(shù)據(jù)線Tx,在檢測到Tx的下跳沿時(shí),McBSP內(nèi)部開始采樣接收數(shù)據(jù),之后Tx的下跳沿將被忽略直至下一個(gè)字節(jié)的起始位再次觸發(fā)內(nèi)部幀接收新的數(shù)據(jù);發(fā)送幀同步信號FSR由McBSP電路在發(fā)送UART數(shù)據(jù)起始位時(shí)產(chǎn)生。本文采用硬件修改和過采樣軟件措施,將一個(gè)多通道緩沖串行接口McBSP0設(shè)計(jì)成了支持UART通信標(biāo)準(zhǔn)的接口。

本導(dǎo)航計(jì)算機(jī)系統(tǒng)使用的CPLD配置信息文件是串行矢量格式(SVF),可以在Xilinx軟件開發(fā)平臺ISE上生成。SVF是一種用來描述IEEE 1149.1(JTAG)總線操作的規(guī)范,包含了編程需要的指令和數(shù)據(jù),描述了TAP測試訪問端口狀態(tài)圖中各狀態(tài)之間的掃描操作過程和行為。由于SVF文件是ASCII格式,所以占用的存儲空間比較大,可以將其轉(zhuǎn)換為一種更簡潔和緊湊的二進(jìn)制格式:XSVF文件。對于本系統(tǒng)所用CPLD器件而言,僅對其進(jìn)行編程操作時(shí),XSVF文件大小為129 720 B,加上擦除和校驗(yàn)操作后,XSVF文件大小為259 533 B。根據(jù)上述分析,本文設(shè)計(jì)的嵌入式導(dǎo)航計(jì)算機(jī)系統(tǒng)中通過UART接口對CPLD器件進(jìn)行在系統(tǒng)軟件更新的硬件電路結(jié)構(gòu)如圖3所示。本文引用地址:http://www.104case.com/article/202351.htm

圖3中,UART通信口由DSP片上多通道緩沖串行口McBSP0實(shí)現(xiàn)。為了存儲通過UART口接收到的包含CPLD配置信息的XSVF文件,本系統(tǒng)外擴(kuò)了一片512 kB的SRAM。FLASH芯片用來存儲導(dǎo)航計(jì)算機(jī)系統(tǒng)升級固件和應(yīng)用程序。CPLD的JTAG口直接與DSP空閑的4個(gè)GPIO口相連,為了提高CPLD器件編程的靈活性,在本系統(tǒng)中保留了連接PC機(jī)并口的CPLD程序下載接口。

評論