用FPGA做正交解碼

FPGA非常適合用邏輯來實現正交解碼的功能。

本文引用地址:http://www.104case.com/article/202312/454241.htm什么是正交信號?

正交信號是兩個相位差為90度的信號。它們在機械系統中用于確定軸的運動(或旋轉)。

這是一個向前移動幾步的軸。

如果對脈沖計數,則可以說軸移動了3步。

如果計算邊緣,則可以說軸移動了12步。這就是我們在此頁面上所做的。

現在,軸向后移動了相同的量。

因此,想法是通過查看邊緣和水平,我們可以確定運動的方向和距離。

這是一個示例,其中軸向前移動10步,然后向后移動7步。

它們在哪里使用?

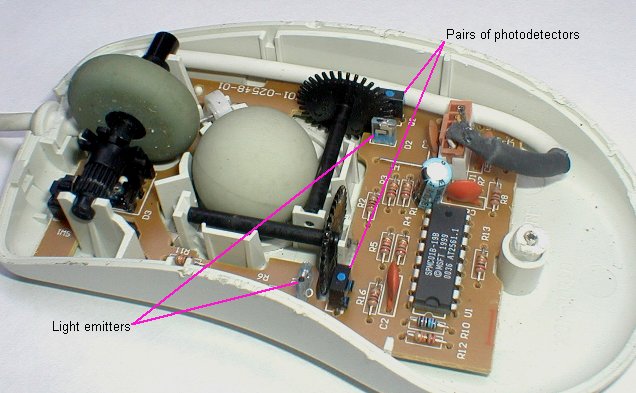

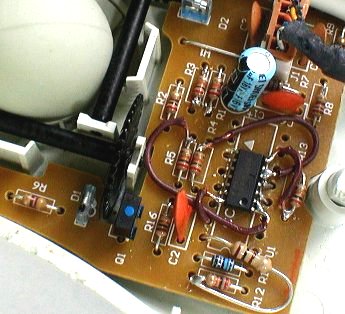

如果您打開機械鼠標,則會看到以下內容。

有兩個光學正交編碼器,每個編碼器由開槽輪,光發射器和一對光電探測器制成。

鼠標包括負責正交解碼和串行/ PS2接口的IC。由于創建正交解碼器(在FPGA中)比串行或PS2接口要容易得多,因此我們修改了鼠標,并用四緩沖器施密特觸發器輸入IC替換了原始IC。

我們使用CD4093,每個NAND門的輸入連接在一起形成反相器。

現在,鼠標輸出正交編碼信號!

正交解碼器

我們要實現一個根據正交信號遞增或遞減的計數器。我們假設有一個比正交信號快的“過采樣時鐘”(在此頁面中稱為“ clk”)。

控制計數器的硬件電路非常簡單。

這是軸向前移動的波形,計數器會遞增。

該電路有時稱為“ 4x解碼器”,因為它會計算正交輸入的所有躍遷。

在verilog HDL中,這為我們提供了:

module quad(clk, quadA, quadB, count); input clk, quadA, quadB; output [7:0] count; reg quadA_delayed, quadB_delayed; always @(posedge clk) quadA_delayed <= quadA; always @(posedge clk) quadB_delayed <= quadB; wire count_enable = quadA ^ quadA_delayed ^ quadB ^ quadB_delayed; wire count_direction = quadA ^ quadB_delayed; reg [7:0] count; always @(posedge clk)begin if(count_enable) begin if(count_direction) count<=count+1; else count<=count-1; endend endmodule

實際生活中的電路

先前的電路假定“ quadX”輸入與“ clk”時鐘同步。在大多數情況下,“ quadX”信號與FPGA時鐘不同步。經典解決方案是每個輸入使用2個額外的D觸發器,以避免將亞穩性引入計數器。

module quad(clk, quadA, quadB, count);

input clk, quadA, quadB;

output [7:0] count;

reg [2:0] quadA_delayed, quadB_delayed;

always @(posedge clk) quadA_delayed <= {quadA_delayed[1:0], quadA};

always @(posedge clk) quadB_delayed <= {quadB_delayed[1:0], quadB};

wire count_enable = quadA_delayed[1] ^ quadA_delayed[2] ^ quadB_delayed[1] ^ quadB_delayed[2];

wire count_direction = quadA_delayed[1] ^ quadB_delayed[2];

reg [7:0] count;

always @(posedge clk)begin

if(count_enable)

begin

if(count_direction) count<=count+1;

else count<=count-1;

endend endmodule總之,創建正交解碼器/計數器所需的硬件很少。FPGA可以容納多個軸,因此可以同時跟蹤多個軸。

評論