基于旋轉編碼器的調節系統設計

實驗任務

實驗目的

在基礎數字電路實驗部分我們已經掌握了FPGA驅動獨立顯示數碼管的原理及方法,本實驗主要學習旋轉編碼器的驅動原理,最后完成旋轉調節系統總體設計。

本文引用地址:http://www.104case.com/article/202312/453766.htm設計框圖

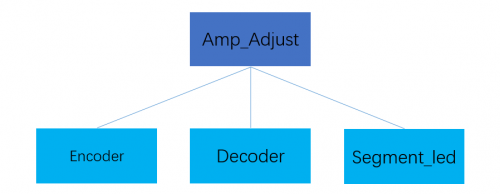

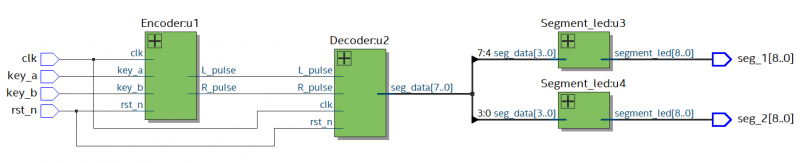

根據前面的實驗解析我們可以得知,該設計可以拆分成三個功能模塊實現,

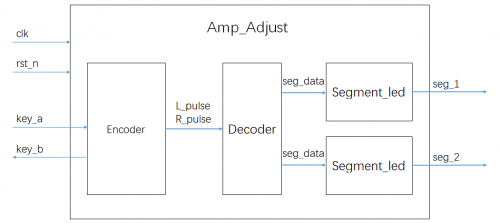

頂層模塊Amp_Adjust通過實例化三個子模塊并將對應的信號連接,最終實現旋轉調節系統的總體設計。

實驗原理

旋轉編碼器介紹

旋轉編碼器(rotary encoder)也稱為軸編碼器,是將旋轉位置或旋轉量轉換成模擬或數字信號的機電設備。旋轉編碼器用在許多需要精確旋轉位置及速度的場合,如工業控制、機器人技術、專用鏡頭、電腦輸入設備(如鼠標及軌跡球)等。 旋轉編碼器以碼盤刻孔方式不同分為:絕對式和增量式兩類。

STEP BaseBoard V3.0底板上集成的旋轉編碼器就是機械增量式的。

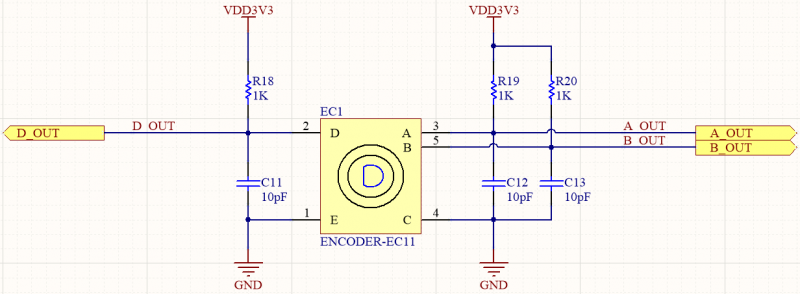

旋轉編碼器連接

旋轉編碼器驅動設計

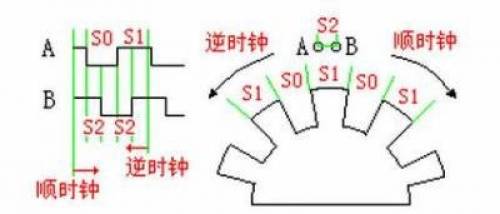

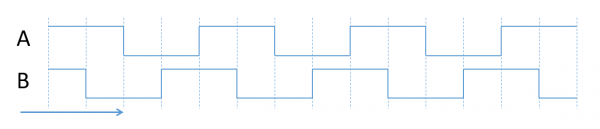

上圖是機械增量式旋轉編碼器的原理示意圖,中間圓形齒輪連接到旋轉編碼器的公共端4管腳,STEP BaseBoard V3.0底板上我們將之接地處理,A、B兩個觸點連接到旋轉編碼器的A、B相輸出端3、5管腳,當進行旋轉操作時,A、B觸點會先后接觸和錯開圓形齒輪,從而導致A、B相輸出信號產生相位不同的脈沖信號:

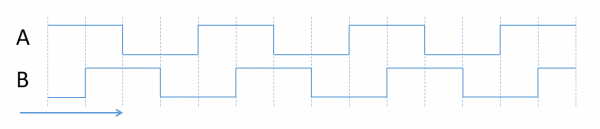

根據時序圖可以看出旋轉編碼器順時針或逆時針旋轉時,A相信號超前或滯后B相信號,FPGA接收到旋轉編碼器的A、B信號時,可以根據A、B的狀態組合判定編碼器的旋轉方向。 程序設計中我們可以對A、B信號檢測,檢測A信號的邊沿及B信號的狀態,

以上就是我們旋轉編碼器驅動設計的總體思路,下面我們就通過編程來實現它。

前面電路連接部分我們使用了兩個電容對A、B信號作去抖處理,可以起到一定的效果,為了驅動更加穩定,我們在程序中再簡單處理一下,先對系統時鐘分頻得到2KHz的時鐘,然后在2KHz時鐘的節拍下對A、B信號采樣,三級鎖存消除亞穩態

對A信號采樣程序實現如下(對B信號一樣):

reg key_a_r,key_a_r1,key_a_r2;//消除亞穩態always@(posedge clk_500us) begin key_a_r <= key_a; key_a_r1 <= key_a_r; key_a_r2 <= key_a_r1;end

然后簡單去抖處理程序實現如下(對B信號一樣):

reg A_state;//簡單去抖動處理

always@(key_a_r1 or key_a_r2) begin

case({key_a_r1,key_a_r2})

2'b11: A_state <= 1'b1;

2'b00: A_state <= 1'b0;

default: A_state <= A_state;

endcaseend檢測A信號的邊沿程序實現如下:

reg A_state_r,A_state_r1;//對A_state信號進行邊沿檢測 always@(posedge clk) begin A_state_r <= A_state; A_state_r1 <= A_state_r; end wire A_pos = (!A_state_r1) && A_state_r; wire A_neg = A_state_r1 && (!A_state_r);

最后根據A信號邊沿與B信號的狀態組合判定旋轉的信息,

逆時針旋轉脈沖輸出程序實現如下:

//當A的上升沿伴隨B的高電平或當A的下降沿伴隨B的低電平 為向左旋轉 always@(posedge clk or negedge rst_n) begin if(!rst_n) L_pulse <= 1'b0; else if((A_pos&&B_state)||(A_neg&&(!B_state))) L_pulse <= 1'b1; else L_pulse <= 1'b0; end //當A的上升沿伴隨B的低電平或當A的下降沿伴隨B的高電平 為向右旋轉 always@(posedge clk or negedge rst_n) begin if(!rst_n) R_pulse <= 1'b0; else if((A_pos&&(!B_state))||(A_neg&&B_state)) R_pulse <= 1'b1; else R_pulse <= 1'b0; end

所以通過上面程序最終實現了左旋右旋的脈沖輸出,脈沖的脈寬等于系統時鐘的周期。

系統總體實現

回顧旋轉調節系統設計框架,剛剛我們已經學習完成了旋轉編碼器的驅動設計,在基礎數字電路實驗部分我們已經掌握了FPGA驅動獨立顯示數碼管的原理及方法, 模塊通過一個4位的輸入傳遞要顯示的數值,通過9位的輸出控制數碼管顯示該數值,這里我們不再重復,還需要設計一個模塊,通過旋轉編碼器模塊脈沖輸出控制變量在0~99范圍內加減變化。

關于BCD碼在基礎數字電路實驗部分已經接觸過,BCD碼(Binarycoded Decimal),是用4位二進制碼的組合代表十進制數的碼制方法,這樣顯示更符合人的閱讀習慣,所以BCD數值變化要求滿9進1。

脈沖控制變量在0~99范圍變化,左旋減,右旋加,程序實現如下

//key_pulse transfer to seg_dataalways@(posedge clk or negedge rst_n) begin if(!rst_n) begin seg_data <= 8'h50; end else begin if(L_pulse) begin if(seg_data[3:0]==4'd0) begin seg_data[3:0] <= 4'd9; if(seg_data[7:4]==4'd0) seg_data[7:4] <= 4'd9; else seg_data[7:4] <= seg_data[7:4] - 1'b1; end else seg_data[3:0] <= seg_data[3:0] - 1'b1; end else if(R_pulse) begin if(seg_data[3:0]==4'd9) begin seg_data[3:0] <= 4'd0; if(seg_data[7:4]==4'd9) seg_data[7:4] <= 4'd0; else seg_data[7:4] <= seg_data[7:4] + 1'b1; end else seg_data[3:0] <= seg_data[3:0] + 1'b1; end else begin seg_data <= seg_data; end end end

綜合后的設計框圖如下:

實驗步驟

實驗現象

將程序下載到實驗平臺,核心板數碼管顯示50,旋轉編碼器左旋(逆時針)數值減小,旋轉編碼器右旋(順時針)數值增加,旋轉編碼器旋轉時有頓挫感,每次頓挫數值變化1。

評論