Lattice MXO2: LED流水燈

在時鐘分頻實驗中我們練習了如何處理時鐘,接下來我們要學習如何利用時鐘來完成時序邏輯。

本文引用地址:http://www.104case.com/article/202311/452377.htm硬件說明

流水燈實現是很常見的一個實驗,雖然邏輯比較簡單,但是里面也包含了實現時序邏輯的基本思想。要用FPGA實現流水燈有很多種方法,在這里我們會用兩種不同的方法實現。

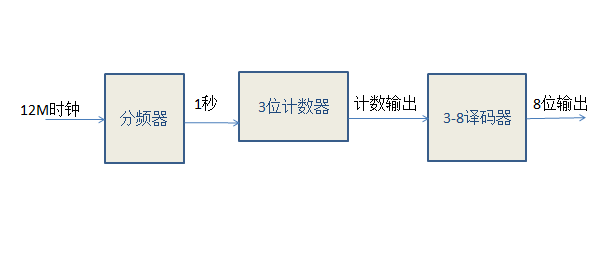

1,模塊化設計:在之前的實驗中我們做了3-8譯碼器和時鐘分頻,如果把這兩個結合起來,我們就能搭建一個自動操作的流水LED顯示。框圖如下:

2,循環賦值:這是一種很簡潔的實現流水燈效果邏輯,就是定義一個8位的變量,在每個時鐘上升沿將最低位賦值給最高位,其他位右移一位,這就實現了循環賦值。這8位輸出到LED就能實現流水燈。

Verilog代碼

模塊化設計是用硬件描述語言進行數字電路設計的精髓,代碼可重復利用。而且模塊化的設計使得程序的結構也很清晰。這里我們首先看看流水燈的模塊化設計。利用了之前的3-8譯碼器和分頻器,你需要把這兩個程序也拷貝到一個工程。

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : flashled.v // Module name : flashled // Author : STEP // Description : segment initial // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2017/03/02 |Initial ver // -------------------------------------------------------------------- // Module Function:流水燈的模塊化設計 module flashled (clk,rst,led); input clk,rst; output [7:0] led; reg [2:0] cnt ; //定義了一個3位的計數器,輸出可以作為3-8譯碼器的輸入 wire clk1h; //定義一個中間變量,表示分頻得到的時鐘,用作計數器的觸發 //例化module decode38,相當于調用 decode38 u1 ( .sw(cnt), //例化的輸入端口連接到cnt,輸出端口連接到led .led(led) ); //例化分頻器模塊,產生一個1Hz時鐘信號 divide #(.WIDTH(32),.N(12000000)) u2 ( //傳遞參數 .clk(clk), .rst_n(rst), //例化的端口信號都連接到定義好的信號 .clkout(clk1h) ); //1Hz時鐘上升沿觸發計數器,循環計數 always @(posedge clk1h or negedge rst) if (!rst) cnt <= 0; else cnt <= cnt +1; endmodule

模塊化設計結構清晰,verilog語言是很靈活的。對于流水燈還有一種很簡潔的實現方法。

// ********************************************************************

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// ********************************************************************

// File name : flashled.v

// Module name : flashled

// Author : STEP

// Description : segment initial

// Web : www.stepfpga.com

//

// --------------------------------------------------------------------

// Code Revision History :

// --------------------------------------------------------------------

// Version: |Mod. Date: |Changes Made:

// V1.0 |2017/03/02 |Initial ver

// --------------------------------------------------------------------

// Module Function:流水燈的模塊化設計

module flashled (clk,rst,led);

input clk,rst;

output [7:0] led;

wire clk1h; //定義一個中間變量,表示分頻得到的時鐘,用作計數器的觸發

//例化分頻器模塊,產生一個1Hz時鐘信號

divide #(.WIDTH(32),.N(12000000)) u2 ( //傳遞參數

.clk(clk),

.rst_n(rst), //例化的端口信號都連接到定義好的信號

.clkout(clk1h)

); //1Hz時鐘上升沿觸發循環賦值

reg [7:0] led;

always@(posedge clk1h or negedge rst)

begin

if(!rst)

led <= 8'b11111110; // <=為非阻塞賦值

else

led <= {led[0],led[7:1]};

//當時鐘上升沿來一次,執行一次賦值,賦值內容是led[0]與led[7:1]重新拼接成8位賦給led,相當于循環右移

end

endmodule引腳分配

按照下面表格定義輸入輸出信號

| 信號 | 引腳 | 信號 | 引腳 |

|---|---|---|---|

| clk | C1 | led[3] | M11 |

| rst | L14 | led[4] | P11 |

| led[0] | N13 | led[5] | N10 |

| led[1] | M12 | led[6] | N9 |

| led[2] | P12 | led[7] | p9 |

配置好以后編譯下載程序。可以調整例化分頻器時傳遞的參數來調整流水燈的速度。

小結

掌握了verilog里面例化module的用法,采用模塊化設計程序。模塊化設計是非常重要的FPGA設計思想。在下一節我們會學習按鍵的另外用法按鍵消抖。

評論