高速電路板設計的電路板層堆棧注意事項

只有使用正確的PCB疊層進行構建,高速設計才能成功運行。您的疊層必須正確布置電源和接地層,為信號分配足夠的層,并且所有材料組和銅選擇均能以適當的規(guī)模和成本制造。如果設計人員能夠獲得正確的疊層,那么在確保信號完整性的情況下布線就會容易得多,并且可以抑制或防止許多更簡單的EMI問題。

本文引用地址:http://www.104case.com/article/202309/450360.htm只有使用正確的PCB疊層進行構建,高速設計才能成功運行。您的疊層必須正確布置電源和接地層,為信號分配足夠的層,并且所有材料組和銅選擇均能以適當的規(guī)模和成本制造。如果設計人員能夠獲得正確的疊層,那么在確保信號完整性的情況下布線就會容易得多,并且可以抑制或防止許多更簡單的EMI問題。

為了幫助設計人員更快地設計和構建支持所需布線和信號完整性的高速疊層,我們?yōu)椴煌悇e的高速疊層編譯了重要資源。

低層數疊層

更簡單的高速PCB將從4層電路板開始。我堅定認為,2層電路板不應該用于支持阻抗控制的高速數字接口的設計,因為其無法保證信號完整性或噪聲控制。任何設計專業(yè)人士均認同這一點。

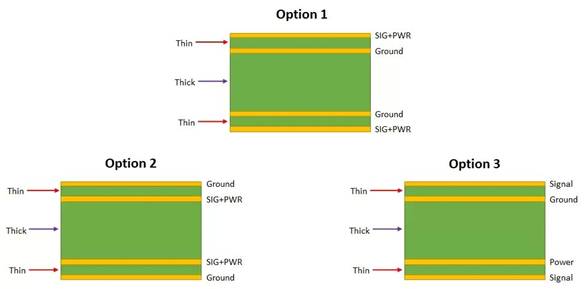

可以支持高速信號的三種主要類型的4層PCB疊層如下所示。在這些疊層中,選項1可以說是最佳選擇,因為它提供了最大的布線靈活性,并且可以用作雙面電路板。選項2也可用于雙面放置,但它限制了信號的布線位置,因為內層可能存在串擾。選項3適用于有高功率需求,但只能在一層上布線高速信號;被動元件或機械元件仍可以放置在背面層上。

· 詳細了解雙面PCB的最佳4層疊層選項

可支持高速布線的4層PCB疊層示例

如果需要將低速信號放入內層等更高的信號數,則下一步是將選項1擴展到更高的層數。這將從一個6層疊層開始,其中一個專用電源層和一個信號層被添加到上面選項1所示的疊層中。此疊層之所以有用,有兩個原因:

· 表層適用于受控阻抗高速接口

· 內層可以支持大多數較慢的接口或控制信號

· 電源層可以分成多個大電源軌以支持不同的核心電壓電平

可以使用相同的步驟將疊層擴展到具有高速信號的8層或更多層;下一節(jié)將討論這種類型的PCB疊層。

· 詳細了解可支持高速PCB的6層PCB疊層

適中層數

在某些時候,電路板疊層會變得非常厚,以至于PCB的總厚度會大于標準值。就制造方面而言,這不是問題;標準層壓過程可以處理超出標準厚度值并達到數毫米厚度的板。如果您的目標是薄板,那么您將需要更薄的層;選項是增強型PTFE層壓板(將在下文討論)或直接轉向HDI過程。

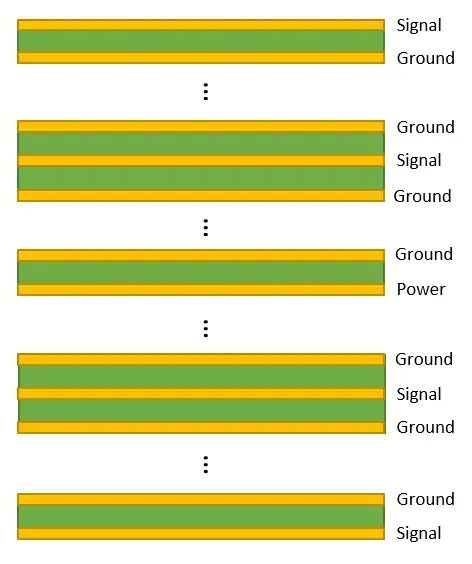

適中層數的電路板(約8層以上)往往會將多個平面層分配給電源,并具有額外的信號層。對于適中層數的電路板,很少會有簡單的指南可以幫助抑制EMI并確保電源完整性:

· 只要信號不參考該平面層,就可以將電源層分成多個軌道

· 如果有多個電源平面,不要將電源平面堆疊在相鄰的層上,而是用一個GND層將其分開

· 將快速信號放在兩個GND平面之間的內層上,不要將其參考有任何拆分的電源平面

· 僅將表層用于快速微帶線,可以使用一些電源布線(如有需要),也可以使用一些GND灌注(如有需要)

這些指南可能會導致您在設計中添加幾個額外的層,但優(yōu)勢是噪聲控制、電源完整性和信號完整性要好得多。

將層分組到更高層數的策略

更多高級疊層

在高速PCB設計的背景下,“更先進”的想法可能意味著很多事情。在高速數字設計中,它在層選擇和排列方面可能有兩種可能的含義:

· 支持HDI布線的薄層

· 層數過高會迫使使用薄層

· 在多層的細間距BGA中進行布線(但不一定要用HDI)

換句話說,您可以擁有非常薄的信號層(例如4密耳)和低層數的玻璃增強型FR4,或者您可以擁有非常高的層數,從而迫使采用薄層和可能的替代材料。

這些PCB高速疊層設計的考量重點是元件所需的線寬和可制造性,而不僅僅是疊層的Dk和Df值。在某些情況下,信號層需要使用低Dk、低Df的層壓板,但并不只是因為損耗較低。在這些設計中,可制造性和信號完整性至高無上,薄層壓板可以解決具有高層數和/或薄信號層的高速疊層中的許多挑戰(zhàn)。如今,較薄電路板的主要選擇是增強型PTFE層壓板,其厚度可低于4密耳,從而無需轉向最先進的工藝或HDI過程。

評論