高精度混合集成電路直方圖測試討論*

*參與項目:陜西省重點產業(yè)創(chuàng)新鏈(群)-工業(yè)領域:高精度模擬與混合信號集成電路頻譜測試技術研究,受理編號:S2020-YF-ZDCXL-ZDLGY-0297

本文引用地址:http://www.104case.com/article/202306/447223.htm本文主要通過測試機臺模擬步進DAC,并且步進DAC 比待測器件高出4 bit,這樣ATE 測試機臺能夠將一個待測ADC 的一個轉換碼平均分割16 步進,并且轉換16 次。從而待測器件理想情況下每位的轉換碼都會重復出現(xiàn)16 次。直方圖測試就是通過統(tǒng)計每個碼點出現(xiàn)的次數(shù),與理想情況下碼點出現(xiàn)的次數(shù)來計算靜態(tài)參數(shù)值。

1 直方圖法參數(shù)計算

零點誤差( EZ ) 與增益誤差( EG )

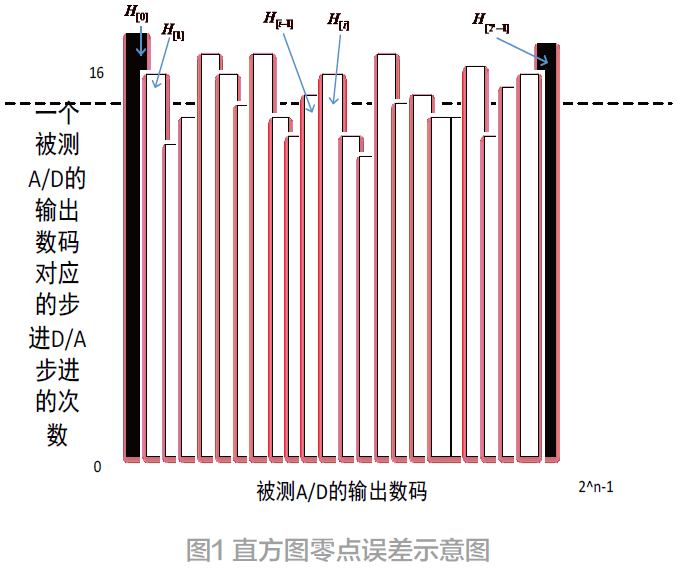

圖1 以柱狀圖表示每個轉換碼點的次數(shù)。假設被測器件是n 位,ATE 測試機臺內部的DAC 是n+4 位。

在計算時,先利用ATE 測試機臺采集每個轉換碼i=1到i=2n?2,重復出現(xiàn)的次數(shù)。我們記錄轉換次數(shù)為H。假設每一位轉換碼在ATE 出現(xiàn)的次數(shù)為H(i )。有![]()

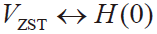

在直方圖測試法下有:

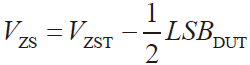

VZST是數(shù)字輸出轉換碼從00..00 到00..01 時的模擬值。

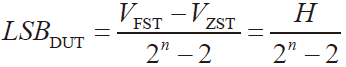

VFST是使數(shù)字輸出轉換碼從11..10 到11..11 的模擬值。根據(jù)待測ADC 靜態(tài)參數(shù)LSBDOUT 準計算公式

ADC的零點誤差:

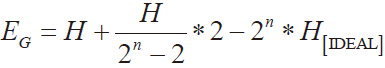

同理增益誤差EG:

其中, H[IDEAL] 直方圖測試法中理想狀態(tài)ADC 的輸出數(shù)碼對應的機臺步進的次數(shù)。

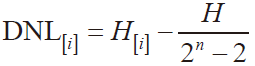

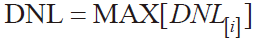

1.2 差分非線性誤差 (DNL) 與微分非線性誤差 (INL)

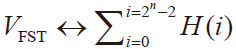

根據(jù)VFST、VZST的定義,在直方圖測試法下有:

由式(4)(5)相減可以得出

根據(jù)A/D 靜態(tài)參數(shù)LSBDUT準計算公式

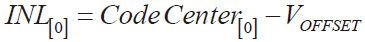

Code Center[i ]為轉換碼中心是指當數(shù)字輸出為i時,其1/2 碼寬對應的模擬輸入值。

Code Center[0]是數(shù)字轉換輸出i = 0的,Code Center[0]就是VZS。

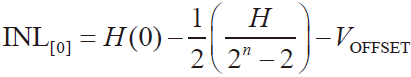

零點的INL值有

理想的零點INL[0]=0

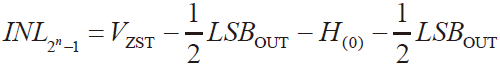

當i = 2n?1(最大值)時,可得

![]()

根據(jù)ADC靜態(tài)參數(shù)傳統(tǒng)計算公式得

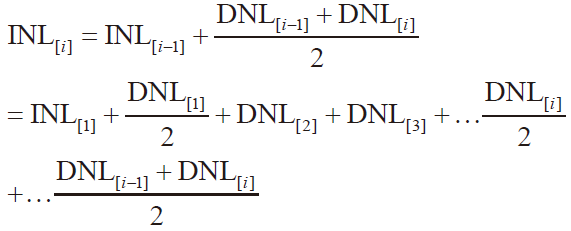

當0 < i < 2n ?1時,根據(jù) ADC 靜態(tài)參數(shù)標準計算公式得

可得

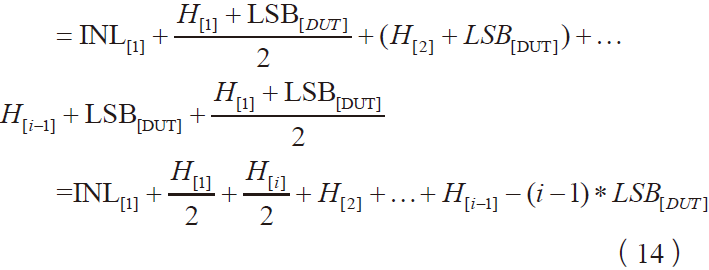

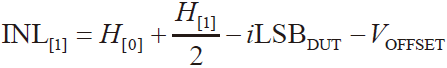

可得直方圖測試法INL[i ]的計算公式

2 測試技術實現(xiàn)

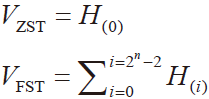

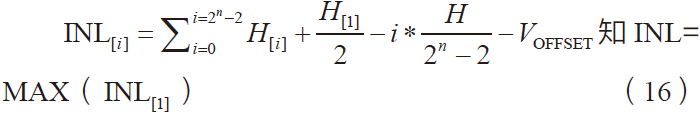

本文選取AD7656BSTZ 型號芯片進行測試分析,分別使用傳統(tǒng)定義法測試和基于直方圖法測試兩種測試方法進行ATE 測試,并分別用這兩種測試方法進行算法編寫代碼,分別計算零點誤差、滿量程誤差、差分非線性誤差、積分非線性誤差。圖2 是器件實物和理想轉換示意圖。

圖2 理想轉換示意圖

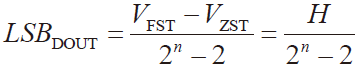

2.1 基于傳統(tǒng)定義法實現(xiàn)測試

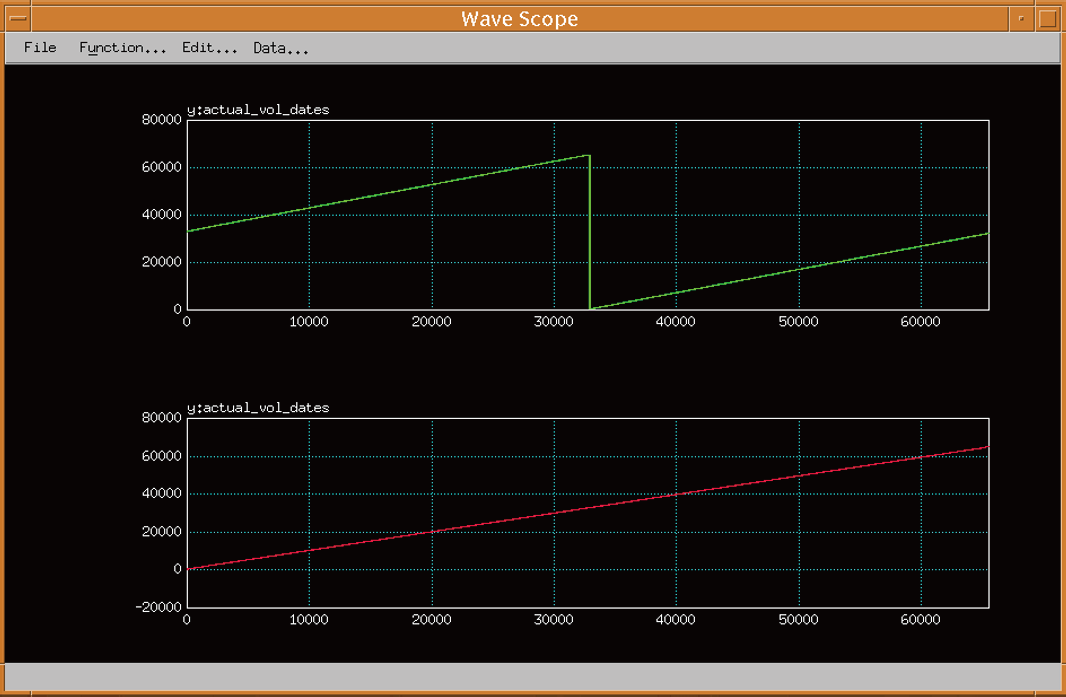

圖3是基于ADVANTEST T6575 測試16 位轉換碼對應的轉換值,采樣點選取了65 536 個點。該芯片為補碼輸出,下圖為ATE 測試補碼輸出和轉換后測試輸出值。ATE將測試的65 536 個轉換值抓取到數(shù)組中進行傳統(tǒng)定義法計算得出EZ、EG、DNL、INL 分別為-0.03%FS、0.02%FS、-1.5LSB、1.2LSB。

圖3 定義測試AD7656BSTZ轉換碼

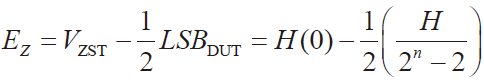

2.2 基于直方圖法實現(xiàn)測試

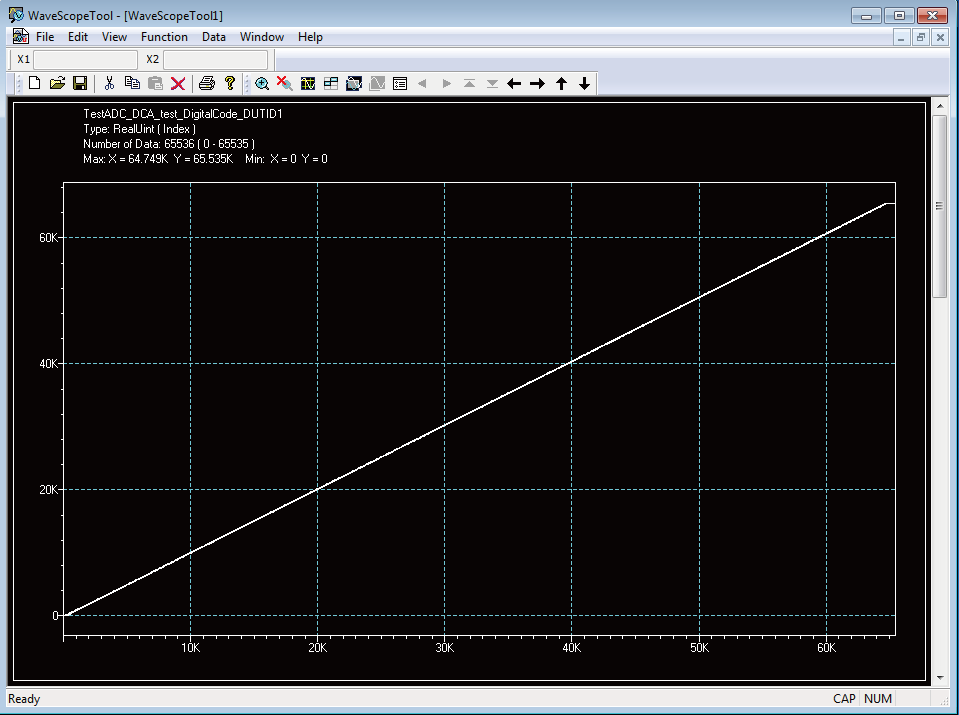

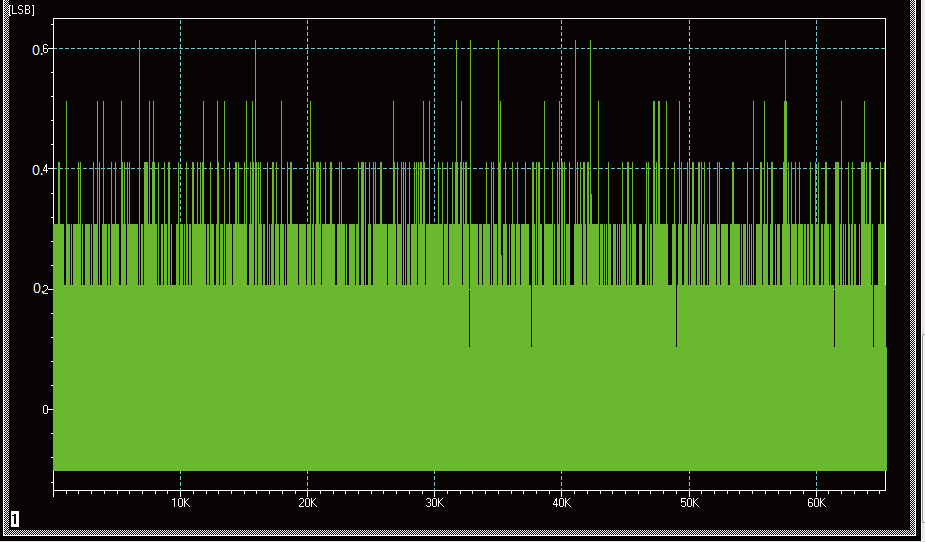

圖4 圖5 是基于ADVANTEST T2000 測試轉換輸出和DNL測試結果。計算得出EZ、EG、DNL、INL 分別為-0.04%FS、0.03%FS、0.6LSB、1.0LSB。

圖4 直方圖法測試轉換碼

圖5 直方圖DNL測試結果

3 對比分析

基于傳統(tǒng)定義法測試特點首先算法簡單容易實現(xiàn),但是算法計算量較大,其次零點誤差和增益誤差可直接計算,并且能夠直觀反映該項參數(shù)的指標。直方圖法測試特點首先在計算DNL 和INL 可剔除系統(tǒng)干擾或者噪聲引起的某個轉換點的突變或者丟碼。其次直方圖法測試需要系統(tǒng)的采樣點多,工程上至少1 個轉換點需要重復測試16 次,才能保證該算法的優(yōu)勢。但同時也增加了測試時間。

參考文獻:

[1] 胡春.基于精度的12位逐次逼近型ADC的研究與設計.華中科技大學碩士學位論文[D].武漢:華中科技大學, 2005,1-2.

[2] 喬高帥.一種高精度逐次逼近模數(shù)轉換器的研究與設計.上海交通大學碩士學位論文[D].上海:上海交通大學, 2009,13-14.

[3] 孫彤,李冬梅.低功耗逐次逼近數(shù)模轉換器的研究與設計.清華大學碩士畢業(yè)論文[D].北京:清華大學, 2007.

[4] LIU W, CHANG Y, S. K. HSIEN, CHEN B W, LEE Y P, et al. A 600 MS/s 30 mW 0.13um CMOS ADC array achieving over 60 dB SFDR with adaptive digital equalization[J].IEEE ISSCC Dig. Tech. Papers, 2009, 2:82-83.

[5] F KUTTNER. A 1.2-V 10-b 20-Msample/s non binary successive approximation ADC in 0.13-um CMOS[J].IEEE ISSCC Dig. Tech. Papers, 2002,2:176–177.

[6] BASTOS J, STEYAERT M, GRAINDOURZE B, et al. Matching of MOS transistors with different layout styles [J].Icmts 1996-1996 IEEE International Conference on Microelectronic Test Structures, Proceedings, 1996, 17-18.

[ 7 ] A L B I N A C M , H A C K L G . L a y o u t p a r a s i t i c interconnections effects on high frequency circuits[J]. 2007 IEEE Dallas/Cas Workshop on System-on-Chip (Soc): Design, Applications, Integration, and Software, 2007, 71-74.

[8] T WAKIMOTOW, LI H, K. MURASE. Statistical analysis on the effect of capacitance mismatch in a high-resolution successive approximation ADC[J].IEEJ Electrical and Electronic Engineering, 2011, 6(S1). S89-S93.

(本文來源于《電子產品世界》雜志2023年5月期)

評論