一種使用Python來分析混合模式信號鏈中噪聲的簡單方法

實(shí)驗(yàn)室噪聲源

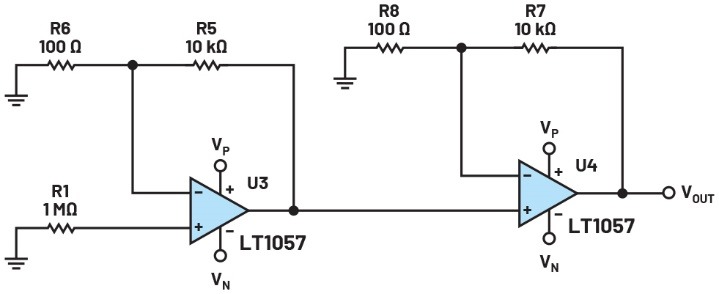

一個校準(zhǔn)過的噪聲發(fā)生器就像是“世界上最糟糕的傳感器”,它模擬傳感器的噪聲,但實(shí)際上不做任何檢測。這種發(fā)生器允許直接測量信號鏈的噪聲響應(yīng)。圖18所示的電路使用1MΩ電阻作為127nV/√Hz(在室溫下)噪聲源,具有“合格”的精度和帶寬。雖然精度只是合格,此方法也有其優(yōu)勢:

■ 它基于第一原則,因此在某種意義上可以作為一種未校準(zhǔn)的標(biāo)準(zhǔn)。

■ 它是真正隨機(jī)的,不含重復(fù)的模式。

OP482是一款超低偏置電流放大器,具有相應(yīng)的低電流噪聲,以及足夠低的電壓噪聲,所以,1MΩ輸入阻抗導(dǎo)致的噪聲占主導(dǎo)地位。配置增益為2121,輸出噪聲為269μV/√Hz。

圖18 一個1MΩ電阻作為可預(yù)測的噪聲源,然后通過低噪聲運(yùn)算放大器放大到可用的水平

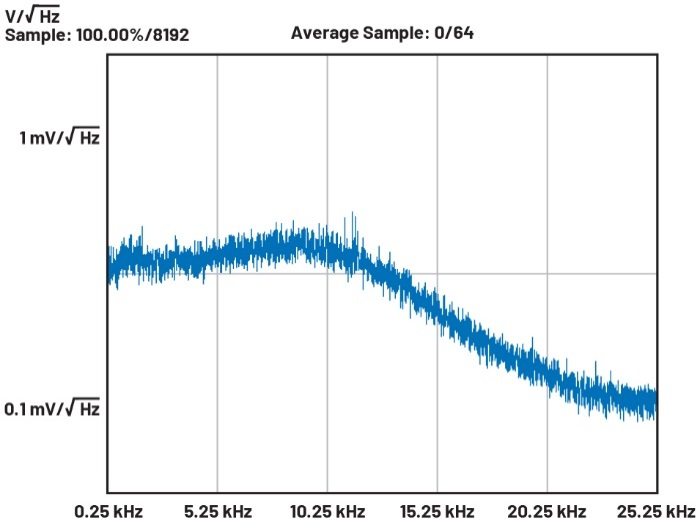

使用ADALM2000 USB儀器,以及Scopy GUI的頻譜分析儀驗(yàn)證噪聲源,如圖19所示。9

圖19 基于電阻的實(shí)驗(yàn)室噪聲發(fā)生器的輸出具有大約10kHz的可用帶寬

在分析儀采用圖示的設(shè)置時,ADALM2000的本底噪聲為40μV/√Hz,遠(yuǎn)低于噪聲源的269μV/√Hz。

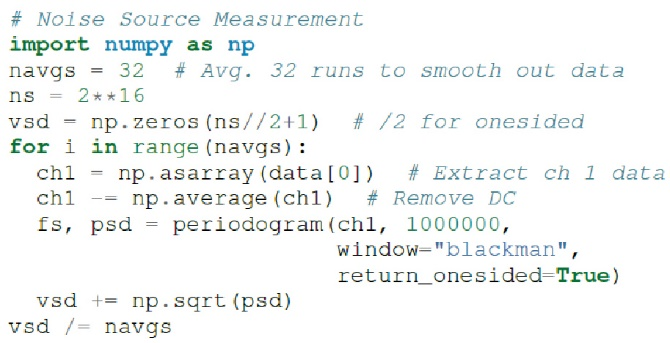

雖然Scopy可用于單次可視測量,但其功能可以通過SciPy周期圖函數(shù)輕松復(fù)制。使用libm2k10和Python捆綁程序從ADALM2000收集原始數(shù)據(jù),進(jìn)行最低限度的處理,以去除直流內(nèi)容(否則會泄漏至低頻率倉),并擴(kuò)展至nV/√Hz。此方法如圖20所示,適用于任何數(shù)據(jù)采集模塊,只要采樣速率是固定的、已知的,且數(shù)據(jù)可以格式化為電壓向量。

圖20 ADALM2000的Python噪聲源測量代碼

我們現(xiàn)在有了已知的噪聲源和測量該噪聲源的方法,它們都可以用來驗(yàn)證信號鏈。

在LTspice中模擬信號鏈

Ltspice??是一款免費(fèi)的通用模擬電路模擬器,可模擬信號鏈設(shè)計(jì)。它可以執(zhí)行瞬態(tài)分析、頻域分析(交流掃描)和噪聲分析,分析結(jié)果可以導(dǎo)出并使用Python集成到混合信號模型中。

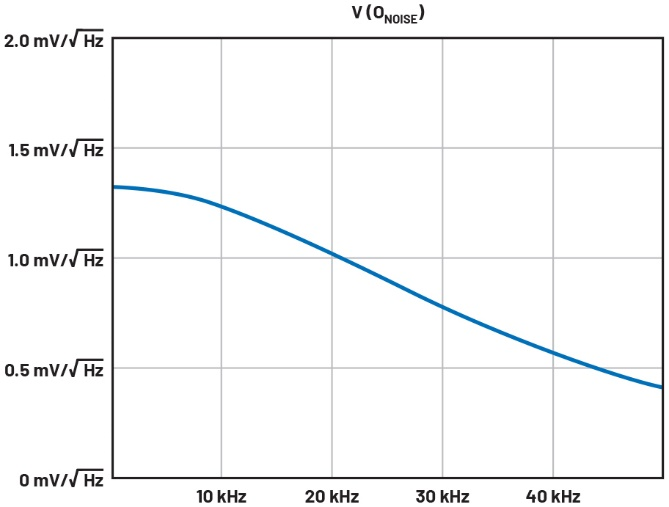

圖21顯示模擬噪聲發(fā)生器的噪聲模擬,與實(shí)驗(yàn)結(jié)果高度一致。使用與OP482的屬性相似的運(yùn)算放大器進(jìn)行模擬。

圖21 對實(shí)驗(yàn)室噪聲源的LTspice模擬顯示出與被測電路大致相同的可用帶寬

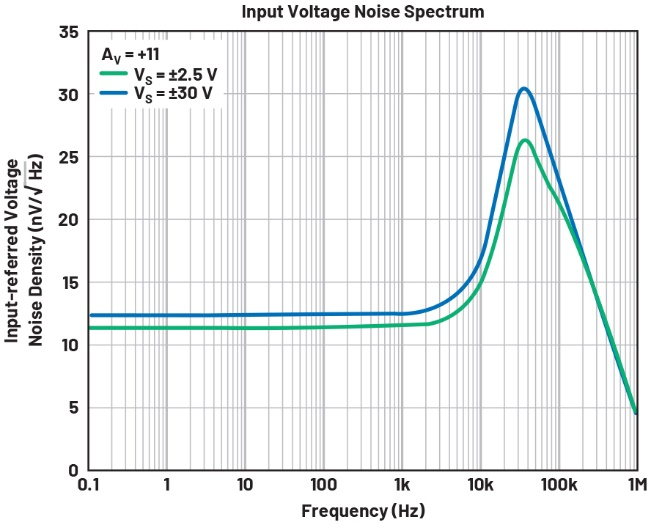

在模擬的時候,圖22的電路噪聲并不重要,它在某些帶寬(相關(guān)信號所在的帶寬)中是恒定的,而在高于這些帶寬的帶寬中,它會按約一階低通響應(yīng)降低。由于高階模擬濾波或有源元件本身,這種技術(shù)在模擬非平坦本底噪聲時非常有用。自動歸零放大器(例如LTC2057)中常見的噪聲山形就是一個典型示例,請參見圖23。

圖22 LTC2057的噪聲密度在低頻率下是平坦的,在50kHz時出現(xiàn)峰值(內(nèi)部振蕩器的100kHz頻率的一半)

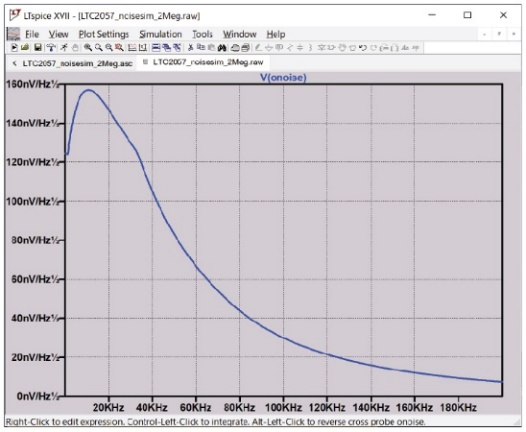

在Python中導(dǎo)入LTspice噪聲數(shù)據(jù)用于頻域分析涉及到設(shè)置模擬命令,以模擬分析向量中的具體頻率。在本例中,噪聲模擬的最大頻率設(shè)置為2.048MHz,分辨率為62.5Hz,對應(yīng)于4.096MSPS采樣率下的第一奈奎斯特區(qū)。圖23顯示同相增益為10時對LTC2057的模擬、模擬輸出和導(dǎo)出的數(shù)據(jù)格式。

圖23 LTspice用于模擬LTC2057在同相增益配置為+10時的輸出噪聲。LTspice提供了用于集成噪聲的簡單工具,但是可以將任何模擬的結(jié)果導(dǎo)出和導(dǎo)入到Python中,以進(jìn)行進(jìn)一步的分析

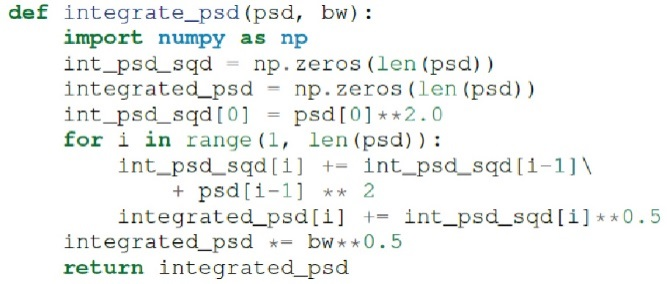

為了確定給定頻帶的噪聲對信號(信噪比)的影響,在相關(guān)帶寬上集成噪聲的和的平方根。在LTspice中,可以通過設(shè)置繪圖界限來集成繪制參數(shù),然后單擊參數(shù)標(biāo)簽。整個2.048MHz模擬過程的總噪聲為32μV rms。在Python中實(shí)現(xiàn)此操作的函數(shù)如圖24所示。

圖24 用于實(shí)現(xiàn)和的平方根的Python代碼

讀取導(dǎo)出的噪聲數(shù)據(jù)并將其傳遞給integrate_psd函數(shù),得出的總噪聲為3.21951e-05,與LTspice計(jì)算得出的值非常接近。

生成測試噪聲

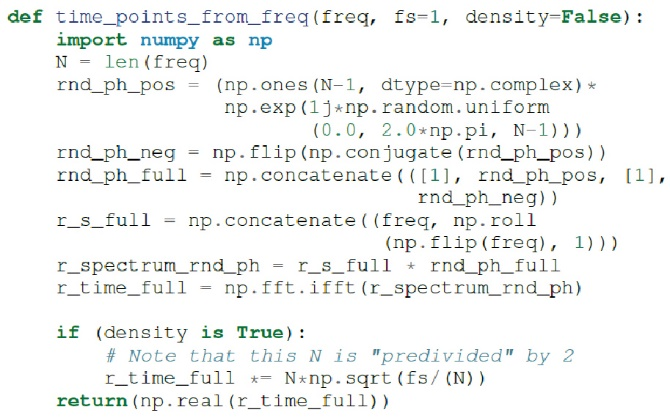

它在純粹的模擬噪聲發(fā)生器的功能上進(jìn)行擴(kuò)展,非常適合用于生成不止是扁平,而且是任意的噪聲剖面——平坦的噪聲帶、粉紅噪聲,或模擬某些放大器的峰值的噪聲山形。由圖25所示的半譜代碼塊生成的時間序列從所需的噪聲譜密度(可以手動生成,或從LTspice模擬中獲取)和時序序列的采樣速率開始,然后生成可以發(fā)送至DAC的電壓時間序列值。

圖25 生成任意噪聲剖面的Python代碼

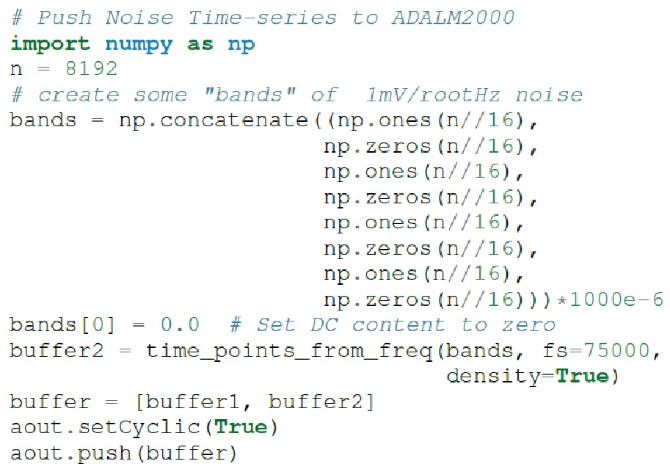

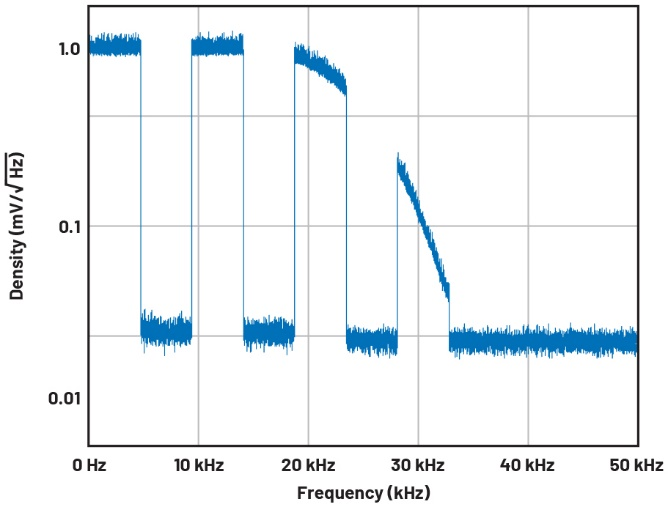

可以通過使用libm2k腳本控制一個ADALM2000,然后使用第二個ADALM2000和Scopy GUI中的頻譜分析儀來驗(yàn)證噪聲剖面,以驗(yàn)證此功能。將噪聲時間序列推到ADALM2000代碼片段(參見圖26),會在ADALM2000 W2輸出上生成4個1 mV/√Hz噪聲帶(在W1上有一個正弦波,用于實(shí)現(xiàn)雙重檢查功能)。

圖26 使用ADALM2000驗(yàn)證任意噪聲

圖27顯示了一個ADALM2000生成的4個1mV/√Hz噪聲帶。輸入矢量長達(dá)8192個點(diǎn),采樣速率為75kSPS,每個點(diǎn)帶寬為9.1Hz。每個頻段為512個點(diǎn),或?yàn)?687Hz寬。高于~20kHz之后出現(xiàn)的滾降是DAC的sinc滾降。如果DAC能夠提供更高的采樣速率,時間序列數(shù)據(jù)就可以通過插值濾波器進(jìn)行上采樣和濾波。11

圖27 Scopy光譜分析儀被用于驗(yàn)證任意噪聲發(fā)生器。噪聲帶之間的深凹痕展示了分析儀的本底噪聲,表明可以準(zhǔn)確地生成任意噪聲剖面

該噪聲發(fā)生器可與純粹的模擬發(fā)生器一起使用,用于驗(yàn)證信號鏈的抑制特性。

模擬和驗(yàn)證ADC噪聲帶寬

外部噪聲源和fS/2以上的雜散音將折回(混疊)到直流到fS/2區(qū)域,轉(zhuǎn)換器可能對遠(yuǎn)遠(yuǎn)超過fS/2的噪聲非常敏感。以LTC2378-20為例,它具有1MSPS采樣速率,34MHz的–3dB輸入帶寬。雖然在如此高的頻率下性能可能不是最好的,但這個轉(zhuǎn)換器會對超過68個奈奎斯特區(qū)的噪聲進(jìn)行數(shù)字化,并將它們折疊回您的信號上。這展示了抗混疊濾波器對寬帶ADC的重要性。精密應(yīng)用的轉(zhuǎn)換器一般采用∑-?(例如AD7124-8)或過采樣SAR架構(gòu),在該架構(gòu)中,輸入帶寬受設(shè)計(jì)限制。

考慮濾波器的等效噪聲帶寬(ENBW)通常是有用的,包括ADC的內(nèi)置濾波器。ENBW是扁平通帶“磚墻”濾波器的帶寬,該濾波器允許通過與非扁平濾波器相同數(shù)量的噪聲。常見示例包括一階RC濾波器的ENBW,其公式為:

其中fC表示該濾波器的截止頻率。如果對1kHz一階低通濾波器的輸入和1.57kHz磚墻低通濾波器的輸入應(yīng)用寬帶噪聲(從“直流到可見光”),輸出端的總噪聲功率將是相同的。

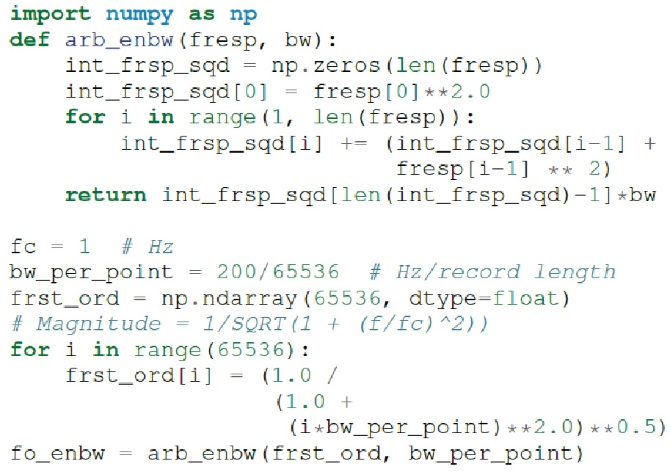

圖28中的ENBW示例代碼塊接受濾波器幅度響應(yīng),然后返回有效噪聲帶寬。計(jì)算并使用單極性濾波器的幅度響應(yīng)來驗(yàn)證ENBW = fC × π/2關(guān)系。

圖28 Python代碼示例,用于計(jì)算有效噪聲帶寬

此函數(shù)可用于計(jì)算任意濾波器響應(yīng)的ENBW,包括AD7124的內(nèi)部濾波器。可以使用與之前的50Hz/60Hz拒波濾波器示例類似的方法來計(jì)算AD7124 sinc4濾波器的頻率響應(yīng)和128SPS采樣速率。arb_anbw函數(shù)返回約31Hz的ENBW。

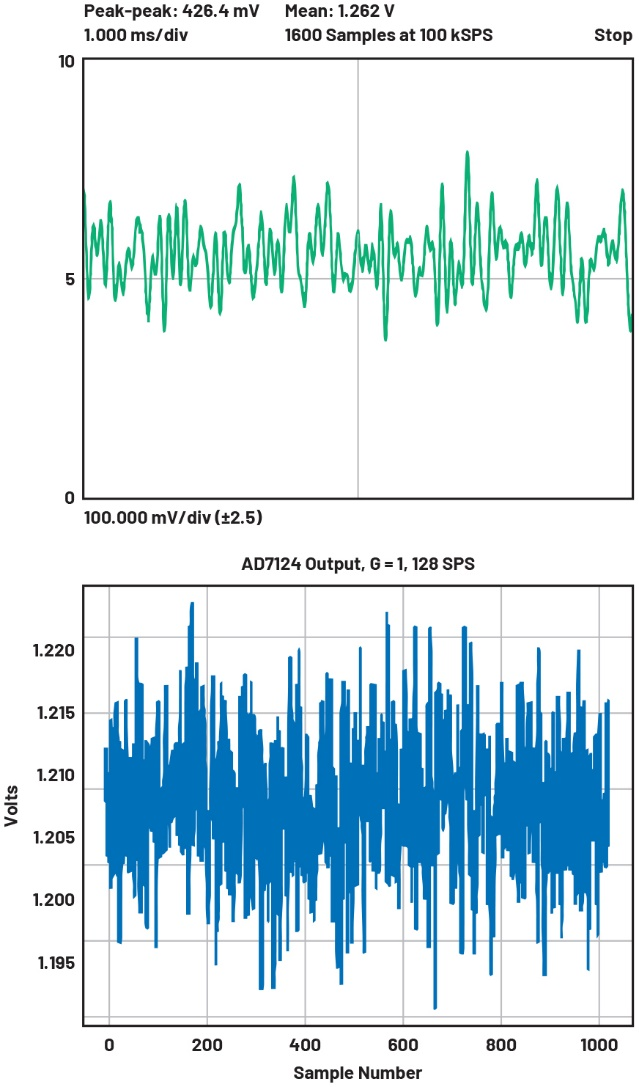

ADALM2000噪聲發(fā)生器可用于驗(yàn)證這一結(jié)果。設(shè)置測試噪聲發(fā)生器生成1000μV/√Hz的頻段會導(dǎo)致約5.69mV rms的總噪聲,測量出的總噪聲約為5.1mV rms。示波器捕獲的ADC輸入信號在ADC輸出數(shù)據(jù)旁邊繪出,如圖29所示。注意,測量到的峰峰值噪聲為426mV,而ADC的峰峰值噪聲約為26mV。雖然在真實(shí)的精密信號鏈中,是無法實(shí)現(xiàn)如此高的噪聲水平的(雖然希望如此),但本練習(xí)表明,可以將ADC的內(nèi)部濾波器作為信號鏈中的主要帶寬限制元件,從而降低噪聲。

圖29 1mV/√Hz噪聲帶被驅(qū)動進(jìn)入AD7124-8輸入。很明顯能夠看到,噪聲出現(xiàn)定量降低;ADC輸入上的426mV峰峰值噪聲會導(dǎo)致ADC輸出上出現(xiàn)約25mV峰峰值噪聲。按照給出的ADC濾波器的噪聲密度為1mV/√Hz,ENBW為31Hz,5.1mV rms總輸出噪聲非常接近預(yù)計(jì)的5.69mV rms

結(jié)論

在任何信號鏈中,噪聲都是一個限制因素;一旦噪聲污染信號,就會致使信息丟失。在構(gòu)建信號采集系統(tǒng)之前,必須先了解應(yīng)用要求,選擇合適的組件,并測試原型電路。ADI在本教程提供了一組可以在設(shè)計(jì)和測試過程中用來準(zhǔn)確模擬和測量傳感器和信號鏈噪聲的方法。

如果單獨(dú)來看,本教程中詳細(xì)介紹的技術(shù)并不新穎。但是,為了實(shí)現(xiàn)一個合適的系統(tǒng),需要一組基本的、易于實(shí)現(xiàn)的低成本技術(shù),以實(shí)現(xiàn)信號鏈模擬和驗(yàn)證。即使制造商繼續(xù)提供性能更好的部件,但這些部件總是存在一定的限制,我們必須意識到這一點(diǎn)。這些技術(shù)不僅可以用于在構(gòu)建混合模式信號鏈之前驗(yàn)證部件,還可以用于識別現(xiàn)有信號鏈中的設(shè)計(jì)錯誤。

參考資料

1 “轉(zhuǎn)換器連接教程。”ADI公司,維基百科,2021年1月。

2 ADI公司教育工具庫。Zenodo,2021年7月。

3 Pauli Virtanen、Ralf Gommers等。“SciPy 1.0:在Python中進(jìn)行科學(xué)計(jì)算的基本算法。”Nature Methods,17(3),2020年2月。

4 Steven W. Smith。面向科學(xué)家和工程師的數(shù)字信號處理指南。California Technical Publishing,1999。

5 Ching Man。“MT-229:量化噪聲:公式SNR = 6.02 N + 1.76的擴(kuò)展推導(dǎo)。”ADI公司,2012年8月。

6 Walt Kester,“MT-001:揭開公式“SNR = 6.02N + 1.76dB”的神秘面紗,以及為什么我們要予以關(guān)注。”(ADI公司,2009年)

7 Charles R. Harris、K. Jarrod Millman等。 “使用NumPy的陣列編程。”Nature,585,2020年9月。

8 “pyadi-iio:適用于IIO驅(qū)動器的器件特定的Python接口。”ADI公司,維基百科,2021年5月。

9“Scopy。”ADI公司,維基百科,2021年2月。

10 “什么是Libm2k?”ADI公司,維基百科,2021年10月。

11 Walt Kester,“MT-017:過采樣插值DAC。”(ADI公司,2009年)

致謝

■ 感謝Jesper Steensgaard,從LTC2378-20開始,他推動了信號鏈設(shè)計(jì)思維范式的轉(zhuǎn)變。

■ 感謝Travis Collins,他架構(gòu)了Pyadi-iio(還有許多其他架構(gòu))。

■ 感謝軟件團(tuán)隊(duì)經(jīng)理Adrian Suciu,他推動了libm2k的開發(fā)。

歸屬

本文首次出現(xiàn)在2021年P(guān)ython科學(xué)計(jì)算大會的會議記錄中,題為“使用Python來分析和驗(yàn)證混合模式信號鏈”。DOI:10.25080/majora-1b6fd038-001。

關(guān)于作者

Mark Thoren于2001年加入凌力爾特(現(xiàn)為ADI公司的一部分),擔(dān)任應(yīng)用工程師,負(fù)責(zé)精密數(shù)據(jù)轉(zhuǎn)換器支持工作。在此期間,他曾擔(dān)任與混合信號應(yīng)用相關(guān)的多個職位,包括開發(fā)評估系統(tǒng)、培訓(xùn)、刊發(fā)技術(shù)資料,以及提供客戶支持。Mark現(xiàn)在是ADI公司系統(tǒng)開發(fā)團(tuán)隊(duì)的一名系統(tǒng)工程師,負(fù)責(zé)開發(fā)參考設(shè)計(jì)和ADI大學(xué)計(jì)劃。Mark擁有緬因大學(xué)奧羅諾分校頒發(fā)的農(nóng)業(yè)機(jī)械工程學(xué)士學(xué)位和電子工程碩士學(xué)位。

Cristina ?uteu于2019年加入ADI公司的系統(tǒng)開發(fā)團(tuán)隊(duì),擔(dān)任系統(tǒng)應(yīng)用工程師。在ADI公司工作期間,她致力于改善軟件,分別擔(dān)任過技術(shù)刊物發(fā)行及培訓(xùn)等多個不同職位,并為ADI大學(xué)計(jì)劃提供學(xué)習(xí)教材,包括ADALM2000視頻系列。Cristina擁有羅馬尼亞布加勒斯特大學(xué)頒發(fā)的電子工程學(xué)士學(xué)位,以及布加勒斯特大學(xué)和法國波爾多大學(xué)聯(lián)合頒發(fā)的信號和圖像處理碩士學(xué)位。

評論