使用CD4007陣列構(gòu)建CMOS邏輯功能

本實驗活動的目標是使用CD4007晶體管陣列構(gòu)建各種CMOS邏輯功能。CD4007包含三對互補的NMOS和PMOS晶體管。

本文引用地址:http://www.104case.com/article/202210/439391.htm使用CD4007晶體管陣列構(gòu)建反相器

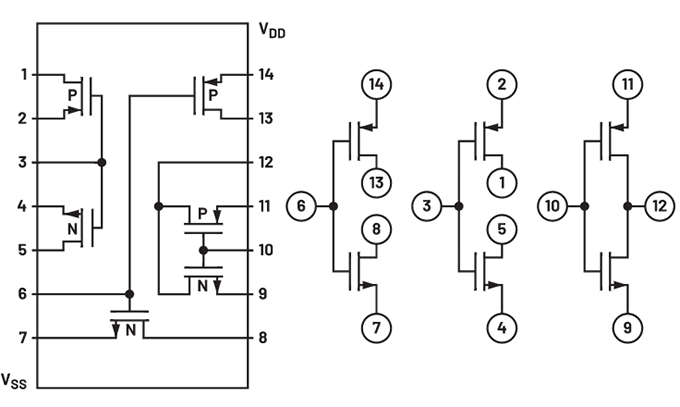

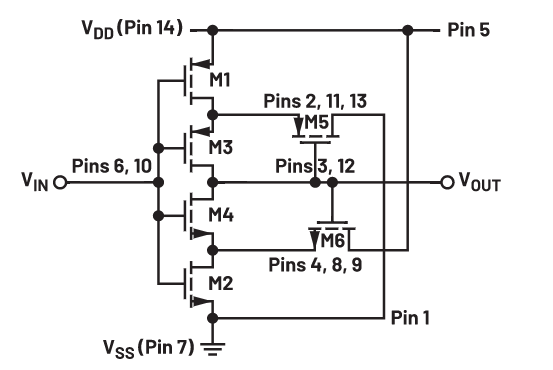

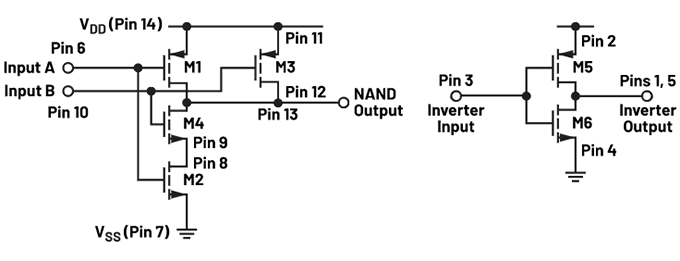

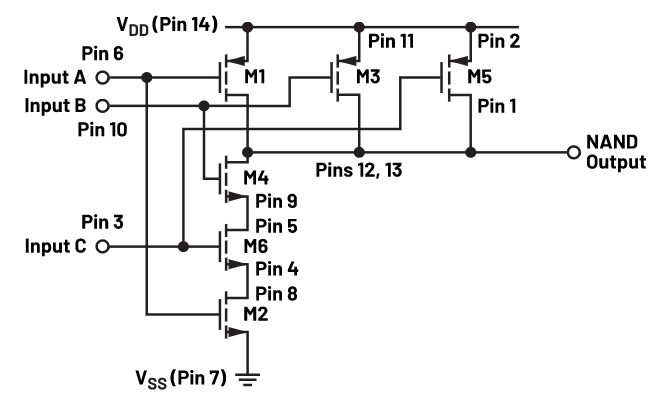

圖1顯示了CD4007的原理圖和引腳排列。

圖1. CD4007 CMOS晶體管陣列引腳排列

多達三個單獨的反相器可由一個CD4007封裝陣列構(gòu)建而成。第一個配置最簡單,如圖2所示,將引腳8和13連接在一起作為反相器輸出即可構(gòu)建。引腳6將作為輸入端。確保將引腳14(VDD)連接到電源,引腳7(VSS)連接到地。

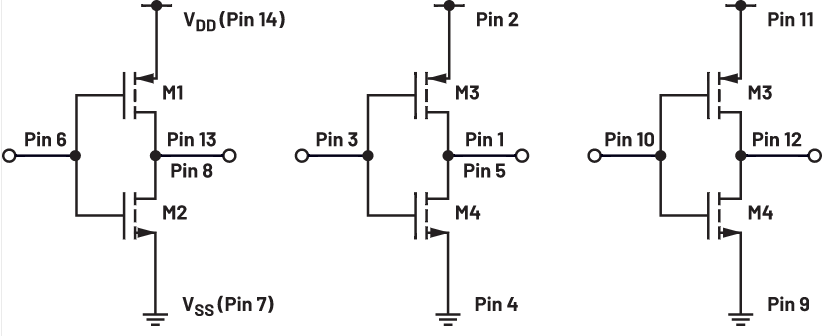

圖2. 三個反相器

第二個反相器是通過將引腳2連接到VDD 且將引腳4連接到 VSS來構(gòu)建的。引腳1和5連接在一起作為輸出,引腳3作為輸入。第三個反相器是通過將引腳11連接到VDD且將引腳9連接到VSS來構(gòu)建的。引腳12為輸出,引腳10為輸入。

CMOS反相器特性表征

CMOS反相器有許多靜態(tài)(DC)和動態(tài)(AC)性能特性,這些參數(shù)通常會固定的并需要測量。本部分我們將測量反相器的若干特性,但其他類型的門電路也可進行相同的測量,本次活動的后面部分 會予以說明。我們將從靜態(tài)特性開始,包括閾值電壓、躍遷區(qū)域?qū)挾取⑤敵鲈春凸嚯娏鳌?/p>

閾值電壓

通常,CMOS制造工藝經(jīng)過特別設(shè)計,使得NMOS和PMOS器件的閾值電壓VTH大致相等,即互補。然后,反相器的設(shè)計人員調(diào)整NMOS和PMOS器件的寬長比W/L,使其各自的跨導(dǎo)也相等。

說明

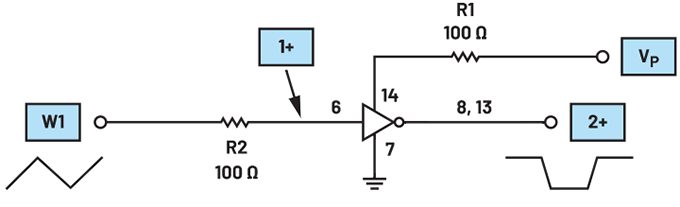

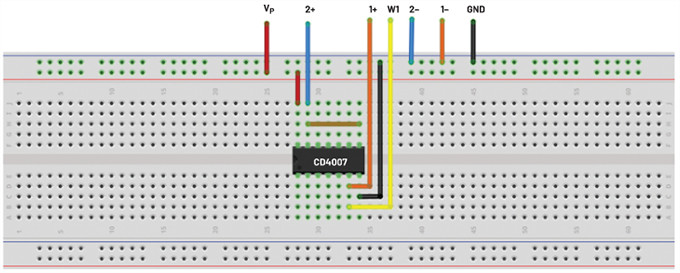

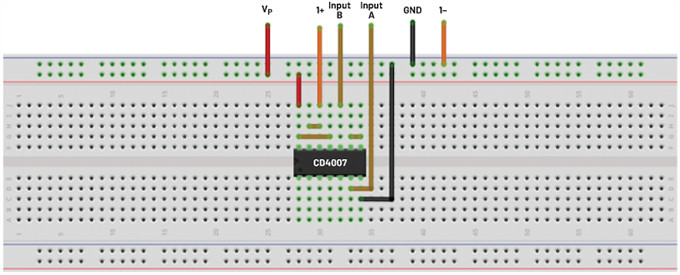

在無焊試驗板上構(gòu)建圖2所示的第一個反相器,以測試CMOS反相 器的輸入到輸出開關(guān)特性。圖3中的藍色框表示ADALM2000上的連接器所需進行的連接。通過100Ω電阻將 VP((5 V)電源連接到 VDD (引腳14)以測量電源電流,并接地至VSS (引腳7)。將波形發(fā)生器的輸出端連接到反相器輸入端(引腳6)以及示波器輸入端1+,并將反相器輸出端(引腳8和13)連接到示波器輸入端2+。將未使用的示波器負輸入端(1-、2-)接地通常也是一個好辦法。

圖3. 測量輸入閾值和躍遷區(qū)域的設(shè)置

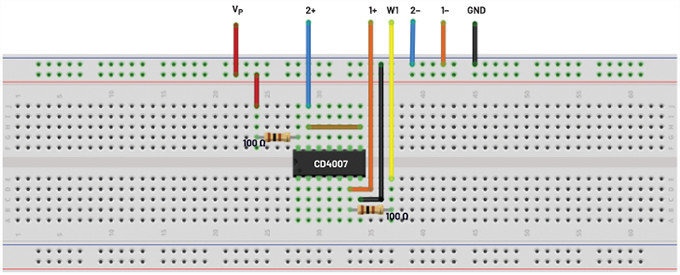

硬件設(shè)置

配置波形發(fā)生器生成100 Hz三角波,峰峰值幅度為5 V,偏移為2.5 V。兩個示波器通道均應(yīng)設(shè)置為1 V/div。將示波器配置為XY模式,水平軸為通道1,垂直軸為通道2。

圖4. 測量輸入閾值和躍遷區(qū)域的試驗板連接設(shè)置

程序步驟

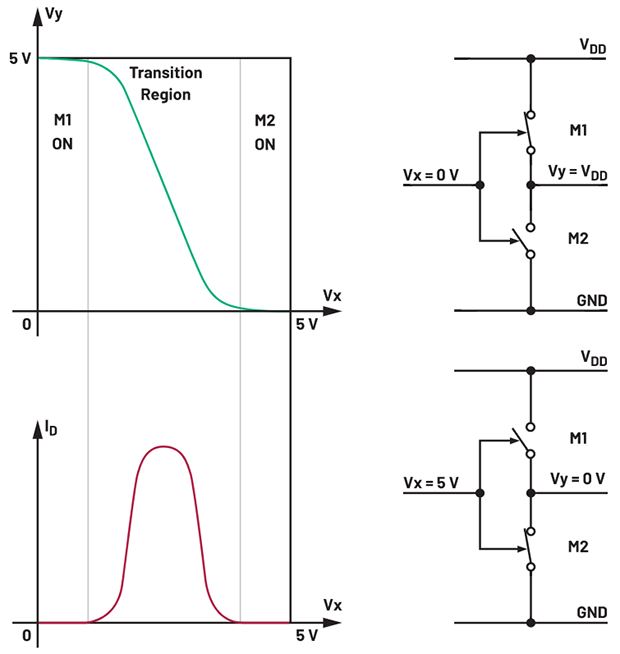

首先使用示波器通道2測量反相器輸出電壓與輸入的關(guān)系;輸入掃描范圍為0 V至5 V,獲得類似圖5上方所示的曲線。

接著移動通道2示波器輸入端2+和2-,以測量圖3中100Ω電阻R1上的電壓。您可能需要調(diào)整通道2的垂直刻度,以便獲得電流波形的最佳視圖。現(xiàn)在,輸入從0 V掃描到5 V,獲得ID與輸入的關(guān)系圖。這應(yīng)當與圖5中的底部曲線非常相似。

圖5. 反相器輸出電壓和電源電流曲線與輸入電壓的關(guān)系

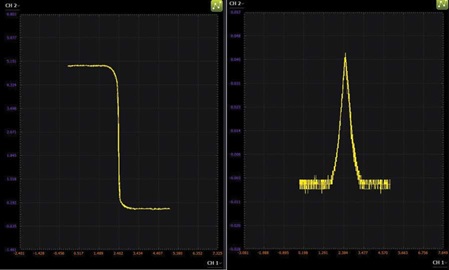

圖6. Scopy屏幕截圖:反相器輸出電壓和電源電流曲線與輸入電壓的關(guān)系

輸入到輸出傳遞特性圖顯示了輸出電壓VOUT與輸入電壓VIN的關(guān) 系。請注意,當輸入電壓從0 V增加到5 V時,輸出電壓從5 V降低到0 V。電源電流特性圖顯示了流經(jīng)VDD和地之間晶體管的電流與輸入電壓VIN的關(guān)系。當輸入電壓接近地和 VDD時,特性曲線有兩部分,并且VDD和地之間沒有電流流動,這些情況很有吸引力,因為在此階段沒有功耗。這就是為什么如今幾乎所有的數(shù)字電路都采用CMOS技術(shù)構(gòu)建的原因。

作為電源的一小部分,躍遷區(qū)域?qū)挾葧a(chǎn)生通常稱之為噪聲容限的性能度量,即輸出保持在恒定高或低電平下的部分輸入范圍。考慮到噪聲可能疊加于輸入信號上,因此希望輸出不會響應(yīng)小的輸入變化。窄躍遷區(qū)域也可能減少輸出在狀態(tài)之間轉(zhuǎn)換的時間量,從而降低NMOS和PMOS晶體管部分導(dǎo)通時的直通電流。

動態(tài)性能

本部分我們將研究CMOS反相器的動態(tài)特性,即反相器在輸入信號從低電壓切換到高電壓或從高電壓切換到低電壓時的行為以及相關(guān)功耗。

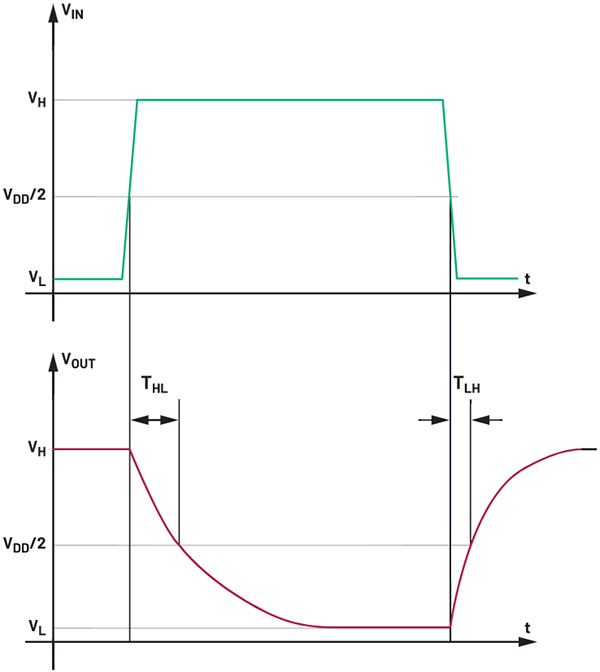

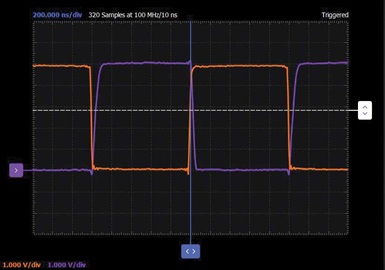

現(xiàn)在我們考慮由電壓脈沖驅(qū)動的CMOS反相器。典型輸入/輸出波形如圖5所示。反相器的動態(tài)行為延遲特性由兩個傳輸延遲時間THL和TLH給出,如圖7所示。請注意,這些傳播時間根據(jù)中間電源電壓VDD/2指定。

圖7. CMOS反相器傳輸延遲

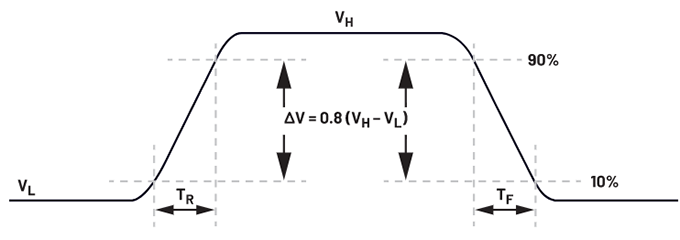

圖8. CMOS反相器上升/下降時間

硬件設(shè)置

現(xiàn)在配置波形發(fā)生器生成500 kHz方波,峰峰值幅度為5 V,偏移為2.5 V。務(wù)必重新連接示波器通道2以測量輸出電壓波形。兩個示波器通道均應(yīng)設(shè)置為每格1 V。調(diào)整水平刻度,以便查看輸入和輸出波形的上升沿和下降沿,如圖7和8所示。

圖9. CMOS反相器試驗板連接

程序步驟

配置示波器通道1和通道2以捕獲輸入和輸出信號的幾個周期。圖10為Scopy波形圖示例。

圖10. Scopy屏幕截圖:CMOS反相器傳輸延遲

測量

傳輸延遲THL和TLH = 輸入躍遷(當 VIN = VDD/2時)與輸出躍遷(當 VOUT = VDD/2時)之間的時間。上升時間TR = 波形從穩(wěn)態(tài)值的10%升至90%所需的時間。下降時間TF = 波形從穩(wěn)態(tài)值的90%降至10%所需的時間。

使用CD4007晶體管陣列構(gòu)建CMOS施密特觸發(fā)器

說明

施密特觸發(fā)器的輸入端(如圖11所示)連接到四個堆疊器件的柵極。上面兩個輸入端連接PMOS,下面兩個輸入端連接NMOS。晶體管M5和M6用作源極跟隨器,通過將輸出電壓VOUT反饋到兩個NMOS和兩個PMOS器件之間的兩個堆疊中間點來引入滯回。

圖11. CMOS施密特觸發(fā)器電路

當 VIN 為0 V時,晶體管M1和M3導(dǎo)通,而M2、M4和M5關(guān)斷。由于VOUT 為高電平,因此M6導(dǎo)通并充當源極跟隨器,而M2的漏極(也是M4的源極)位于VDD至VTH。如果輸入電壓上升至高于地一個閾值的水平,則晶體管M2開始導(dǎo)通,M2和M6均會接通以形成分壓器 網(wǎng)絡(luò),以約一半的電源電壓對M4源極進行偏置。當輸入比1/2VDD高一個閾值時,M4開始導(dǎo)通且即將再次切換。輸入端的任何額外電壓都會導(dǎo)致VOUT下降。當VOUT下降時,M6的源極跟隨其柵極,即VOUT。M6在與M2形成的分壓器中的影響迅速減弱,使VOUT 進一步下降。同時,M5已開始導(dǎo)通,其柵極通過快速下降的VOUT變?yōu)榈碗娖健L幱趯?dǎo)通狀態(tài)的M5使M3源極變?yōu)榈碗娖讲㈥P(guān)斷M3。在M3關(guān)斷的情況下,VOUT 會一直驟降到地。當通過源極跟隨器晶體管的正反饋導(dǎo)致通過堆疊的環(huán)路增益大于1時,會發(fā)生咬合動作。當輸入再次變?yōu)榈碗娖綍r,堆疊上部會發(fā)生類似過程,并且當達到閾值下限時會發(fā)生咬合動作。

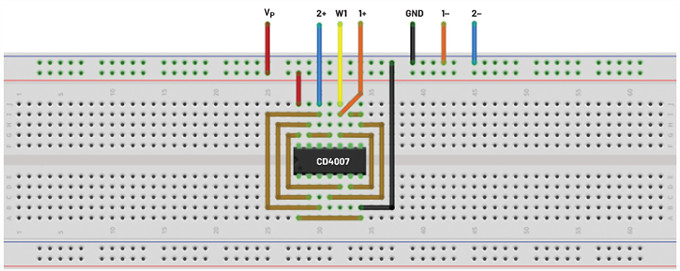

硬件設(shè)置

在無焊試驗板上,構(gòu)建圖11所示的施密特觸發(fā)器電路以測試輸入到輸出開關(guān)特性,就像使用普通反相器所做的那樣。

配置波形發(fā)生器生成1 kHz三角波,峰峰值幅度為5 V,偏移為2.5 V。兩個示波器通道均應(yīng)設(shè)置為每格1 V。將示波器配置為XY模式,水平軸為通道1,垂直軸為通道2。

圖12. CMOS施密特觸發(fā)器電路試驗板連接

程序步驟

使用示波器通道2測量輸出電壓與輸入的關(guān)系;輸入掃描范圍為0 V至5 V,與使用簡單反相器一樣,可得到一個波形圖。

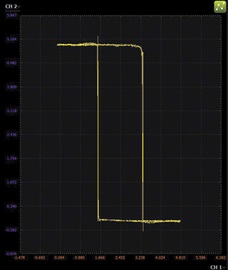

圖13. CMOS施密特觸發(fā)器Scopy圖

使用CD4007晶體管陣列制作NAND/AND門

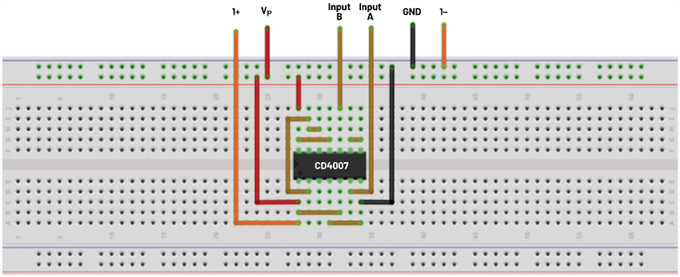

如圖14所示,一個2路輸入NAND門和一個反相器可由一個CD4007封裝陣列構(gòu)建而成。通過將引腳12和13連接在一起作為NAND輸出端來配置NAND門,如圖14所示。引腳14和引腳11連接到VDD以獲得電源,引腳(VSS)連接到地。應(yīng)將引腳9連接到引腳8以構(gòu)成NAND門的N側(cè)。引腳6將作為A輸入端,引腳10將作為B輸入端。

圖14. 2路輸入NAND和反相器

圖15. 2路輸入NAND試驗板連接

圖16. 2路輸入AND試驗板連接

該反相器是通過將引腳2連接到VDD且將引腳4連接到VSS來構(gòu)建的。 引腳1和5連接在一起作為輸出,引腳3作為輸入。將引腳12和13上的NAND輸出端連接到引腳3上的反相器輸入端來構(gòu)建AND門。

使用所有6個器件可構(gòu)建單個3路輸入NAND門,如圖17所示。

說明

同時構(gòu)建2路輸入和3路輸入NAND門,并通過填寫各自真值表來確認其邏輯功能。還可以通過將未使用的輸入端連接到VDD來測量每個輸入端的輸入閾值電壓,正如對簡單反相器所做的那樣。

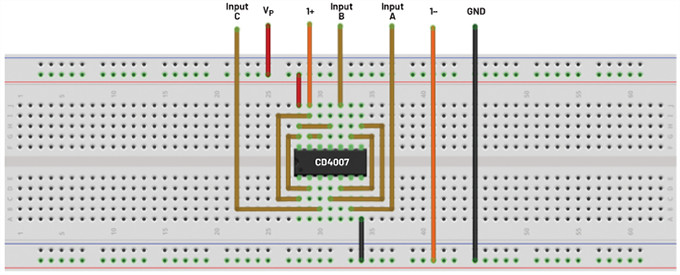

圖17. 3路輸入NAND門

圖18. 3路輸入NAND試驗板連接

評論