超高數據流通量FPGA新品類中的Block RAM級聯架構

概述

本文引用地址:http://www.104case.com/article/202207/435949.htm隨著數據中心、人工智能、自動駕駛、5G、計算存儲和先進測試等應用的數據量和數據流量不斷增大,不僅需要引入高性能、高密度FPGA來發揮其并行計算和可編程硬件加速功能,而且還對大量數據在FPGA芯片內外流動提出了更高的要求。于是,在FPGA芯片中集成包括片上二維網絡(2D NoC)和各種最新高速接口的新品類FPGA芯片應運而生,成為FPGA產業和相關應用的新熱點。

拉開這場FPGA芯片創新大幕的是全球最大的獨立FPGA技術和產品提供商Achronix半導體公司,其采用7nm工藝打造的Achronix Speedster7t FPGA不僅擁有諸多高性能外圍Hard IP,而且是全球首次在FPGA的邏輯陣列上集成了2D NoC,一經推出就在市場得到了積極的響應,并引來競爭對手的模仿和跟隨。

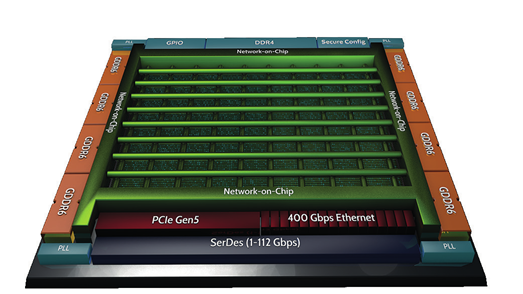

Speedster7t這款專門針對人工智能/機器學習(AI / ML)和高帶寬應用進行優化的高性能、高密度FPGA,包括了革命性的二維片上網絡(2D NoC)、新型機器學習處理器(MLP)、400G以太網和PCIe Gen5端口,以及高帶寬GDDR6和DDR4/5存儲控制器。Speedster7t FPGA架構如圖1所示。

圖1 Speedster7t FPGA結構圖

Achronix Speedster7t FPGA除了在外圍Hard IP上都采用目前業內領先的大帶寬高速率IP,在內部的可編程邏輯的架構中也做了大量的優化去進一步提高內部可編程邏輯的性能,從而適配外圍IP超高帶寬需求。本文首先談談Speedster7t FPGA的片上SRAM,也就是Block RAM針對傳統的結構所做出的一些優化。

Speedster7t FPGA中可編程邏輯的架構

Speedster7t FPGA中內部的可編程資源是按列排布,包括LUT、FF、ALU、MUX、MLP、Block RAM、Logic RAM。如圖2所示。

圖2 Speedster7t FPGA可編程邏輯結構

其中MLP、Block RAM、Logic RAM是集成在一起,他們之間的連接用的是專有的走線,不占用可編程邏輯走線資源,這樣做的目的主要是為了提高性能,同時也可以節省可編程邏輯走線資源,這個架構對于AI,還有需要用到MLP的一些復雜算法的性能優化是非常明顯的,在我們的MLP系列文章中會詳細講到,這里我們只重點說一下Block RAM。

Speedster7t FPGA的Block RAM特點

Speedster7t FPGA內部的Block RAM是一個容量為72k bit的簡單雙端口RAM,有一個讀端口,一個寫端口。兩個端口的時鐘完全獨立,并且可以完全獨立的配置讀寫位寬。它可以靈活的配置成簡單雙端口RAM或者ROM。

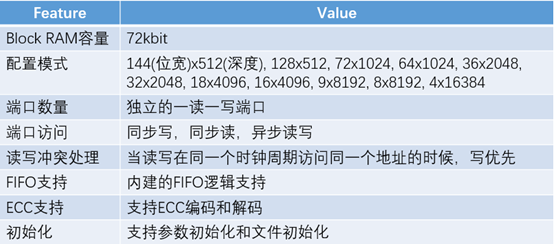

Block RAM的主要特性如表1所示。

表1 Block RAM的關鍵特性

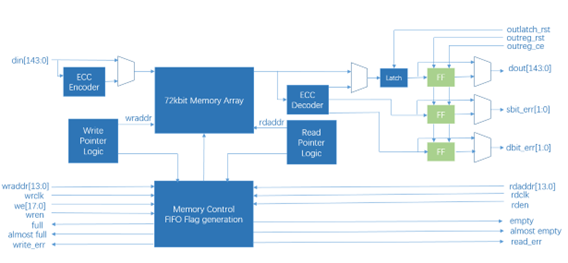

Block RAM框圖如圖3所示。

圖3 Block RAM內部結構

Speedster7t FPGA的Block RAM級聯結構

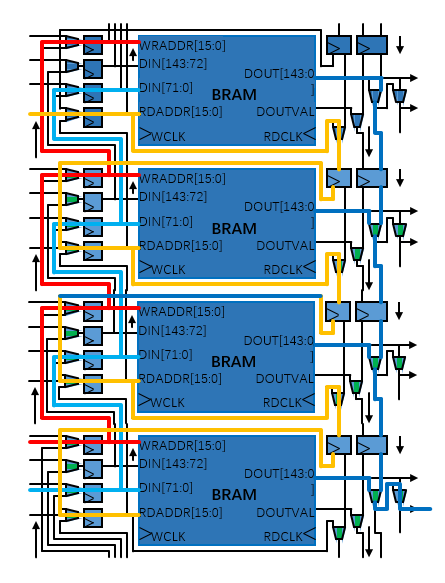

Speedster7t FPGA的Block RAM最大的特點是增加了Block RAM間的級聯走線,級聯走線是BRAM間專有的連線,不占用可編程邏輯的走線資源,可以極大的提升多個Block RAM級聯的性能。圖4顯示了Block RAM間級聯走線的架構。

圖4 Block RAM級聯結構

由圖4可以看出,讀寫地址線和數據線都有專有的級聯線連接。這樣的架構在一些場景中都會有應用,比如:需要從外部端口接收數據或者從GDDR6讀數據去初始化大量Block RAM的場景,AI的神經網絡就是一個典型的應用,在每一層的卷積算法中,系統都會從GDDR6讀出圖像數據和權重數據放入每個引擎的Block RAM中,引擎計算完畢以后再存入到GDDR6中供下一次運算使用。

有了這樣的級聯架構,我們在寫入數據去初始化大量Block RAM的時候不需要外部數據有很大的扇出,直接通過同一列Block RAM的級聯線就可以輕松完成,具體實現可以參考Achronix MLP_Conv2D參考設計。另外一個例子就是在需要多個Block RAM去構成更大容量的RAM的時候,如果利用級聯線可以大大提升系統的性能。我們針對這個專門做了一個工程比較一下,生成一個位寬64bit,深度16384的一個簡單雙端口RAM,需要用到16個Block RAM。我們分別用專有級聯線和內部可編程邏輯去拼深度兩種方法來對比。可以看到用專有的級聯線資源更省,而且性能有了很大的提高。

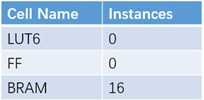

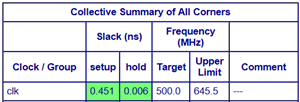

使用專有的級聯線資源占用和性能:

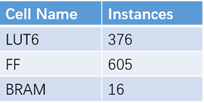

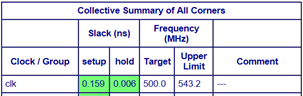

使用可編程邏輯資源占用和性能:

后面我們會繼續深入了解Speedster7t FPGA可編程邏輯的各種特性,并且會用一些例子來說明如何更高效的利用這些特性,以將Speedster7t這款業界首創的高數據帶寬FPGA芯片與更多的創新智能化應用結合起來。

此外,Achronix也提供Speedcore嵌入式FPGA硅知識產權(IP)產品,用來幫助用戶在應用規模進一步擴大后,去開發帶有eFPGA邏輯陣列的ASIC或者SoC產品,它們由Achronix的ACE FPGA開發工具提供支持,從而可以重用FPGA開發成果,這是Achronix在率先引入2D NoC和MLP之外,另一個層面上的創新。

參考文獻:

1 Achronix website www.achronix.com

2 Achronix Speedster7t IP component UG090

評論