簡述Xilinx FPGA管腳物理約束解析

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

本文引用地址:http://www.104case.com/article/202104/424914.htm管腳位置約束: set_property PAKAGE_PIN “管腳編號” [get_ports “端口名稱”]

管腳電平約束: set_property IOSTANDARD “電壓” [get_ports “端口名稱”]

舉例:

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN M14 [get_ports {led[0]}

]set_property PACKAGE_PIN M15 [get_ports {led[1]}]

注意:

1)以上語法對大小寫敏感;

2)端口名稱為數組時,需要用{}括起來,端口名不能為關鍵字。

2. 差分信號約束

2.1 普通差分約束

差分信號約束語法和1節中相同。此處僅舉例。

1)HR I/O Bank,VCCO = 3.3V,HDMI接口約束

set_property PACKAGE_PIN N18 [get_ports TMDS_clk_p]

set_property PACKAGE_PIN V20 [get_ports {TMDS_data_p[0]}]

set_property IOSTANDARD TMDS_33 [get_ports TMDS_clk_p]

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_p[0]}]

2)HP I/O Bank,VCCO = 1.8V,HDMI接口約束

set_property PACKAGE_PIN N18 [get_ports TMDS_clk_p]

set_property PACKAGE_PIN V20 [get_ports {TMDS_data_p[0]}

]set_property IOSTANDARD LVDS [get_ports TMDS_clk_p]

set_property IOSTANDARD LVDS [get_ports {TMDS_data_p[0]}]

注意:

1)差分信號約束,只約束P管腳即可,系統自動匹配N管腳約束,當然_P和_N管腳都約束也沒有問題;

2)差分信號電平要根據VCCO Bank電壓進行相應的約束。

2.2收發器差分信號約束

1)收發器MGTREFCLK時鐘約束管腳位置約束:

set_property LOC “管腳編號” [get_ports “端口名稱”]

舉例:

set_property LOC G7 [get_ports Q2_CLK0_GTREFCLK_PAD_N_IN ]

set_property LOC G8 [get_ports Q2_CLK0_GTREFCLK_PAD_P_IN ]

2)收發器MGT通道約束

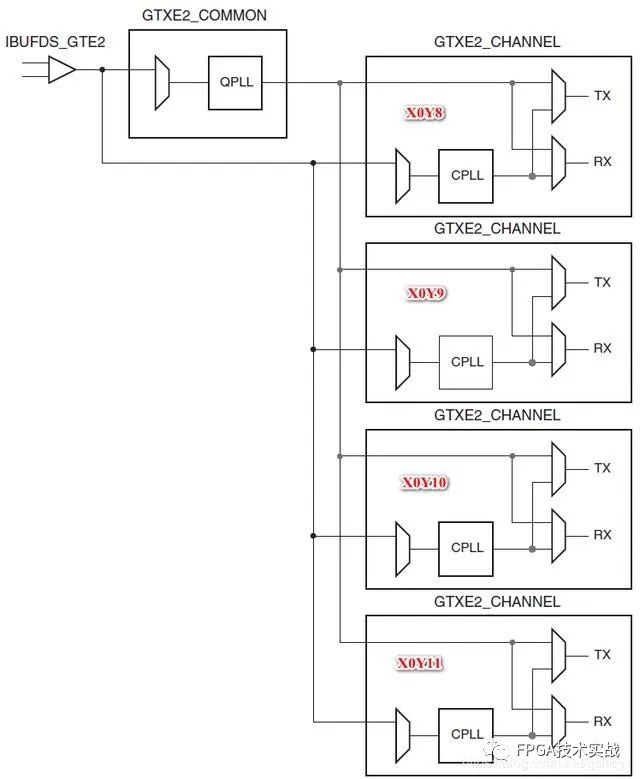

對于GTXE2_CHANNEL通道約束:一種方法是可以利用7系列FPGAs收發器向導,在配置好收發器配置參數后,自動生成XDC模板,然后將該模板應用到自己的設計中;第二種方法是自己編寫XDC約束文件,其位約束位置要參照具體原理圖信號管腳來進行編寫約束文件。舉例:對于圖1中四通道收發器對GTXE2_CHANNEL約束。

圖1、四通道GTX收發器框圖

收發器通道位置約束:

set_property LOC “ GTXE2_CHANNEL_X* Y * ” [get_cells “gtxe_2例化路徑”]

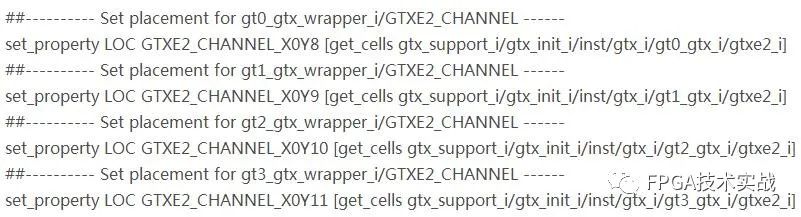

舉例:

圖2、收發器通道位置約束

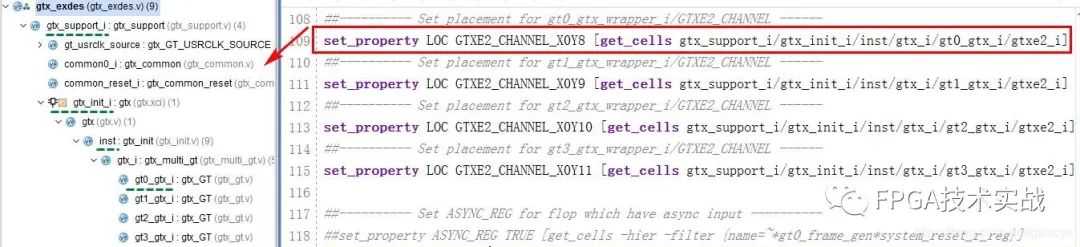

注意:gtxe_2例化路徑參照圖3所示,路徑名稱依據具體工程實現進行修改。

圖3、gtxe_2例化路徑參照圖

評論