小尺寸高分辨率的微顯示系統(tǒng)設(shè)計(jì)及FPGA實(shí)現(xiàn)

0 引言

隨著微顯示概念的不斷發(fā)展,微顯示技術(shù)的逐漸成熟,未來市場對微顯示系統(tǒng)的尺寸與顯示效果有著更高的要求,在顯示系統(tǒng)中,顯示效果直接決定于顯示屏上的像素個(gè)數(shù)也就是顯示分辨率,而為了提升顯示分辨率,最為直接的方法就是增加顯示屏的像素個(gè)數(shù),但這樣做會(huì)大幅增加顯示屏與驅(qū)動(dòng)芯片的尺寸與成本,不適用于微顯示領(lǐng)域的應(yīng)用場景[1]。

因此本文設(shè)計(jì)了一個(gè)小尺寸高分辨率的微顯示系統(tǒng),通過將源圖拆分后對子圖像進(jìn)行動(dòng)態(tài)子像素融合,在只對部分?jǐn)?shù)據(jù)臨時(shí)儲(chǔ)存的情況下對高分辨率的圖像數(shù)據(jù)進(jìn)行實(shí)時(shí)處理,并顯示在低分辨率的顯示屏上,使顯示分辨率提升為原來的四倍,且不增加顯示屏的尺寸,無需儲(chǔ)存圖像數(shù)據(jù)節(jié)省了70% 的FPGA 存儲(chǔ)資源,等效至顯示系統(tǒng)中則減小了驅(qū)動(dòng)芯片接近80% 的面積,實(shí)現(xiàn)了顯示系統(tǒng)微型化的同時(shí)提高了顯示分辨率,滿足了更高要求的微顯示技術(shù)應(yīng)用。

作者簡介:謝博文,碩士生,主要研究方向?yàn)榧呻娐吩O(shè)計(jì)。

黃嵩人,教授,主要研究方向?yàn)镃MOS集成電路研發(fā)。

陳弈星,博士,主要研究方向?yàn)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/微顯示芯片">微顯示芯片設(shè)計(jì)。

1 方法原理

一般來說,顯示屏的分辨率與顯示屏上的最小成像單元總個(gè)數(shù)一致,即分辨率與尺寸成正比[2]。為了在不增加顯示屏尺寸的情況下提高分辨率,復(fù)用相鄰像素的信息,使一個(gè)發(fā)光二極管參與到多個(gè)相鄰像素的成像,這樣一來就能使成像點(diǎn)更多更密,從而不增加顯示屏尺寸也能提高顯示分辨率[3]。但這里面包含了對圖像數(shù)據(jù)的復(fù)雜處理與存儲(chǔ),大大增加了驅(qū)動(dòng)部分的面積與功耗,所以本文針對這一問題進(jìn)行了研究與改進(jìn),通過對進(jìn)來的圖像數(shù)據(jù)進(jìn)行實(shí)時(shí)處理與計(jì)算,在一幀的時(shí)間內(nèi)達(dá)到同樣的顯示效果,既提升了顯示分辨率,又實(shí)現(xiàn)了顯示系統(tǒng)的微型化。

1.1 源圖像拆分方式

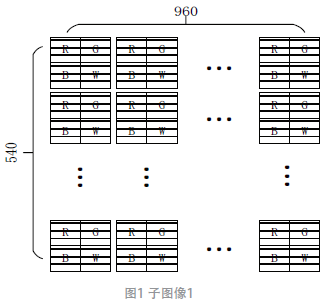

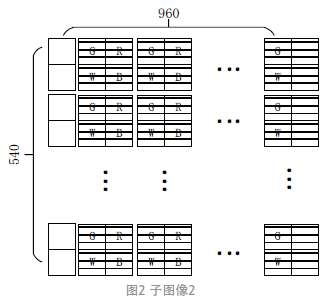

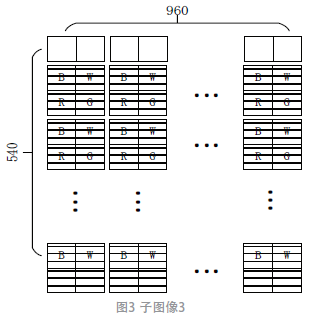

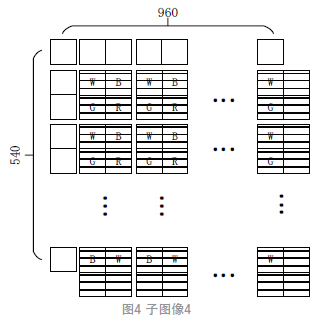

根據(jù)實(shí)際的需求,源圖像可有不同的拆分方式,本文選擇以奇偶行列來劃分源圖像,這種拆分方式不僅簡易且更利于顯示效果的提升[4]。以1080P 的視頻源為例,源圖像的像素共有1 080 行1 920 列,且每個(gè)像素內(nèi)包含R、G、B 三種顏色分量,以奇偶行列為標(biāo)準(zhǔn)拆分,具體拆分方式如下,將源圖像偶數(shù)行與偶數(shù)列的像素取出重新組合為子圖像1,將源圖像偶數(shù)行與奇數(shù)列的像素取出重新組合為子圖像2,將源圖像奇數(shù)行與奇數(shù)列的像素取出重新組合為子圖像3,將源圖像奇數(shù)行與偶數(shù)列的像素取出重新組合為子圖像4,即將1 920×1 080 的源圖像拆分成了四幅960×540 的子圖像,以供后續(xù)的子像素組合。

1.2 子圖像組合方式

由于人眼對亮度的敏感程度大于對色度的敏感程度,本文采用目前十分流行的RGBW 像素排列方式,對比傳統(tǒng)的RGB 像素排列方式,每個(gè)像素顯示單元增加了一個(gè)White 白色子像素,構(gòu)成四色型像素設(shè)計(jì),這種排列方式在提高屏幕亮度的同時(shí)降低了顯示功耗[5]。

具體組合方式如圖所示,子圖像1 在第一個(gè)子幀時(shí)間內(nèi)以圖1 所示位置進(jìn)行顯示,子圖像2 在第二個(gè)子幀時(shí)間內(nèi)以圖2 所示位置進(jìn)行顯示,子圖像3 在第三個(gè)子幀時(shí)間內(nèi)以圖3 所示位置進(jìn)行顯示,子圖像4 在第四個(gè)子幀時(shí)間內(nèi)以圖4 所示位置進(jìn)行顯示,最終在一幀時(shí)間內(nèi)完成了四幅子圖像的顯示,雖然每個(gè)子幀顯示圖像都為低分辨率圖像,但通過時(shí)間與空間的抖動(dòng)疊加成功將高分辨率圖像所有的像素信息保留并顯示出來。

1.3 動(dòng)態(tài)子像素融合

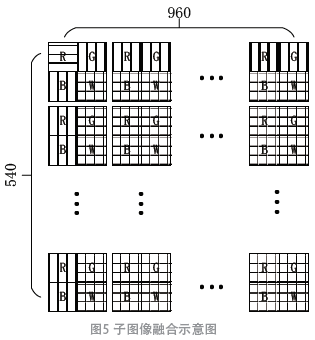

動(dòng)態(tài)子像素融合能使每個(gè)像素點(diǎn)包含多個(gè)位置的像素信息,以此來參加相鄰像素的成像,根據(jù)四幅子圖像空間上的不同位置計(jì)算疊加后的每個(gè)點(diǎn)的子像素信息,融合后的圖像如圖5 所示,田字格橫線代表該點(diǎn)包含一幅子圖像在該點(diǎn)的子像素信息,田字格豎線代表該點(diǎn)融合了兩幅子圖像在該點(diǎn)的子像素信息,田字格橫豎網(wǎng)格線代表該點(diǎn)融合了四幅子圖像在該點(diǎn)的子像素信息,從而高分辨率的圖像信息得以在低分辨率的顯示屏上顯示,顯示分辨率得到提升且無需儲(chǔ)存大量的圖像數(shù)據(jù)。

2 MATLAB驗(yàn)證

在完成對動(dòng)態(tài)子像素融合方法的設(shè)計(jì)之后,使用MATLAB 對這種融合方法進(jìn)行了可行性分析與驗(yàn)證,驗(yàn)證這種動(dòng)態(tài)子像素融合的顯示效果是否有提升以及提升效果如何。

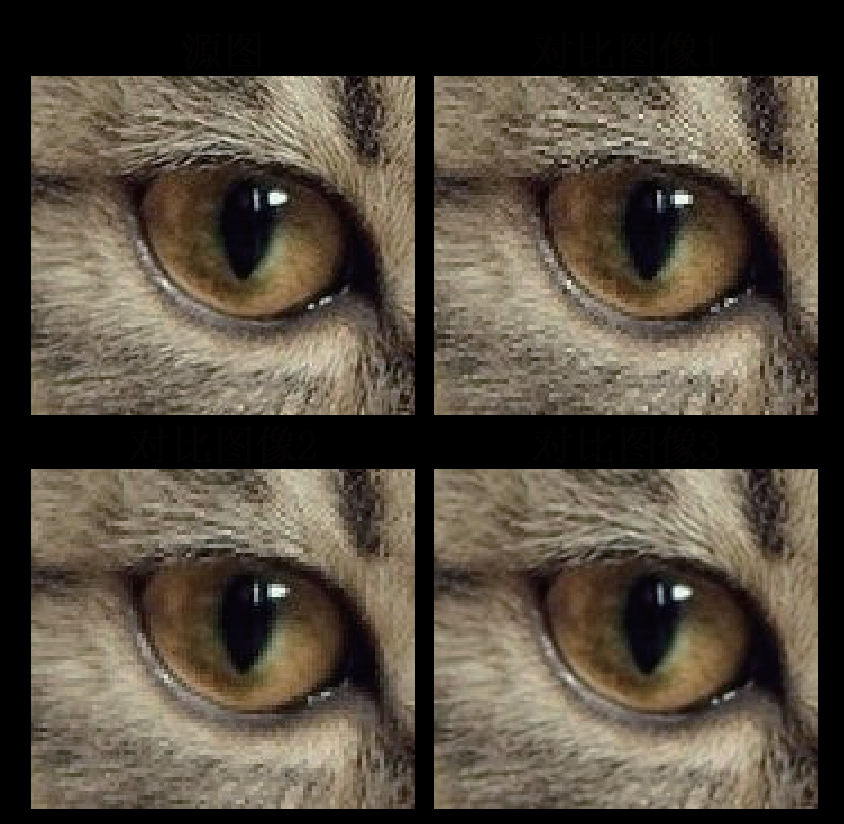

首先對高分辨率的源圖像根據(jù)奇偶行列進(jìn)行拆分,同樣分為四幅子圖像,將只保留偶數(shù)行偶數(shù)列的圖像作為對比圖像1,不在空間上進(jìn)行移動(dòng),直接將四幅子圖像的圖像數(shù)據(jù)進(jìn)行疊加并取平均值的圖像作為對比圖像2,在空間上進(jìn)行抖動(dòng)疊加,進(jìn)行動(dòng)態(tài)子像素融合的圖像作為對比圖像3,對比結(jié)果如圖6 所示。

可以看到,對比圖像1 即只保留四分之一原圖的圖像顯示效果最差,不進(jìn)行動(dòng)態(tài)子像素融合而直接疊加的對比圖像2 效果同樣不佳但優(yōu)于對比圖像1,而完成了動(dòng)態(tài)子像素融合的對比圖像3 效果提升顯著,與源圖像只有著些微差距。

圖6 Matlab仿真對比圖

3 RTL設(shè)計(jì)

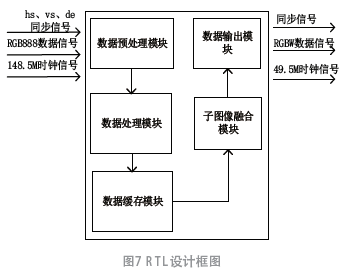

RTL 設(shè)計(jì)中使用Verilog 語言,整體實(shí)現(xiàn)的功能是將1080P 60 Hz 的RGB888 輸入信號(hào),在數(shù)據(jù)預(yù)處理模塊中計(jì)算并轉(zhuǎn)換成RGBW 格式的圖像數(shù)據(jù),在輸入模塊中實(shí)現(xiàn)對源圖像數(shù)據(jù)的拆分的同時(shí)對數(shù)據(jù)進(jìn)行臨時(shí)儲(chǔ)存,而輸出模塊直接根據(jù)動(dòng)態(tài)子像素融合的規(guī)律,將臨時(shí)儲(chǔ)存的圖像數(shù)據(jù)進(jìn)行實(shí)時(shí)計(jì)算,在一幀的時(shí)間內(nèi)完成整幅圖像數(shù)據(jù)的融合并送出至顯示屏上,整體的設(shè)計(jì)框圖如圖7 所示。

3.1 數(shù)據(jù)預(yù)處理模塊設(shè)計(jì)

數(shù)據(jù)預(yù)處理模塊在視頻數(shù)據(jù)作為RGB888 格式進(jìn)來之后,通過輸入時(shí)鐘產(chǎn)生延時(shí)信號(hào),在一定的延時(shí)時(shí)間內(nèi)完成對亮度信息W 的計(jì)算,具體可通過Gray (W) = R×0.299 +G×0.587 + B×0.114計(jì)算而得[5],這時(shí)數(shù)據(jù)被轉(zhuǎn)化為了RGBW 的數(shù)據(jù)格式,并與數(shù)據(jù)同步信號(hào)一起輸出至數(shù)據(jù)處理模塊。

3.2 數(shù)據(jù)處理模塊設(shè)計(jì)

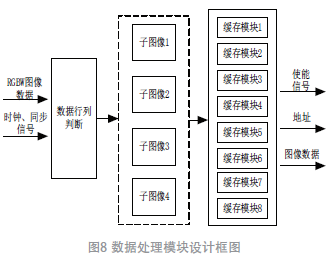

數(shù)據(jù)處理模塊設(shè)計(jì)圖如圖8 所示,在RGBW 格式的數(shù)據(jù)信號(hào)輸入的同時(shí),對視頻源的圖像數(shù)據(jù)進(jìn)行子圖像劃分,偶數(shù)行偶數(shù)列作為子圖像1 處理,偶數(shù)行奇數(shù)列作為子圖像2 處理,奇數(shù)行偶數(shù)列作為子圖像3 處理,奇數(shù)行奇數(shù)列作為子圖像4 處理,由于動(dòng)態(tài)子像素融合實(shí)時(shí)處理的特性,需要用8 個(gè)緩存模塊來暫存四行的數(shù)據(jù),以此來保證每個(gè)像素點(diǎn)都能包含多個(gè)相鄰像素點(diǎn)的信息,同時(shí)將行列與讀寫的控制信號(hào)送入數(shù)據(jù)緩存模塊與子像素融合模塊。

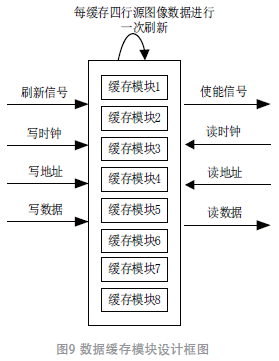

3.3 數(shù)據(jù)緩存模塊設(shè)計(jì)

數(shù)據(jù)緩存模塊共有8 個(gè)緩存模塊,設(shè)計(jì)框圖如圖9 所示,該模塊可同時(shí)進(jìn)行讀寫,讀寫時(shí)鐘都為148.5 MHz,輸入的數(shù)據(jù)以RGBW 格式進(jìn)行緩存,數(shù)據(jù)每輸入四行完成對緩存模塊的一次刷新,在數(shù)據(jù)處理模塊至少寫入一行圖像數(shù)據(jù)之后開始讓子像素融合模塊讀取數(shù)據(jù),同時(shí)將數(shù)據(jù)的控制信號(hào)送入子像素融合模塊用于進(jìn)一步計(jì)算( 如圖9)。

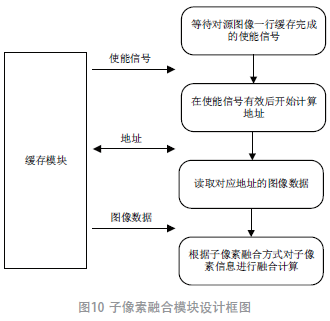

3.4 子像素融合模塊設(shè)計(jì)

子像素融合模塊設(shè)計(jì)圖如圖10 所示,在數(shù)據(jù)緩存模塊至少存入一行時(shí)開始讀取圖像數(shù)據(jù),同時(shí)根據(jù)送入的控制信號(hào)對數(shù)據(jù)進(jìn)行相應(yīng)的計(jì)算,確定融合方式之后每個(gè)子像素點(diǎn)得以根據(jù)行列的控制信號(hào)進(jìn)行計(jì)算,從而完成子像素的融合,再將得到的數(shù)據(jù)與控制信號(hào)送入數(shù)據(jù)輸出模塊。

3.5 數(shù)據(jù)輸出模塊設(shè)計(jì)

數(shù)據(jù)輸出模塊的輸入時(shí)鐘為148.5 MHz,由于輸入的視頻源數(shù)據(jù)為1080P/60 Hz,而輸出的數(shù)據(jù)格式為RGBW,總的數(shù)據(jù)量為原來的1/3,這里選擇同樣以60 Hz 的幀率進(jìn)行輸出顯示,那么輸出時(shí)鐘為49.5 MHz即可滿足要求[6]。

4 FPGA實(shí)現(xiàn)

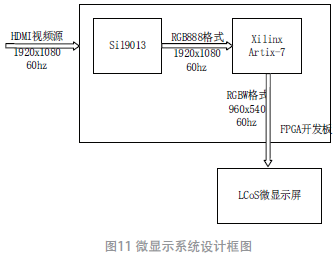

4.1 顯示系統(tǒng)

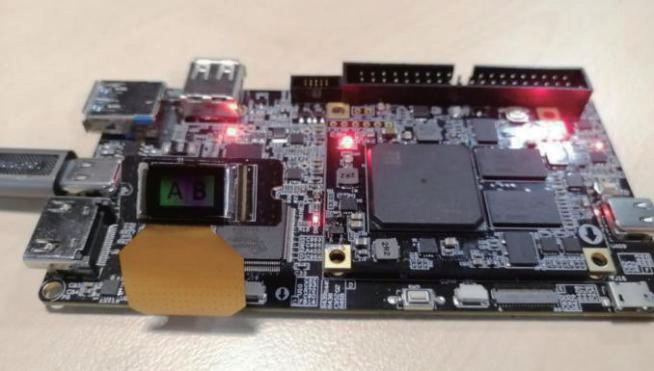

在完成MATLAB 方法驗(yàn)證以及RTL 設(shè)計(jì)之后,在Xilinx Artix-7 系列型號(hào)為AX7013 的FPGA 開發(fā)板上實(shí)現(xiàn)了這種動(dòng)態(tài)子像素融合方法,該顯示系統(tǒng)的設(shè)計(jì)圖如圖11 所示。Sil9013 芯片將HDMI 標(biāo)準(zhǔn)的視頻源數(shù)據(jù)格式轉(zhuǎn)換成RGB888 格式的圖像數(shù)據(jù),F(xiàn)PGA 芯片實(shí)現(xiàn)RTL 設(shè)計(jì)的功能[7],完成數(shù)據(jù)同步與動(dòng)態(tài)子像素融合,最終輸出960×540 分辨率的RGBW 格式數(shù)據(jù)至LCoS 微顯示屏,在實(shí)現(xiàn)顯示系統(tǒng)微型化的同時(shí)提升了顯示分辨率,使960×540 分辨率的微顯示屏能顯示出1 920×1 080 分辨率的圖像顯示效果,圖12 為上述顯示系統(tǒng)的實(shí)物圖。

圖12 微顯示系統(tǒng)實(shí)物圖

4.2 使用資源對比

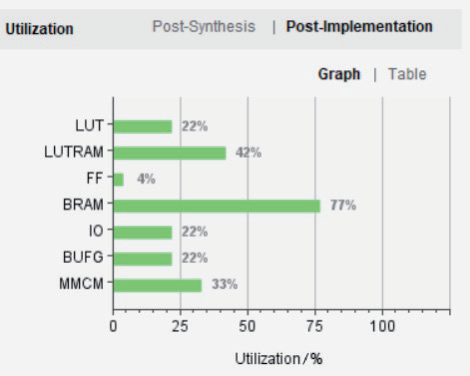

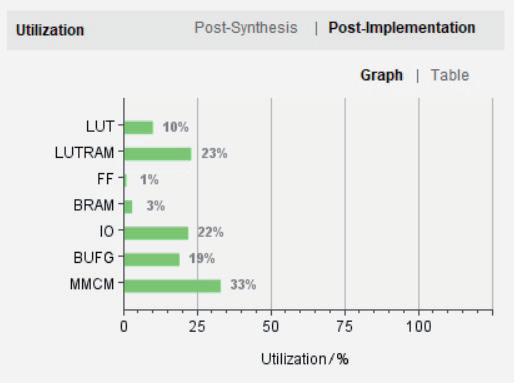

過去提升同等倍數(shù)分辨率的顯示系統(tǒng),消耗了過多的FPGA 存儲(chǔ)資源[8],具體如圖13 所示,可見BRAM資源占用率達(dá)到77%。而本文采用動(dòng)態(tài)子像素融合的設(shè)計(jì)只需將一幀視頻圖像的兩行數(shù)據(jù)暫存下來,對數(shù)據(jù)進(jìn)行實(shí)時(shí)地計(jì)算處理,并完成高分辨率的顯示,具體如圖14 所示,BRAM 資源占用率僅有3%,節(jié)省了74% 的存儲(chǔ)資源,等效至顯示系統(tǒng)中的驅(qū)動(dòng)芯片可減小80%以上的芯片面積。

圖13 使用動(dòng)態(tài)子像素融合前的FPGA使用資源

圖14 使用動(dòng)態(tài)子像素融合后的FPGA使用資源

4.3 顯示效果驗(yàn)證

為了驗(yàn)證實(shí)際的顯示效果在動(dòng)態(tài)子像素融合之后是否得到了提升,以及實(shí)際提升的效果如何,在已完成的RTL 設(shè)計(jì)中加入了寄存器配置模塊,使點(diǎn)屏之后能通過I2C 接口進(jìn)行配置選擇不同圖像數(shù)據(jù)輸出,在實(shí)際點(diǎn)屏?xí)r切換幾種經(jīng)過不同處理的圖像來進(jìn)行對比顯示。

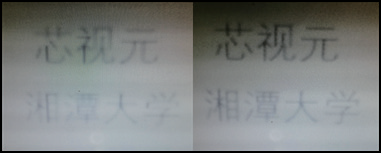

實(shí)際點(diǎn)屏的對比圖如圖15 所示,左圖是未進(jìn)行動(dòng)態(tài)子像素融合而直接將四幅子圖像疊加后的圖像,右圖進(jìn)行動(dòng)態(tài)子像素融合后的圖像,通過高倍放大后的對比可以看出,經(jīng)過子像素動(dòng)態(tài)融合后的圖像顯示效果遠(yuǎn)好于未經(jīng)處理的對比圖像顯示效果。

圖15 實(shí)際點(diǎn)屏對比圖

5 結(jié)語

本文針對顯示系統(tǒng)的微型化與高分辨率顯示的需求設(shè)計(jì)并實(shí)現(xiàn)了一種小尺寸高分辨率微顯示系統(tǒng),相較過去提升同等分辨率的顯示系統(tǒng),節(jié)省了FPGA 中74%的存儲(chǔ)資源,等效至顯示系統(tǒng)中可減小驅(qū)動(dòng)芯片80%以上的芯片面積,實(shí)時(shí)地對視頻圖像數(shù)據(jù)進(jìn)行處理計(jì)算并顯示,通過這種子像素動(dòng)態(tài)融合兼顧了顯示系統(tǒng)的微型化與高分辨率。在通過MATLAB 與FPGA 的共同對比驗(yàn)證后,證實(shí)了這種顯示系統(tǒng)的可行性與有效性,節(jié)省資源降低功耗的同時(shí)提升了接近四倍的顯示分辨率,在微顯示領(lǐng)域具有很高的應(yīng)用價(jià)值。

參考文獻(xiàn):

[1] 梁靜秋.微顯示器件的研究進(jìn)展[J].光機(jī)電信息,2010,27(12):21-27.

[2] 梁宇華,朱樟明.硅基液晶(LCoS)微顯示技術(shù)[J].微納電子與智能制造,2020,2(02):73-79.

[3] CRAIG W,ERIC E,KEN F,et al.63‐4:Q‐View Technology- Approach to Achieving High Resolution and Low Power in Small Pixel Micro‐Display[J].SID Symposium Digest of Technical Papers,2018,49(1).

[4] 胡子輝,黃嵩人,陳奕星.一種提高微顯示器顯示分辨率的動(dòng)態(tài)子像素組合方法及FPGA實(shí)現(xiàn)[J].電子產(chǎn)品世界,2020,27(05):51-54+58.

[5] 周莉莎,郭建,陳弈星.YCbCr的LCOS驅(qū)動(dòng)芯片面積優(yōu)化的方案設(shè)計(jì)[J].單片機(jī)與嵌入式系統(tǒng)應(yīng)用,2019,19(03):20-22+27.

[6] SEAN T,SCOTT D,TIMO K.79‐1: Framework for Evaluating Display Resolution and Size in the Context of Video Compression and Visual Acuity[J].SID Symposium Digest of Technical Papers,2019,50(1):1134-1137.

[7] 付昱強(qiáng).基于FPGA的圖像處理算法的研究與硬件設(shè)計(jì)[D].南昌:南昌大學(xué),2006.

[8] 馬飛,黃苒,趙博華,等.基于FPGA的LCoS顯示驅(qū)動(dòng)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[J].液晶與顯示,2012,27(3):364-370.

(本文來源于《電子產(chǎn)品世界》雜志2021年3月期)

評(píng)論