掌控人工智能的力量:使用萊迪思sensAI快速上手

在萊迪思FPGA中構建推理引擎

本文引用地址:http://www.104case.com/article/201902/397747.htm設計AI推理模型的硬件需要不斷平衡所需資源數量與性能和功率要求。萊迪思的ECP5和UltraPlus產品系列能輕松實現這種平衡。

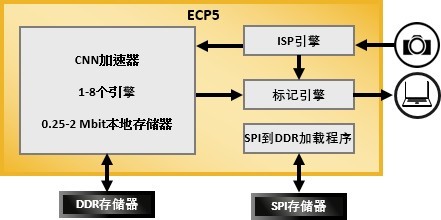

ECP5系列擁有三種不同規格的器件,能夠運行一到八個推理引擎。它們集成的本地存儲器從1 Mb到3.7 Mb不等。功耗最高僅為1 W,尺寸也只有100 mm2。

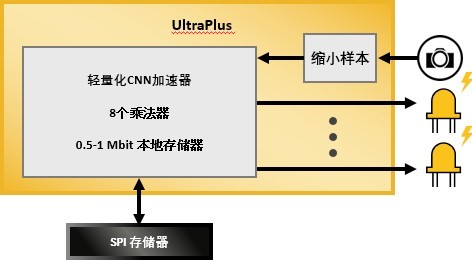

相比之下,UltraPlus系列的功耗水平低至ECP5系列的千分之一,僅為1 mW。占用的電路板面積僅為5.5mm2,包括了最多8個乘法器和最多1 Mb的本地存儲器。

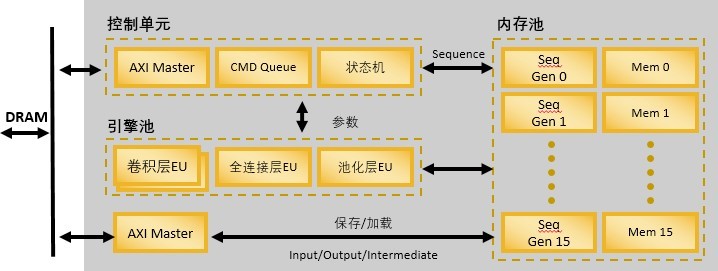

萊迪思還提供可在這些器件上高效運行的CNN IP以及可用于ECP5系列的CNN加速器。

圖4 適用于ECP5系列的CNN加速器

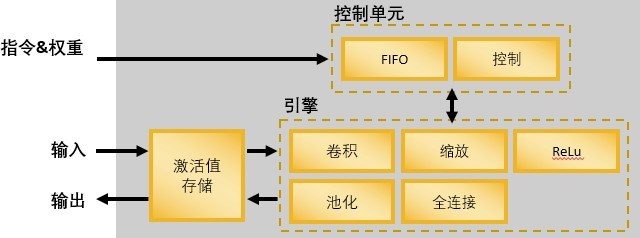

萊迪思還提供可用于UltraPlus系列的輕量化CNN加速器。

圖5 適用于UltraPlus系列的輕量化CNN加速器

這里暫且不談細節;重點在于您無須從頭開始設計自己的AI引擎。您可以聯系萊迪思獲取關于這些IP的更多信息。

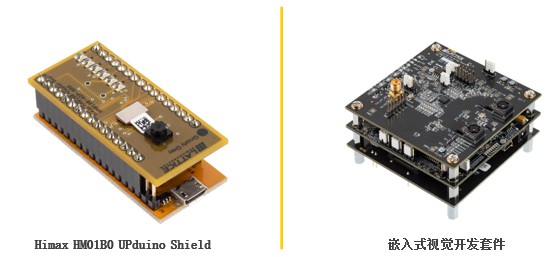

最后,您還可以在開發模塊上運行并測試這些演示,兩個模塊分別對應這兩種產品系列。Himax HM01B0 UPduino Shield采用了一片UltraPlus FPGA, 尺寸為22x50 mm2。嵌入式視覺開發套件采用了一片ECP5 FPGA,尺寸為80x80 mm2。

Himax HM01B0 UPduino Shield 嵌入式視覺開發套件

圖6 評估AI應用的開發模塊

有了FPGA、軟IP和其他處理數據所需的硬件部分,就可以使用Lattice Diamond設計工具進行編譯,從而生成位流,在每次上電后對目標設備中的FPGA進行配置。

在萊迪思FPGA上構建推理模型

創建推理模型與創建底層運行平臺大不相同。它更抽象,涉及更多運算,且不涉及RTL設計。這一過程主要有兩個步驟:創建抽象模型,然后根據所選平臺優化模型的實現。

模型訓練在專門為此過程設計的框架中進行。最流行的兩個框架是Caffe和TensorFlow,但不限于此。

CNN由很多層構成——卷積層,可能還會有池化層和全連接層——每一層都有由前一層的結果饋送的節點。每個結果都在每個節點處加權重,權重多少則由訓練過程決定。

訓練框架輸出的權重通常是浮點數。這是權重最為精確的體現,然而大多數網絡邊緣設備不具備浮點運算功能。這時我們需要針對特定平臺對這個抽象模型進行優化,這項工作由萊迪思的神經網絡編譯器負責。

編譯器可以實現加載和查看從某個CNN框架下載的原始模型。您可以運行性能分析,這對模型優化最關鍵的方面——量化至關重要。

由于無法處理浮點數,因此需要將它們轉換為整數。對浮點數四舍五入也就意味著精度會降低。問題是, 什么樣的整數精度才能滿足您想要的精度?通常使用的最高精度為16位,但是權重和輸入可以表示為較小的整數。萊迪思目前支持16、8和1位的設計實現。

1位的設計實際是在一位整數域中進行訓練以保持精度。顯然,更小的數據單元意味著性能更高、硬件尺寸更小以及功耗更低。但是,精度太低就無法準確地推斷視野中的物體。

圖7 可以對單個模型進行優化以適用于不同的設備

神經網絡編譯器能讓您創建代表模型的指令流,然后可以模擬或直接測試這些指令,從而判斷在性能、功耗和精度之間是否達到了適度的平衡。測試的標準通常是看一組測試圖像(與訓練圖像不同)中正確處理的圖像的百分比。

通常可以通過優化模型來優化運行,包括去掉一些節點以減少資源消耗,然后重新訓練模型。這一設計環節可以微調精度,同時保證能在有限的資源下順利運行。

兩個檢測實例

在以下兩個不同的視覺案例中,我們將看到權衡是如何發揮作用的。第一個應用是人臉檢測;第二個是人員偵測。我們將看到不同FPGA之間存在的資源差異如何影響到相對應的應用的性能和功耗。

兩個示例的輸入都源自同一個攝像頭,兩者都在相同的底層引擎架構中運行。在UltraPlus設計實例中,圖像的尺寸縮小后通過8個乘法器進行處理,利用了內部存儲器并使用了LED指示燈。

圖8 UltraPlus平臺用于人臉檢測和人員偵測應用

ECP5系列資源更多,提供了一個計算能力更強的平臺。攝像頭捕捉的圖像在發送到CNN之前在圖像信號處理器(ISP)中進行預處理。處理結果與原始圖像在標記引擎上比對,從而將文本或注釋覆蓋在原始圖像上。

圖9 ECP5平臺用于人臉檢測和人員偵測應用

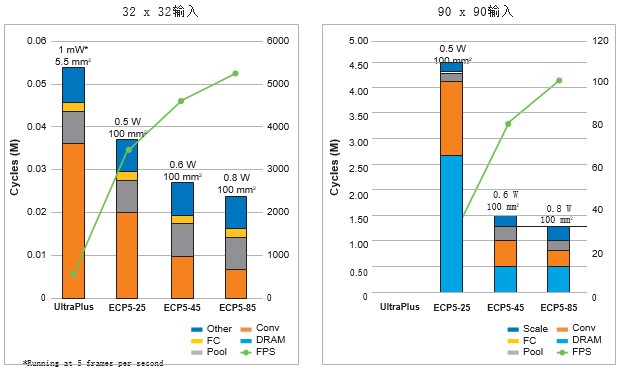

我們可以使用一系列圖表來衡量兩種應用的性能、功耗和占用面積情況。對于每個應用,我們做了兩組示例:一組輸入較少,一組輸入較多。

圖7表示了人臉檢測應用的結果。兩組分別采用了32x32輸入和90x90輸入的情況。

圖10 在UltraPlus和ECP5 FPGA上實現簡單和復雜的人臉檢測應用時的性能、功耗和占用面積

左側的軸代表處理一張圖片需要的周期數量以及這些周期的分配情況。右側的軸代表在各器件(綠線)上實現的每秒幀數(fps)。最后,每種情況下還標注了功耗和占用面積。

左側的32x32輸入示例中,橙色部分代表卷積層上運行的周期。在四個示例中,UltraPlus的乘法器數量最少;其他三片ECP5 FPGA的乘法器數量依次遞增。隨著乘法器數量的增加,卷積層所需的周期數減少。

90x90輸入的示例位于右側,得到的結果完全不同。在每個柱形圖的底部有大面積的藍色區域。這是由于設計更為復雜,使用了除器件內部存儲空間以外的更多存儲器。由于需要占用外部DRAM,性能就有所損失。需要注意的是,這種設計無法使用較小的UltraPlus器件。

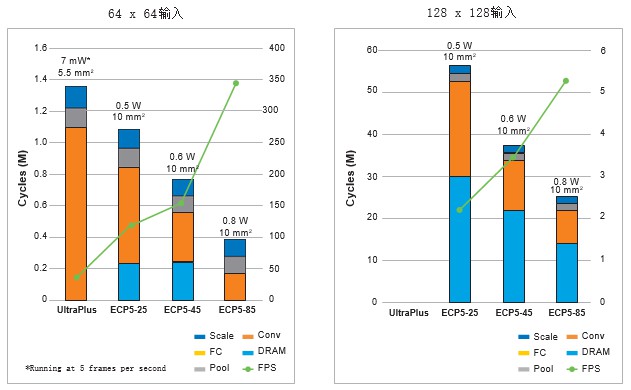

人員偵測應用的情況類似。兩組分別采用了64x64輸入和128x128輸入的情況。

圖11 在UltraPlus和ECP5 FPGA上實現簡單和復雜的人臉檢測應用時的性能、功耗和占用面積

同樣,較多的乘法器會減少卷積層的負擔,而依賴DRAM則會影響性能。

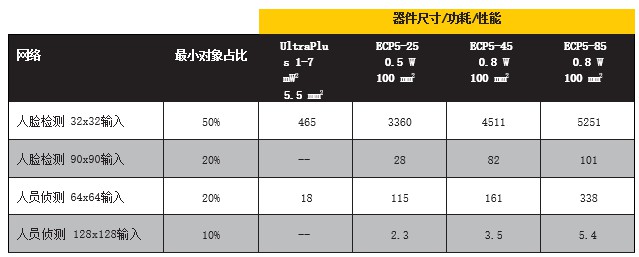

圖9總結了各類情形下的性能。它包括了對圖像中最小可識別對象或特征的度量,用視野范圍的百分比表示。在這里使用更多輸入能夠為較小的目標提供更多分辨率。

圖12 兩個應用示例在四片FPGA上的性能總結

小結

總之,使用萊迪思sensAI產品提供的資源,您就可以在萊迪思FPGA上輕松實現要求低功耗、具有靈活性和可擴展性的網絡邊緣AI推理設計。它可以提供成功部署AI算法所需的關鍵要素:

? 神經網絡編譯器

? 神經引擎軟IP

? Diamond設計軟件

? 開發板

? 參考設計

評論