金手套 ADC 錦標賽――SAR 迎戰

一邊是當前流行的SAR ADC,另一邊是相對較新的模數轉換技術∑△ADC,二者比拼的結果會是如何呢?

本文引用地址:http://www.104case.com/article/201809/388834.htm我們要進行七輪角逐,在這七輪中將分別就以下分類項目打分:

1 轉換準確性

2 轉換速度

3 攻擊線性

4 高低壓側轉換準確性

5 差動非線性

6 積分非線性

7 量化誤差

人們已經對兩種技術的比拼等待了很長時間。SAR ADC 和它的新近挑戰技術終于能夠進行一對一的比拼了。誰能最終獲勝呢?SAR ADC 的特點是體形較大(采樣和保持電路),速度較快,決定性較弱;而∑△ADC 則屬于輕量級選手,其采用了集成電路以及科學的方法和準確的思考進程。

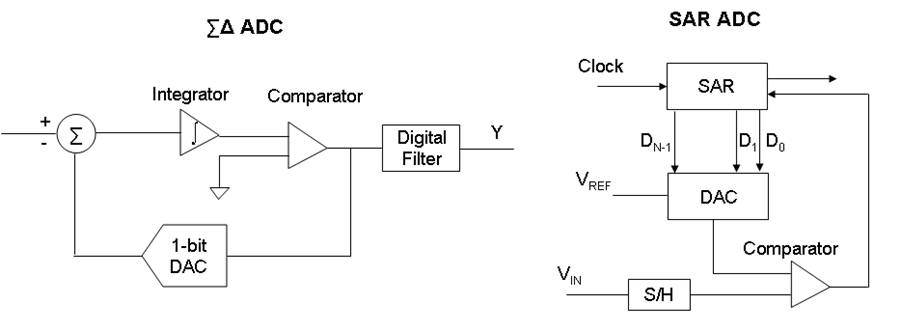

圖 1:∑△ 和 SAR 拓撲

圖中文字:integrator:積分器

comparator:比較器

digital filter:數字濾波器

clock:時鐘

第一輪:轉換準確性

準確性是由增益誤差和非線性決定的。我們在這一輪在討論的是增益誤差,非線性問題將在第五輪和第六輪比拼中討論。

增益誤差有兩種。刻度 (scale) 信號誤差是由參照差異以及輸入和 ADC 之間增益通道的差異造成的,誤差的大小與信號強弱相關。偏置誤差是由輸入放大器中的輸入器件以及 ADC 積分電路/比較器中使用的運算放大器造成的。

我們在圖 1 中可看到∑△的調制器(積分器、比較器和 1 位 DAC)和數字濾波器。∑△ADC 可在其前端包含可選的增益放大器。改變放大器的增益會改變輸入采樣電容的大小。由于采樣電容存在差異,因此增益不會是絕對精確的,需要 ADC 校準。為了糾正偏置和增益誤差,我們要根據零轉換、正滿刻度轉換和負滿刻度轉換結果獲得校準因數。

另一方面,SAR ADC 的轉換準確性取決于電壓參照、內部 DAC 和比較器。ADC 的內部 DAC 和比較器的準確性應和整體系統一樣,任何的不準確都會導致線性誤差,而這是校準所不能解決的。

在第一輪中,∑△ADC因其自身的單調性而勝出。

第二輪:轉換速度

∑△轉換器需要 2n 個采樣來完成轉換,因此轉換速度取決于轉換器的分辨率。分辨率越高,需要的轉換時間就越長。數字音頻設備通常使用的傳統∑△轉換器帶寬約 22kHz。近期,帶寬達 1MHz ~ 2MHz、分辨率達 12 ~ 20 位的∑△轉換器已經上市,這些轉換器通常包含四級(乃至更高)∑△調制器,而且支持多位反饋 DAC。

在SAR ADC 轉換周期開始時,DAC 設為半刻度,并對待測電壓和 DAC 輸出進行比較。DAC 在每一步進中都進行更新,選擇下一位并進行比較。我們通過二進制搜索(“逐次逼近”)來發現輸入電壓的數字形式。

SAR ADC在第二輪中因其轉換算法實際速度較高而勝出。

第三輪:攻擊線性

差動非線性 (DNL) 和積分非線性 (INL) 這兩種形式的非線性都取決于拓撲和轉換器的構造。DNL 和 INL 誤差不能像增益和偏置誤差一樣通過校準解決。

∑△ADC 的準確性取決于積分電路/比較器中運算放大器的穩定性。如果調制器切換太快,而運算放大器不能保持同步,則會出現非線性問題。

不管分辨率達到多少位,∑△ADC 本身都是單調性的。其性能是固定的,并不取決于具體的組件值或組件匹配。

就 SAR ADC 而言,線性誤差是由內部 DAC 和比較器的準確性不高造成的。線性誤差是 SAR 設計的副效應。

第三輪的勝出者是∑△ADC。

第四輪:高低壓側的轉換準確性

∑△轉換器提高了特定輸出代碼的非線性,這取決于抽取器中所用的 FIR 濾波器。這種非線性主要出現在刻度端點上。端點非線性對持續數據流(如數字音頻)不構成問題,但系統如果需要軌到軌線性檢測,則不應使用 ∑△轉換器。

SAR ADC 不會出現較大的∑△轉換器高低壓側端點不準確性問題。其端點準確性取決于內部 DAC 和比較器的軌到軌跟蹤(電壓合規)。

SAR ADC在第四輪在因其高低壓側的準確度較高而勝出。

第五輪:差動非線性

差動非線性誤差是指實際步進和 1 LSB 理想值之間的差異。因此,如果步長或高剛好為 1 LSB,那么差動非線性誤差就為零。如果 DNL 超過 1 LSB,則轉換器可能是非單片的,這就意味著輸出強度會下降,而輸入強度上升。在 ADC 中,也可能出現丟失代碼的問題,如一個或多個 2n 二進制代碼無法輸出。

不管分辨率達到多少位,∑△ADC本身都是單調性的。其性能是固定的,并不取決于具體的組件值或組件匹配。

SAR ADC 本身不是單調性的,其性能取決于具體的組件值或組件匹配。

第五輪的勝出者是∑△ADC。

第六輪:積分非線性

積分非線性誤差體現為實際轉換函數與直線之間的偏差。直線可以是可盡可能降低偏差的最佳直線,也可以是增益和偏置誤差取消后在轉換函數端點之間所畫的直線。對 ADC 而言,偏差是兩個步進之差,積分非線性顧名思義就是指從下至特定步進的差動非線性之和,其決定著步進的積分非線性值。

第六輪的勝出者是∑△ADC。其設計并不取決于具體的組件匹配或組件值。SAR ADC則需要高度準確的DAC和比較器。

第七輪:量化誤差

量化誤差是由 ADC 有限的分辨率造成的,也是各種類型 ADC 所無法避免的缺陷。它是 ADC 模擬輸入電壓和輸出數字化值之間的化整誤差。噪聲就是非線性的,并從屬于信號。

∑△轉換器不需要抗混濾波器,由于采樣率大大高于有效帶寬,因此模擬輸入處會出現驟降。過采樣會平衡掉模擬輸入處的任何系統噪聲。∑△轉換器的速度較慢,但分辨率較高。

SAR ADC的主要優勢在于低功耗、高分辨率和準確性。在SAR ADC中,提高分辨率會增加更為準確的內部組件成本。

盡管∑△ADC 在多輪比拼中獲勝,但評委還是認為二者基本打平。兩種轉換器在特定應用中的表現很好,因此必須根據量化信號、轉換速度、轉換準確性和價格來選擇∑△或SAR ADC。二者都有其用武之地。

讓我們從錦標賽的比拼中返回到現實的模擬領域。顯而易見,在消費、汽車、醫療、到工業等各種應用中,必須檢測、放大、調節和轉換各種感應器采集的模擬信號,從而實現在數字領域中對其加以處理。SAR和DelSig 各有優缺點,設計人員需根據不同的具體應用要求加以選擇。毫無疑問,這兩種轉換器在不同領域都能發揮出各自的效用,而賽普拉斯半導體公司 PSoC 產品近期提供的可編程模擬系統帶來了一款靈活的平臺,設計人員可用其來構建多個 SAR、DelSig,甚至同時構建SAR和DelSig。

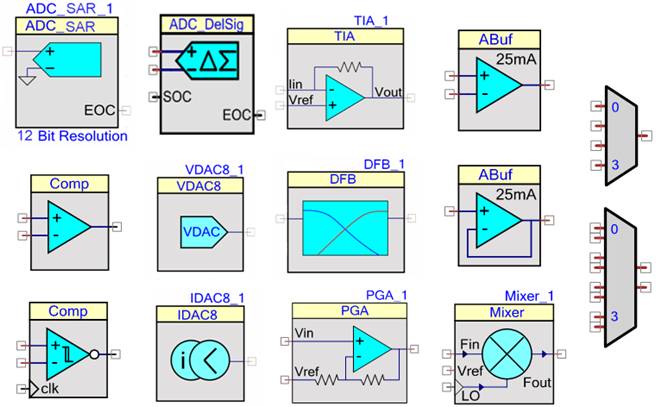

我們從圖 # 看出,軟件開發工具 PSoC Creator 組件庫——包括能在獨特軟硬件協同設計環境中配置 PSoC 器件的圖形設計編輯器在內的集成開發環境 (IDE)——中提供了模擬符號。模擬可編程系統創建標準和高級模擬信號處理塊的專用組合。這些塊彼此互聯,可提供高度的設計靈活性和 IP 安全性。PSoC Creator 軟件程序提供了用戶友好型界面,可配置 GPIO 和多種模擬資源之間的模擬連接,也能配置模擬資源彼此之間的連接,從而幫助設計人員構建自己的組件,如一般包括 DAC、比較器和數字邏輯的 SAR ADC(圖 #)。

可編程模擬不僅能實現可在最后時刻進行方案調整的靈活開發,同時還提供了一個適當的平臺。無論金手套錦標賽中的勝負如何,設計人員均能借助該平臺進行各種嘗試并操控不同領域的各種分離式模擬組件,進而構建最佳的系統。

評論