基于FPGA的高壓變頻器中性點(diǎn)偏移技術(shù)的算法實(shí)現(xiàn)

0 引言

本文引用地址:http://www.104case.com/article/201808/387240.htm在高壓變頻器正常運(yùn)行過程中,如果功率單元出現(xiàn)故障,一般的實(shí)現(xiàn)方法是將此故障功率單元旁通,同時(shí)讓其它兩相相應(yīng)的功率單元也同時(shí)旁通,這樣使變頻器A、B、C 三相輸出相電壓相等,從而保證線電壓相等,使電機(jī)的三相電流平衡。但是在旁通過程中,由于同時(shí)旁通掉3個(gè)功率單元,所以電流沖擊較大,可能造成系統(tǒng)過流停機(jī)。并且在旁通后高壓變頻器的輸出功率降低較多,因此使電機(jī)輸出功率減小。

1 中性點(diǎn)偏移技術(shù)原理分析

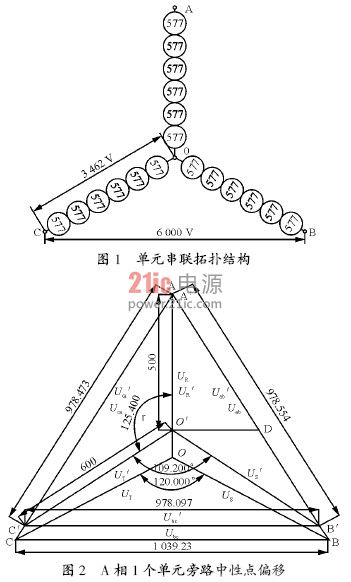

目前國內(nèi)生產(chǎn)的高壓變頻器大多采用功率單元串聯(lián)疊加多電平,VVVF控制方式。其拓?fù)浣Y(jié)構(gòu)如圖1 所示。A、B、C三相各6 個(gè)功率單元,每個(gè)功率單元輸出電壓為577 V,相電壓UAO=UBO=UCO=3 462 V,線電壓UAB=UBC=UCA=6 000 V。如果出現(xiàn)任意1 個(gè)功率單元故障旁通時(shí),勢必造成系統(tǒng)不平衡,從而導(dǎo)致系統(tǒng)停機(jī)。經(jīng)過公司研發(fā)人員的理論推導(dǎo)及技術(shù)分析,提出了“中性點(diǎn)偏移”的方法。

如圖2(此圖按照等比例1頤5.77所繪)所示,如果A 相有一個(gè)功率單元故障旁通掉,中性點(diǎn)由O偏移到O憶(虛擬中性點(diǎn)),經(jīng)過運(yùn)算,線電壓由原來的1 039.23 V(1 039.23伊5.77=5 996 V)變?yōu)?78.5 V(978.5伊5.77=5 646),相角度由120毅變?yōu)?25.4毅和109.2毅。雖然相電壓不相等,但是輸出的線電壓保持相等。這樣就保證了電機(jī)的三相電流平衡。同理如果出現(xiàn)2 個(gè)或3 個(gè)單元旁通時(shí),經(jīng)過復(fù)雜運(yùn)算,也可實(shí)現(xiàn)中性點(diǎn)偏移,從而保證輸出的線電壓相等。

2 FPGA 中各種功能模塊的算法實(shí)現(xiàn)

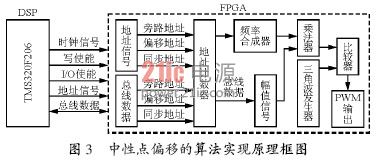

中性點(diǎn)偏移的算法實(shí)現(xiàn),主要是通過現(xiàn)場可編程門陣列(FPGA)和數(shù)字信號(hào)處理器(DSP)來實(shí)現(xiàn)的。DSP 主要采集功率單元的故障信息并進(jìn)行處理后,發(fā)出旁通信號(hào)、地址和數(shù)據(jù)信號(hào)給FPGA。

FPGA收到這些數(shù)據(jù)后,做相應(yīng)處理。中性點(diǎn)偏移的算法實(shí)現(xiàn)原理框圖如圖3所示。其中,DSP采用TI 公司的TMS320F206,F(xiàn)PGA 采用Altera 公司的EP1C6Q240C8。

2.1 芯片簡介

TMS320F206 是TI 公司推出的一種DSP 芯片,它是基于TMS320C5x 之上的高速定點(diǎn)數(shù)字處理芯片,具有改進(jìn)的哈佛結(jié)構(gòu)(程序總線和數(shù)據(jù)總線分離)、高性能CPU及高效的指令集等特點(diǎn)。其主要特性有:CPU具有32 位CALU、32 位累加器、16伊16 位并行乘法器、3 個(gè)移位寄存器、8 個(gè)16 位輔助寄存器。存儲(chǔ)器具有224 kB 可尋址存儲(chǔ)空間、544 B片內(nèi)DRAM、4 kB 片內(nèi)SRAM 或32 kB片內(nèi)快閃存儲(chǔ)器。指令速度可達(dá)25 ns單指令周期。外圍電路有軟件可編程定時(shí)器、軟件可編程等待狀態(tài)發(fā)生器、片內(nèi)鎖相環(huán)時(shí)鐘發(fā)生器、同步和異步系列串口等。

EP1C6Q240C8是Altera 公司推出的主流低成本FPGA-Cyclone系列。Cyclone器件采用0.13 滋m的工藝制造,其內(nèi)部有2 個(gè)鎖相環(huán)(PLL)、20 個(gè)M4K RAM塊、具有5 980個(gè)LE 的邏輯容量、最大用戶I/O 為185、支持高速LVDS 接口,性能可達(dá)到311 Mb/s。

2.2 DSP數(shù)據(jù)處理

當(dāng)故障信號(hào)(包括IGBT過流,直流過壓,無PWM信號(hào)等)上傳到DSP 中時(shí),DSP對(duì)故障位進(jìn)行判斷,封鎖相應(yīng)故障功率單元的PWM 信號(hào),然后執(zhí)行旁通程序,對(duì)每個(gè)功率單元按順序進(jìn)行掃描,對(duì)有故障的功率單元進(jìn)行記憶,然后發(fā)出旁通命令及對(duì)應(yīng)的旁通地址和相應(yīng)數(shù)據(jù)。

2.3 地址信號(hào)編碼和總線數(shù)據(jù)處理

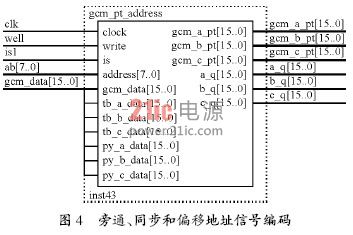

地址信號(hào)分為旁通地址、同步地址、偏移地址,均通過ab[7..0]實(shí)現(xiàn)。旁通時(shí)A、B、C 三相分別對(duì)應(yīng)一個(gè)地址。通過此地址DSP 向FPGA 發(fā)送旁通命令、同步數(shù)據(jù)及偏移數(shù)據(jù)。地址信號(hào)編碼如圖4 所示。

總線數(shù)據(jù)包括旁通命令位、同步數(shù)據(jù)量、偏移數(shù)據(jù)量,通過數(shù)據(jù)總線gcm_data[15..0]來接收,A、B、C 三相分別對(duì)應(yīng)一個(gè)地址。在相應(yīng)地址選通后,DSP 向FPGA 寫數(shù)據(jù),由FPGA 來保存這些數(shù)據(jù),在數(shù)據(jù)用完后進(jìn)行清零。如圖4 所示,旁通輸出數(shù)據(jù)為gcm_a_pt_ [15..0]、gcm_b_pt_[15..0]、gcm_c_pt_[15..0],同步和偏移輸出數(shù)據(jù)信號(hào)為a_q[15..0]、b_q[15..0]、c_q[15..0]。

在FPGA 中用于查表的地址數(shù)據(jù)主要用于正弦波查表,改變此地址可生成不同頻率的正弦波形。如圖4 所示的ab[7..0]有效時(shí),改變gcm_data[15..0] 的值可以產(chǎn)生不同的地址信號(hào)a_q[15..0]、b_q[15..0]、c_q[15..0],此三個(gè)地址信號(hào)用于正弦波查表的地址輸入值。

評(píng)論