結合FPGA與結構化ASIC進行設計

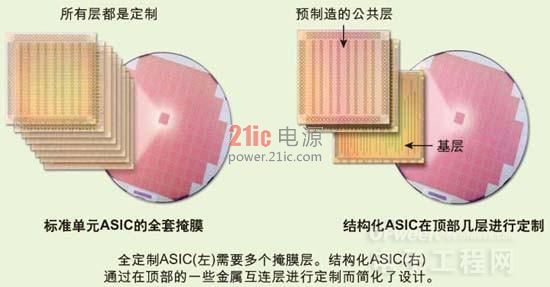

由于結構化ASIC具有單位成本低、功耗低、性能高和轉換快(fast turnaound)等特點,越來越多的先進系統設計工程師正在考慮予以采用。在結構化ASIC中,像通用邏輯門、存儲器、鎖相環和I/O緩存這些功能性資源都嵌在芯片內部經過預設計和預驗證的基層中。然后,該層和頂部少數金屬互聯層一起完成定制。比起從頭開始創建ASIC來說,這種方法可大幅縮短設計時間。

本文引用地址:http://www.104case.com/article/201808/386945.htm僅在芯片少數金屬層上配置電路,不僅可以降低開發成本和縮短開發時間,而且降低了設計錯誤發生的風險。這是因為與ASIC需要設計許多掩膜層來構成芯片相比,結構化ASIC供應商只需要生成相對簡單的金屬層。

然而,利用結構化ASIC進行開發也不是沒有風險。邏輯設計錯誤仍然可能存在。避免硅片設計反工的一種方法是使用FPGA作原型,然后將設計從FPGA轉換成ASIC。

與標準單元ASIC相比,當結構化ASIC鏡像FPGA上的可用資源時,針對結構化ASIC的FPGA原型更加成功。右文是使用結構化ASIC設計方法學的一些建議。

建議

1. 針對一定范圍內的應用確立一種設計方法學。要確保你的設計團隊受過有關工具和FPGA、ASIC架構的良好培訓,以便能夠構建最佳設計。

2. 利用軟件開發環境,以此降低產生功能性邏輯錯誤等設計問題的風險。使用邏輯驗證和仿真以及FPGA原型設計是行之有效的方法。

3. 利用那些能提供給你最佳性能和功能的FPGA特性進行FPGA原型設計。同時,利用應用所需的知識產權創建原型。

4. 盡可能在系統內檢測你的設計,驗證它是否符合設計要求。同時,要確保在所有要經歷的電壓和溫度范圍下利用FPGA原型對該系統進行了全面檢測。

5. 使用FPGA或結構化ASIC進行系統設計。這種方法能實現兩個目標。第一,你可以將FPGA投入生產并且將其轉變為ASIC。這使得該系統能更快地進入市場。第二,如果對于ASIC有突然增加的需求而供應又不足時,就能夠生產一些使用FPGA的系統。

不建議

1. 使用FPGA只對邏輯和低級I/O(例如LVTTL或者LVCMOS)進行原型設計。這會使得你的設計局限在低端門陣列,從而無法提供高性能。通常,FPGA中只有邏輯進行原型設計,這將導致錯誤理解設計在系統中工作的好壞。許多設計還需要高速存儲接口。最好對其進行原型設計,以確保接口按需求工作,特別是在電壓和溫度變化下能正常工作。

2. 只根據單位成本而選擇ASIC方法學。這種選擇可能會節省一些物料清單(BOM)成本,但考慮到整個工程計劃的實際開發時間和成本等因素,系統將失去競爭力。從長遠看,FPGA和結構化ASIC能降低開發成本,縮短開發周期。

3. 對于專用標準產品(ASSP)的設計只考慮采用標準單元ASIC技術。考慮到年產量和產品最快面市的需求,有時候結構化ASIC或甚至FPGA才是最佳選擇。

4. 在了解清楚設計的市場需求之前就貿然選擇結構化ASIC。當你試圖強行把一個設計放入太小或性能受限的結構化ASIC中時,該系統在市場上將直接面臨生死考驗(DOA)。

5. 只考慮單芯片解決方案。有時,構建系統的最好方法是采用兩個器件而不是一個大規模ASIC。將設計分割開來,可以縮短整體開發時間、簡化設計流程,還能降低設計反工的危險。

評論