基于Zynq的圖形生成電路設(shè)計與實現(xiàn)

導(dǎo)讀: 為了適應(yīng)機載液晶顯示器向低功耗、高集成度發(fā)展的趨勢,提出了一種基于Zynq可擴展處理平臺的圖形生成電路實現(xiàn)方法。

本文引用地址:http://www.104case.com/article/201808/386777.htm

摘要:為了適應(yīng)機載液晶顯示器向低功耗、高集成度發(fā)展的趨勢,提出了一種基于Zynq可擴展處理平臺的圖形生成電路實現(xiàn)方法。方法以Zynq為核心搭建硬件平臺,使用Zynq集成的ARM 處理器執(zhí)行圖形生成算法運算,配合可編程邏輯資源,按照一種三緩沖機制對DDR3SDRAM 幀存數(shù)據(jù)進行緩沖處理,實現(xiàn)圖形的實時生成.采用本設(shè)計可以生成多種分辨率的機載圖形畫面.實驗結(jié)果表明,當(dāng)生成分辨率為1024×768的EFIS電子飛行顯示系統(tǒng)畫面時,幀率可達74fps,能夠滿足機載液晶顯示器高性能實時顯示需求。

1 引言

在飛機座艙顯示系統(tǒng)中圖形顯示占據(jù)重要地位[1].主顯示器尺寸不斷加大,分辨率不斷提高,并日益朝著大屏幕化、綜合化、信息化和智能化方向發(fā)展[2].隨著分辨率的提高,要顯示的信息量也大幅增加,座艙圖形綜合顯示系統(tǒng)是一個對實時性要求很高的系統(tǒng)[3],軍用飛機在做戰(zhàn)術(shù)動作時,畫面變換速度快,要求圖形的更新速度也必須很快,至少要比幀或場的刷新速度快,才可以避免畫面的斷續(xù)[4G5].采用DSP+FPGA 的圖形硬件加速架構(gòu),或者使用專用GPU 圖形生成芯片,都可以生成高分辨的機載顯示器圖形,但隨之而來的是產(chǎn)品成本的急劇增加以及功耗的不斷上升[6].為機載圖形顯示系統(tǒng)配置更合理的硬件設(shè)計和軟件架構(gòu)變得尤為迫切。

Xilinx最新平臺Zynq將處理器的軟件可編程能力與FPGA 的硬件可編程能力實現(xiàn)完美結(jié)合,以低功耗和低成本等系統(tǒng)優(yōu)勢實現(xiàn)良好的系統(tǒng)性能、靈活性和可擴展性[7].本文提出一種基于Zynq可擴展處理平臺的實時圖形生成電路,利用Zynq內(nèi)部集成的ARM 處理器以及可編程邏輯資源,實現(xiàn)了機載顯示器圖形畫面的實時生成與顯示。

2 Zynq簡介

2.1 Zynq構(gòu)成

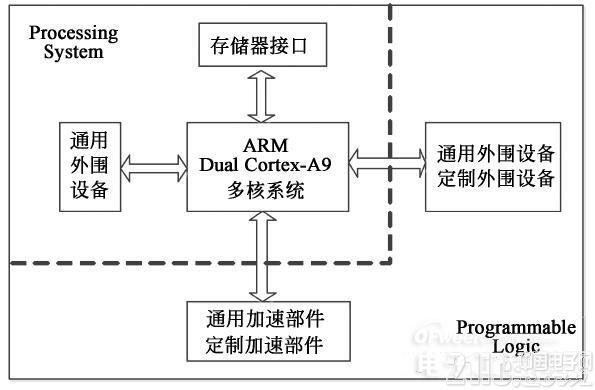

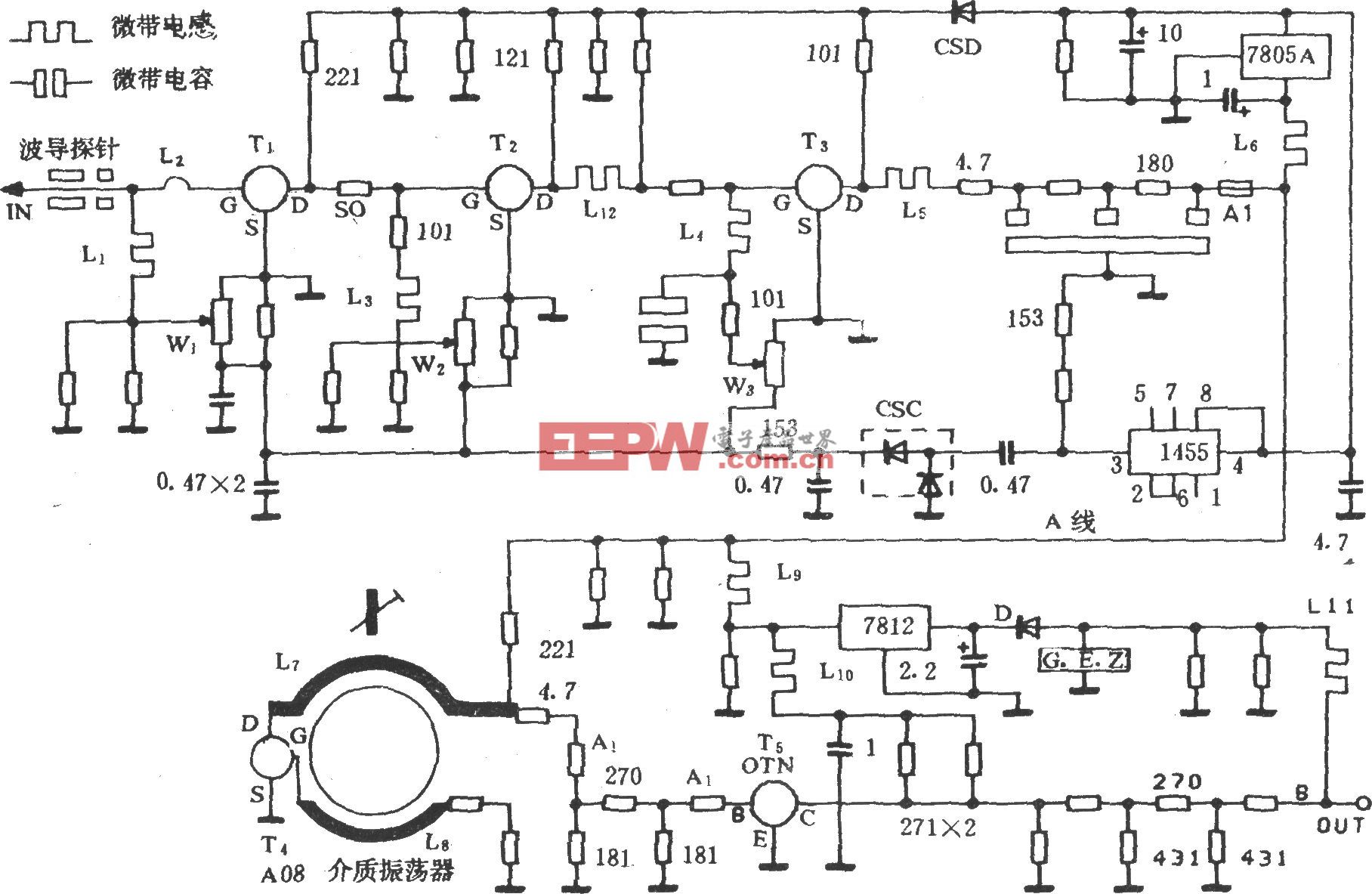

Zynq構(gòu)架將內(nèi)部結(jié)構(gòu)分為處理器系統(tǒng)(ProcessingSystem,PS)與可編程邏輯(ProgrammableLogic,PL)兩部分[8].PS部分包括雙ARM CortexGA9內(nèi)核、存儲器接口以及通用外設(shè)接口等資源.PL部分也即常規(guī)的FPGA,通過PL生成的IP核可以作為ARM 內(nèi)核的擴展外圍設(shè)備或者ARM 內(nèi)核的加速部件.Zynq器件內(nèi)部結(jié)構(gòu)圖如圖1所示。

圖1 Zynq內(nèi)部結(jié)構(gòu)圖

Zynq架構(gòu)可以對PL和PS中運行的自定義邏輯和軟件方便地進行管理和規(guī)劃,PS和PL的單芯片綜合使其在I/O 數(shù)據(jù)帶寬、功能耦合、功耗預(yù)算等方面的性能表現(xiàn)大大超越了以往ASSP和FPGA 雙芯片解決方案。

PS和PL可以通過多種途徑實現(xiàn)互聯(lián),包括GPIO端口、AXI總線端口、EMIO 端口、中斷、DMA 等等.其中AXI總線是ARM 系統(tǒng)中連接各個模塊的主要通道,各個功能部件通過AXI總線實現(xiàn)互聯(lián).在PL中可以通過工具自動生成帶有AXI接口的IP 核,和PS 端進行高速數(shù)據(jù)交互。

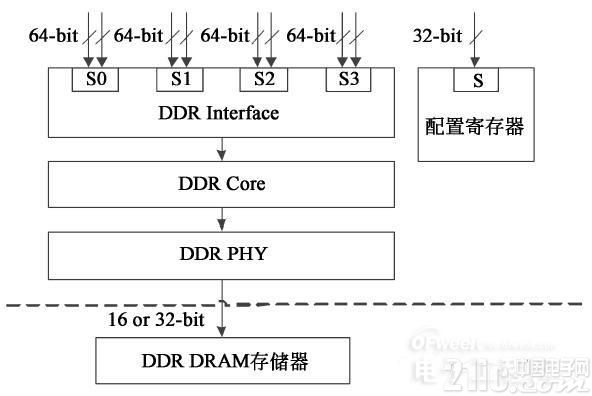

2.2 DDR Memory控制器

Zynq內(nèi)部集成的DDR memory控制器支持DDR2、DDR3、LPDDR2等多種存儲器類型,包含了3個主要模塊:AXI存儲器端接口DDRI、帶有傳輸調(diào)度機制的中央控制器DDRC 和物理層控制器DDRP[9].DDRmemory控制器框圖如圖2所示。

圖2 DDR Memory控制器框圖

DDRI端口符合AXI總線標(biāo)準(zhǔn),包含4個64位的同步AXI接口,分別為S0、S1、S2、S3,用于接收多個AXI主端的訪問請求,其中S0和S1端口接收PS部分CPU 的訪問請求;S2和S3端口接收PL部分邏輯端的訪問請求.DDRC對來自多個AXI主端的訪問請求按照其調(diào)度策略進行裁決,裁決實施的依據(jù)是主控端訪問的優(yōu)先級、等待時長計數(shù)器和緊急信號.DDRP 處理來自于DDRC的讀寫請求,并將其轉(zhuǎn)換成符合DDR 存儲器時序要求的特定信號。

2.3 AXI VDMA

AXI VDMA 是Xilinx公司開發(fā)的一個軟核IP,用于在系統(tǒng)存儲器和支持AXI4-Stream 視頻類型的目標(biāo)IP之間提供一個高速的數(shù)據(jù)存取通道[10].AXI4-Stream 格式數(shù)據(jù)流不能直接用于驅(qū)動顯示,還需要將數(shù)據(jù)流以視頻使能信號為界進行分割,配合行場同步信號驅(qū)動視頻終端顯示。

該IP 有兩路AXI4-Stream 接口,分別為AXI Memory Map to Stream (MM2S)Stream Master 和AXI4-Stream to Memory Map(S2MM)Stream Slave,其中MM2S為主端口,用于輸出轉(zhuǎn)換成AXI4-Stream 格式視頻流的系統(tǒng)存儲器中數(shù)據(jù).S2MM 為從端口,用于接收AXI4-Stream 格式視頻流轉(zhuǎn)換成存儲器數(shù)據(jù).MM2S和S2MM 彼此相互獨立,可以并行同時工作.PS端的處理器可通過AXI4-Lite總線對其內(nèi)部的寄存器進行訪問以控制VDMA 工作模式、獲取VDMA 工作狀態(tài)。

3 設(shè)計實現(xiàn)

3.1 硬件設(shè)計

3.1.1 硬件架構(gòu)

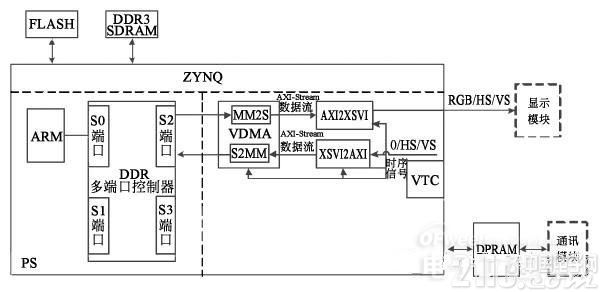

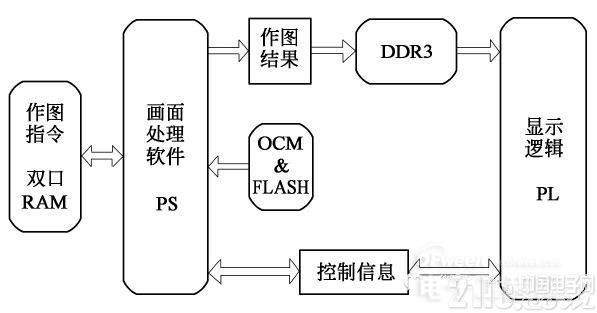

本文通過Zynq完成圖形生成與顯示功能,原理框圖如圖3所示,硬件模塊主要包括Zynq、DDR3SDRAM、FLASH、雙口RAM 等.正常工作時PS中的ARM 內(nèi)核根據(jù)從雙口RAM 中接收到的繪圖指令和參數(shù)完成繪圖算法,將圖形數(shù)據(jù)寫入DDR3SDRAM 存儲器中.PL 從DDR3中讀出圖形數(shù)據(jù)進行顯示,并對DDR3SDRAM中的圖形數(shù)據(jù)進行清屏處理。

圖3 Zynq圖形生成原理框圖

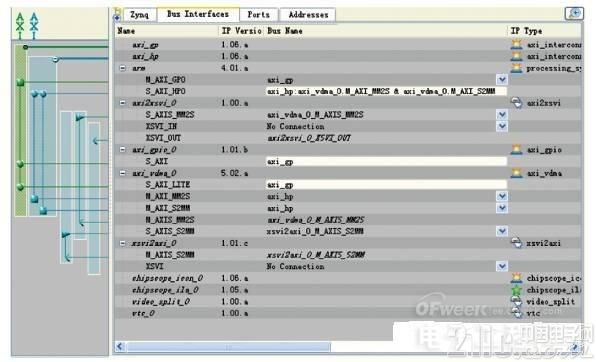

3.1.2 Zynq硬件平臺設(shè)計

本文通過Xilinx 的ISE14.2 軟件集成的XPS開發(fā)環(huán)境完成Zynq圖形生成電路的硬件平臺設(shè)計.利用XPS可以快速地對Zynq系統(tǒng)內(nèi)的各種硬件資源進行定制設(shè)計,包括存儲器、外設(shè)、ARM 處理器、系統(tǒng)IP和用戶IP等.Zynq硬件平臺結(jié)構(gòu)圖見圖4所示.

圖4 Zynq硬件結(jié)構(gòu)圖

本文在Zynq中的PL 部分應(yīng)用了VDMA、AXI2XSVI、XSVI2AXI、VTC等幾個IP核,其中VDMA 用于從DDR3SDRAM 中讀出圖形數(shù)據(jù),同時向DDR3SDRAM 中寫入全零數(shù)據(jù)以達到清屏目的.AXI2XSVI用于將AXIGStream 數(shù)據(jù)流用行、場同步信號進行區(qū)隔,供外部顯示模塊進行顯示.XSVI2AXI用于將帶有行場同步信號的視頻數(shù)據(jù)轉(zhuǎn)換成AXIGStream 數(shù)據(jù)流.VTC 用于生成系統(tǒng)運行所需時序信號.對VTC根據(jù)顯示時序進行修改,系統(tǒng)即可產(chǎn)生多種分辨率圖形畫面。

3.1.3 圖形緩沖設(shè)計

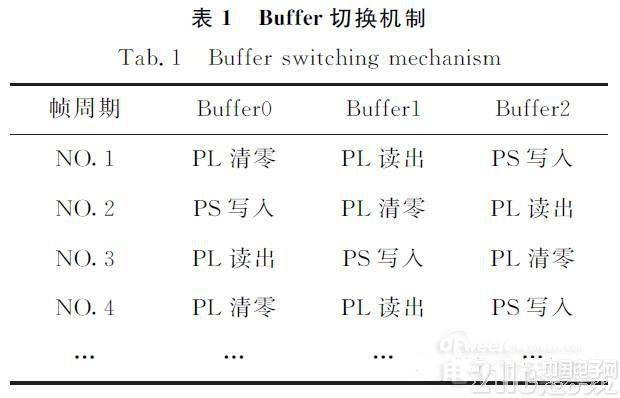

本文中對DDR3SDRAM 幀存的操作包括3種類型:PS寫入、PL讀取、PL清零.清零從本質(zhì)上說也是一種寫入操作,寫入的是全零數(shù)據(jù).讀取和寫入請求通過DDR 控制器中的調(diào)度機制和仲裁策略分別在不同時刻得以響應(yīng),得益于DDR3SDRAM 的高速高帶寬優(yōu)勢,外部可以同時進行多個通道的讀寫操作.針對本文中DDR3SDRAM 的3種操作類型,在DDR3幀存中設(shè)置了3個緩沖區(qū),分別為buffer0,buffer1,buffer2,相應(yīng)地,VDMA 中的framebuffer數(shù)目也設(shè)置為3.buffer的切換機制如表1所示.

這種三緩沖切換機制保證了寫入的都是已清零完成的buffer,清零的都是已讀出完成的buffer,讀出的都是已寫入完成的buffer。

根據(jù)buffer切換機制,VDMA 中的S2MM和MM2S通道分別以指定的buffer為操作對象.初始化狀態(tài)下為每個buffer指定默認(rèn)的操作模式,而后在每個幀周期內(nèi)啟動VDMA 切換buffer操作模式,從而不間斷地輸出圖形數(shù)據(jù)。

3.2 軟件設(shè)計

3.2.1 Zynq系統(tǒng)軟件

系統(tǒng)繪圖時,根據(jù)雙口RAM 提供的畫面內(nèi)容要求,啟動繪圖任務(wù),并將繪圖結(jié)果保存下來.顯示工作完全由PL內(nèi)部的顯示邏輯負(fù)責(zé),顯示邏輯從顯存中讀取顯示數(shù)據(jù),按照標(biāo)準(zhǔn)時序送至顯示接口.圖形軟件的接口關(guān)系如圖5所示.

圖5 圖形生成軟件接口示意圖

評論