基于DSP的SoC芯片的FPGA驗證方法

引 言

本文引用地址:http://www.104case.com/article/201808/386477.htmDSP 技術廣泛地應用于數字信號處理領域, 它或者以獨立的器件形式在系統中出現, 或者以IP 核的形式嵌入SoC系統中。而隨著集成電路技術的發展以及EDA 設計水平的迅速提高, 基于IP( Intellectual Property) 進行SoC(System on Chip)芯片設計的能力和技術得到了大大的提高。在一些應用方面,需要處理的數據量不斷增大以及數據處理時間縮短,數據運算更加復雜,內嵌DSP核處理器的SoC技術能夠提高處理時間精確性并能進行大數據量的處理,提高可靠性, 縮小體積,降低功耗。因此本論文設計研究一種基于DSP的SoC芯片的FPGA驗證方法,并將整個系統包括DSP處理器、片上總線、ASIC、內存模塊和I/O 外圍設備及其他IP模塊集成到一個芯片中。 而在復雜的內嵌DSP核的SoC 芯片的系統設計中, 為了保證SoC芯片設計的正確性, 驗證工作變得越來越重要, 也更加復雜。FPGA驗證是復雜芯片和SoC芯片設計驗證的一種有效手段,可以彌補軟件模擬仿真的不足,減少驗證時間,檢驗SoC的設計是否實現了設計規范確定的功能,從而提高SoC芯片流片成功率。

1 基于DSP核控制的SoC系統

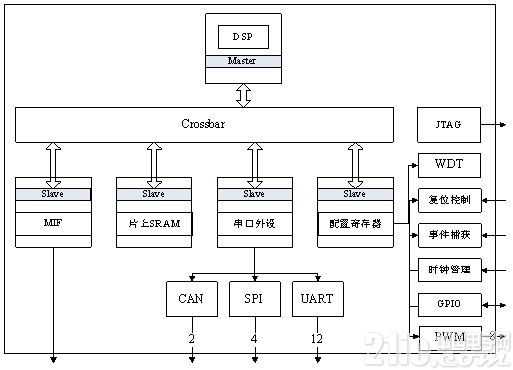

本論文設計的SoC系統采用國內自主研發DSP核 ,而基于DSP設計的SoC系統主要包括: DSP 處理器核、片上AXI總線、PWM、事件捕獲器、看門狗控制、中斷控制器、復位管理、存儲模塊、I/O及其他外設UART、CAN、SPI等模塊。這些模塊與DSP核之間通過AXI總線連接,進行數據通信。AMBA AXI的總線協議具有高性能、支持高頻傳輸、高速亞微型系統互連的特征。AXI協議是主從結構的,一切觸發都由主設備發起。核間通信總線采用實際SoC系統中應用最多的AXI總線結構,比較靈活,可滿足對帶寬需求高低不同的各種IP。

基于DSP的SOC系統結構框圖如圖1所示。

圖1 基于DSP的SOC系統架構

2 SoC系統的FPGA驗證平臺

FPGA驗證平臺用于SoC芯片驗證,對于大規模SoC系統的設計進行快速準確地實時驗證,根據不同SoC規模容量,采用不同的FPGA硬件資源,硬件平臺建設有所不同。由于FPGA具有靜態可編程和在線動態重構特性,能夠使硬件的功能電路同軟件程序一樣方便修改,使得FPGA驗證修改十分便利易操作,實時性較好;還可以縮短開發周期,節約時間,降低開發成本;FPGA具有的這些特點使得FPGA成為通用的SoC功能驗證的器件,為SoC的系統原型驗證提供了一個非常合適的平臺。FPGA器件在SoC驗證設計中的應用越來越廣泛。目前FPGA已經從系統集成、系統存儲、系統時鐘和系統接口四個方面滿足了SoC芯片驗證的要求,為SoC芯片的快速系統原型驗證提供了一個非常合適的平臺。此基于DSP的SoC系統的FPGA驗證平臺采用Xilinx Virtex-6 LX760器件,是建立在Xilinx Virtex6 FPGA板上的軟硬件聯合驗證系統,并用ISE13.3進行綜合和布局布線。另外此FPGA硬件驗證平臺包括支持DSP程序下載的JTAG通路及接口。

2.1 FPGA 硬件平臺建設

關于硬件平臺搭建主要使用了兩顆Xilinx Virtex-6 LX760 FPGA器件,雙FPGA Virtex-6核具有15.2M 邏輯門的邏輯資源。Virtex-6 LX760是面向于高端應用,具有更多的時鐘和存儲資源,而且能夠支持運行更快的速度。通過分析所選擇FPAG具備資源滿足此SoC驗證使用,為了實現通用性,該FPGA硬件驗證平臺采用了子板和母板相結合的方式。在母板上設置有通用的FPGA芯片,相應的PROM,系統全局時鐘的選擇和配置模塊,系統復位邏輯,FPGA芯片下載通路,與子板連接的connector接口等模塊。子板根據基于DSP的SoC系統驗證需求,該FPGA硬件平臺設計的子卡配置了JTAG調試子板,以提供DSP仿真器連接的調試接口通路。另外還設計配置了驗證EMIF訪問外部存儲設備通路的SRAM存儲器子板。為了方便測試和驗證EMIF接口功能,在這兩類測試子板上,都設有關鍵信號的測試探測點,以方便測試一些基礎的時鐘、復位信號及其他探測信號。

2.2 FPGA 軟件環境建設

在SoC 設計中,經常會使用一些硬IP 核,如PLL、SRAM、ADC、USB transceiver 等,而在采用FPGA驗證技術驗證ASIC及SoC設計過程中,需要做ASIC的設計原碼的轉換。所以首先需要對SoC進行修改,以適合FPGA的開發環境。如門控的處理,添加PLL對所需要的時鐘進行適當的分/倍頻,存儲單元RAM、FIFO的替換,修改子模塊配置,特殊單元的處理等。還要根據特定的硬件平臺增加FPGA 相關的時序Timing的約束和IO引腳的指定約束,并搭建一個能夠自動仿真和驗證的環境。在此FPGA驗證過程中主要使用ISE13.3內置綜合工具或專用綜合工具對RTL進行編譯、綜合,生成網表。生成的網表以生成bit文件,包括優化、適配、bit文件生成等。進行靜態時序分析,檢查是否滿足預定的時鐘頻率要求,若不能滿足,則重新進行綜合編譯優化如果多次進行仍不能滿足時序要求,則根據違反時序信息查找關鍵路徑對RTL設計代碼進行修改優化。

基于DSP控制的SoC系統的FPGA驗證軟件除了需要上述提到的綜合布局布線的軟件環境ISE13.3外,還需要FPGA內部信號在線調試工具Chipscope,即時抓取一些內部邏輯信號分析內部邏輯正確與否。在驗證調試階段,還需要DSP核下載調試軟件CCS3.3以編寫控制處理器核DSP執行運行的軟件測試程序。

2.3 軟硬件協同驗證系統

FPGA驗證SoC系統方法是軟硬件協同仿真和驗證,并搭建軟硬件協同驗證平臺系統。基于FPGA的SoC驗證系統,即硬件平臺和軟件環境結合的驗證系統,已經成為SoC設計驗證流程中的重要方法和技術手段。實現的基礎條件常常是需要上述提出的能夠滿足工作要求的FPGA硬件平臺,以及有力的設計描述及編譯工具等軟件環境。而基于DSP控制的SoC驗證系統還需要DSP軟件程序開發環境及下載通路等。

2.3.1 FPGA軟硬件協同驗證架構

FPGA驗證是使設計的SoC系統及IP模塊硬件化,通過實現在具體的FPGA驗證平臺上運行及驗證,具體化設計研發的SoC系統及IP電路,彌補軟件仿真存在的差距。為了驗證的完整性與可靠性,采用FPGA硬件平臺和軟件環境建設的軟硬件協調驗證方法。

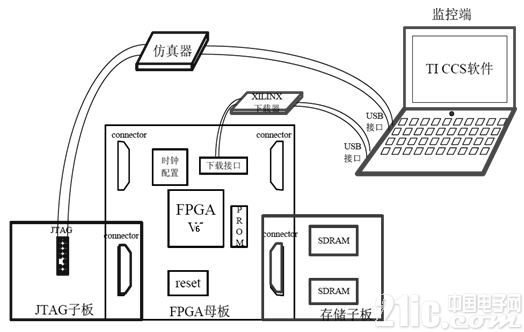

FPGA驗證是為了實現和驗證SoC芯片在實際硬件環境下的功能和運行工作情況。針對基于本文設計提出的基于DSP的SoC系統,搭建能夠實現和驗證其DSP程序指令及內部電路工作的軟硬件驗證系統平臺。建立的FPGA軟硬件協同驗證系統的基本架構如圖3所示。其中包括FPGA原型驗證需要的XILINX V6芯片的FPGA驗證母板、支持下載bit位文件及驗證調試過程中需要的XILINX FPGA 編程器及下載線、能夠支持正確下載DSP激勵測試程序的DSP-JTAG調試子板、支持DSP芯片的仿真器、安裝有TI CCS軟件和 ISE13.3 軟件及支持DSP芯片驅動的微機。

圖2 FPGA軟硬件協同驗證系統的基本架構

2.3.2 驗證過程

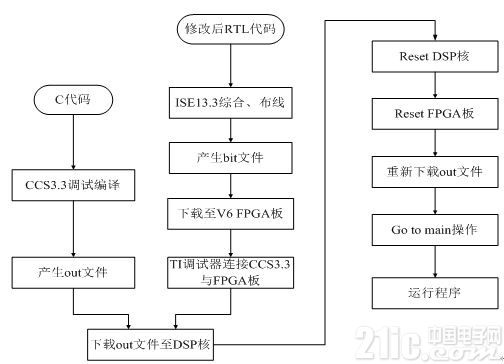

軟硬件協同驗證過程分以下幾個步驟(1)首先把要驗證的SoC系統經由ISE13.3自動綜合及布局布線實現后生成相應的FPGA位流文件經JTAG下載線下載至構建的FPGA驗證系統中的FPGA芯片或對應的PROM中。(2)通過微機CCS 界面編寫控制內部DSP核運行的程序,完成程序啟動初始化、測試激勵程序編譯,及開發驗證IP及系統需要的程序。(3)并通過DSP仿真器以實時的方式進行軟硬件協同驗證過程中的管理控制,通過編寫及測試程序的加載、運行、調試,實現對DSP核進行的單步操作、連續運行等操作;通過設置正確中斷服務程序、設置斷點、觀測DSP核內部寄存器及SoC配置寄存器值等分析DSP核運行及操作IP情況(4)透過不同的控制程序驅動運行相應功能IP模塊及整個系統工作運行,驗證IP功能及不同IP之間的交互和總線競爭。在驗證過程中可以根據IP功能及SoC系統特性使用示波器觀測引腳信號,使用ChipScope軟件抓取內部信號來判斷邏輯關系及系統運行的準確性。驗證DSP核、SoC系統及相應IP功能;驗證系統各模塊間的相互操作、片上系統內的數據相互流通功能;驗證所有IP集合協同運行情況;驗證整個系統。具體驗證流程圖可參見圖3

圖3 基于DSP的SoC系統的FPGA驗證流程圖

3 SoC系統及IP模塊功能驗證

對SoC系統及內部IP功能模塊進行驗證,需要首先驗證FPGA軟件平臺及硬件平臺正確性,才能在CCS環境下編寫控制DSP處理器的程序以驗證SoC系統設計及各個功能模塊的正確性。通過CCS編程器與FPGA硬件平臺連接正確后,可通過下載編寫控制DSP內核的程序,驗證DSP運行正確性,并通過編寫控制其他IP邏輯模塊驗證SoC系統內部交互及IP邏輯設計。其中主要進行了下面幾種功能模塊劃分及其驗證,通過驗證功能模塊也進一步驗證SoC系統及片上總線等設計的正確性。

評論