不用處理器控制FPGA總線的方法

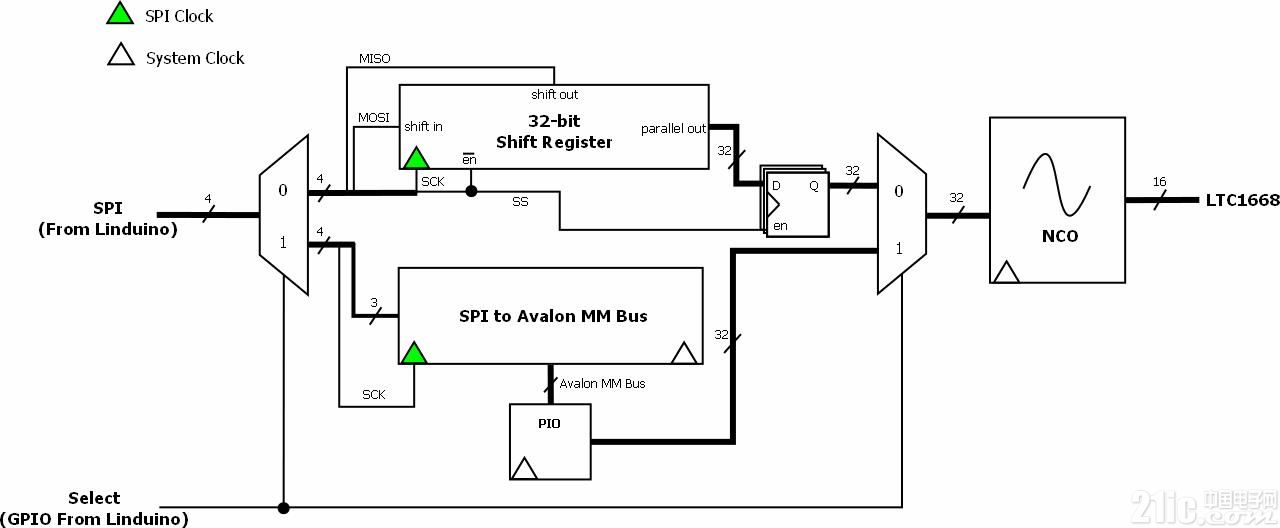

圖4顯示了系統框圖。注意,數字控制振蕩器(NCO)可以由移位寄存器或PIO內核進行控制。移位寄存器用于調試,因為它可以直接控制NCO。將GPIO線置高將激活SPI-Avalon橋,進而控制Avalon總線上的32位PIO端口。PIO輸出隨即用于控制NCO頻率。

圖4:FPGA系統框圖

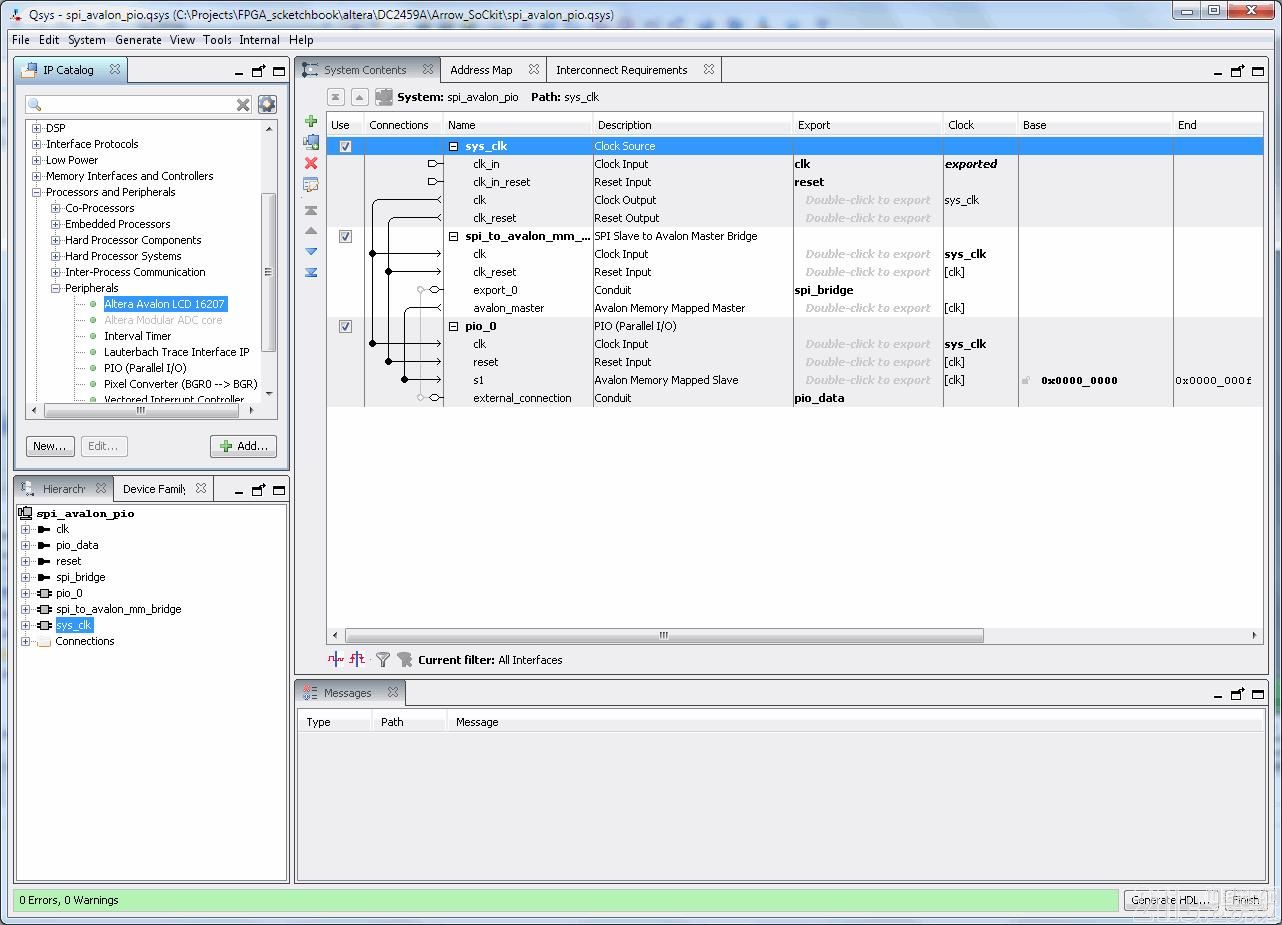

借助基本的一些系統操作,可以將額外的外設內核連接到總線上。為了幫助系統設計,Altera提供了一款名為Qsys的工具,它提供了連接各個IP的圖形用戶界面(GUI)。Qsys可以將GUI設計的系統(圖5)翻譯為HDL。外設地址是完全可配置的。在這個案例中,PIO被設為基地址0x0。

圖5:Qsys GUI

當設計在FPGA中實現后,LinearLabTools中提供的Python庫包含的兩個函數就能連接到設計:

transaction_write(dc2026, base, write_size, data) transaction_read(dc2026, base, read_size)

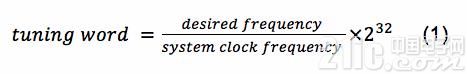

這些函數的第一個參數是Linduino的串口實例。第二個參數是Avalon總線上的外設地址。這兩個函數分別用于接收和返回字節列表。當讀寫IP時這兩個函數具有一定的靈活性。為了設置給定例子的NCO,只需要transaction_write一個函數。公式1用于確定調節字。

要將NCO設為1kHz并具有50MSPS采樣率,調節字的值需要設為85899或0x00014F8B,并按4個字節一起傳送。這樣,將數模轉換器設為1kHz的Python代碼是: transaction_write(linduino_serial_instance, 0, 0, [0x0, 0x01, 0x4F, 0x8B])

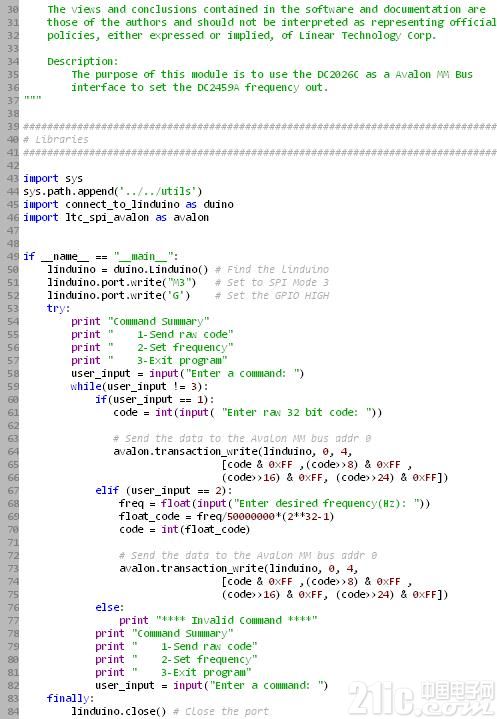

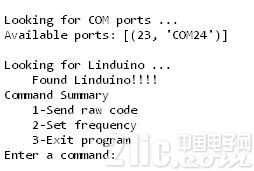

圖6:Python Avalon總線例子

圖6中的Python腳本描述了用于配置NCO的簡單文本接口。值得一提的是:SPI橋使用SPI模式3。這是通過不斷的試錯,并通過分析Altera例子中的Nios處理器的SPI接口驗證后才確定的模式。 本設計實例提供了一種無需使用嵌入式處理器就能控制系統的方法,它能幫助硬件工程師在不打擾軟件工程師的情況下搞定一個項目,并且對硬件設計的影響最小。

評論