詳細介紹數(shù)字時鐘管理模塊與嵌入式塊RAM

業(yè)內(nèi)大多數(shù)FPGA 均提供數(shù)字時鐘管理( 賽靈思公司的全部FPGA 均具有這種特性)。賽靈思公司推出最先進的FPGA 提供數(shù)字時鐘管理和相位環(huán)路鎖定。相位環(huán)路鎖定能夠提供精確的時鐘綜合,且能夠降低抖動,并實現(xiàn)過濾功能。

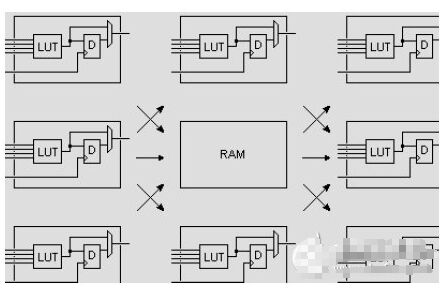

4.嵌入式塊RAM(BRAM)

大多數(shù)FPGA 都具有內(nèi)嵌的塊RAM,這大大拓展了FPGA 的應用范圍和靈活性。塊RAM 可被配置為單端口RAM、雙端口RAM、內(nèi)容地址存儲器(CAM) 以及FIFO 等常用存儲結(jié)構(gòu)。RAM、FIFO 是比較普及的概念,在此就不冗述。CAM 存儲器在其內(nèi)部的每個存儲單元中都有一個比較邏輯,寫入CAM 中的數(shù)據(jù)會和內(nèi)部的每一個數(shù)據(jù)進行比較,并返回與端口數(shù)據(jù)相同的所有數(shù)據(jù)的地址,因而在路由的地址交換器中有廣泛的應用。除了塊RAM,還可以將FPGA 中的LUT 靈活地配置成RAM、ROM 和FIFO 等結(jié)構(gòu)。在實際應用中,芯片內(nèi)部塊RAM 的數(shù)量也是選擇芯片的一個重要因素。

圖2-7 內(nèi)嵌的塊RAM

單片塊RAM 的容量為18k 比特,即位寬為18 比特、深度為1024,可以根據(jù)需要改變其位寬和深度,但要滿足兩個原則:首先,修改后的容量( 位寬 深度) 不能大于18k 比特;其次,位寬最大不能超過36 比特。當然,可以將多片塊RAM級聯(lián)起來形成更大的RAM,此時只受限于芯片內(nèi)塊RAM的數(shù)量,而不再受上面兩條原則約束。

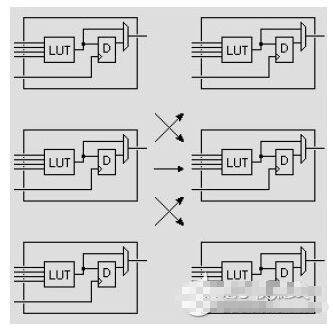

5. 豐富的布線資源

布線資源連通FPGA 內(nèi)部的所有單元,而連線的長度和工藝決定著信號在連線上的驅(qū)動能力和傳輸速度。FPGA 芯片內(nèi)部有著豐富的布線資源,根據(jù)工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類是全局布線資源,用于芯片內(nèi)部全局時鐘和全局復位/ 置位的布線;第二類是長線資源,用以完成芯片Bank 間的高速信號和第二全局時鐘信號的布線;第三類是短線資源,用于完成基本邏輯單元之間的邏輯互連和布線;第四類是分布式的布線資源,用于專有時鐘、復位等控制信號線。

圖2-8 FPGA內(nèi)部互連布線

在實際中設計者不需要直接選擇布線資源,布局布線器可自動地根據(jù)輸入邏輯網(wǎng)表的拓撲結(jié)構(gòu)和約束條件選擇布線資源來連通各個模塊單元。從本質(zhì)上講,布線資源的使用方法和設計的結(jié)果有密切、直接的關系。

評論