簡單組合時序電路設計

要求: 完成占空比(高電平占一個時鐘周期的比例)為0.25的8分頻電路模塊的Verilog設計,并且設計一個仿真測試用的Verilog程序,從時序上驗證分頻電路模塊的正確性。

本文引用地址:http://www.104case.com/article/201808/385213.htm整數分頻器的設計原理

1.1 偶數倍分頻

偶數分頻器的實現非常簡單,通過計數器計數就完全可以實現。如進行N倍偶數分頻,就可以通過由待分頻的時鐘觸發計數器計數,當計數器從0計數到N/2-1時,輸出時鐘進行翻轉,并給計數器一個復位信號,以使下一個時鐘從零開始計數。以此循環,就可以實現任意的偶數分頻。

1.2 奇數倍分頻

奇數倍分頻有兩種實現方法,其中之一完全可以通過計數器來實現,如進行三分頻,就可通過待分頻時鐘上升沿觸發計數器來進行模三計數,當計數器計數到鄰近值時進行兩次翻轉。比如可以在計數器計數到1時,輸出時鐘進行翻轉,計數到2時再次進行翻轉。這樣,就在計數值鄰近的1和2進行了兩次翻轉。如此便實現了三分頻,其占空比為1/3或2/3。

如果要實現占空比為50%的三分頻時鐘,則可通過待分頻時鐘下降沿觸發計數,并以和上升沿同樣的方法計數進行三分頻,然后對下降沿產生的三分頻時鐘和上升沿產生的時鐘進行相或運算。即可得到占空比為50%的三分頻時鐘。這是奇數分頻的第三種方法。這種方法可以實現任意的奇數分頻。如將其歸類為一般的方法:對于實現占空比為50%的N倍奇數分頻,首先要進行上升沿觸發以進行模N計數,計數選定到某一個值再進行輸出時鐘翻轉,然后過(N-1)/2再次進行翻轉,就可得到一個占空比為50%的奇數n分頻時鐘。再同時進行下降沿觸發的模N計數,當其到達與上升沿觸發輸出時鐘翻轉選定值相同時,再進行輸出時鐘翻轉,同樣,經過(N-1)/2時,輸出時鐘再次翻轉以生成占空比為50%的奇數n分頻時鐘。將這兩個占空比為50%的n分頻時鐘相或運算,就可以得到占空比為50%的奇數n分頻時鐘。

3、 實驗步驟和程序

`TImescale 1ns / 1ps

module odd_division(clk,rst,count,clk_odd);

input clk,rst;

output clk_odd;

output[3:0] count;

reg clk_odd;

reg[3:0] count;

parameter N = 8;

always @ (posedge clk)

if(! rst)

begin

count 《= 1‘b0;

clk_odd 《= 1’b0;

end

else

if ( count 《 N/4-1)

begin

count 《= count + 1‘b1;

clk_odd 《= 1’b1;

end

else if (count 《 N/2-1)

begin

count 《= count + 1‘b1;

clk_odd 《= 1’b0;

end

else

begin

count 《= 1‘b0;

end

endmodule

test file:

`TImescale 1ns / 1ps

module test2;

// Inputs

reg clk;

reg rst;

// Outputs

wire [3:0] count;

wire clk_odd;

odd_division uut (

.clk(clk),

.rst(rst),

.count(count),

.clk_odd(clk_odd)

);

always #10 clk=~clk;

iniTIal begin

clk = 0;

rst = 0;

#100;

#10 rst=1;

end

endmodule

4、 測試數據記錄和結果分析

5、 實驗結論和體會

注意事項:

1.請獨立完成實驗和報告,紙質報告每周交一次。

2.每次實驗時請在C盤根目錄中創建一個以本人班級學號如BX10040322命名的文件夾,在這文件夾下創建工程,最后壓縮這個文件夾并上傳后刪除。

3.實驗成績分為兩部分:一為實驗現場操作分(包括程序編寫、得出結論等),二為報告分。

4.實驗步驟和程序分為三部分:一為基本步驟,二為程序流程圖(也可以為算法的文字或公式說明)或狀態圖,三為程序源代碼(可以不用全寫,只寫出關鍵部分的程序)及其說明。

5.實驗結論和體會:一為實驗結論,二為討論當前設計的不足及其改進設想。

6.測試數據記錄和結果分析:Verilog程序綜合出來的RTL圖(電路很復雜時不做要求);時序仿真結果(必備),可以抓圖后打印出來貼在報告上,但必須對圖里的結果有詳細的文字說明。可參考以下案例格式寫

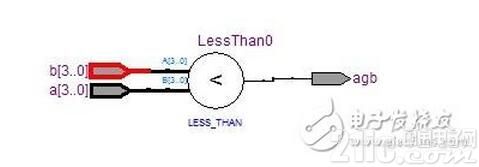

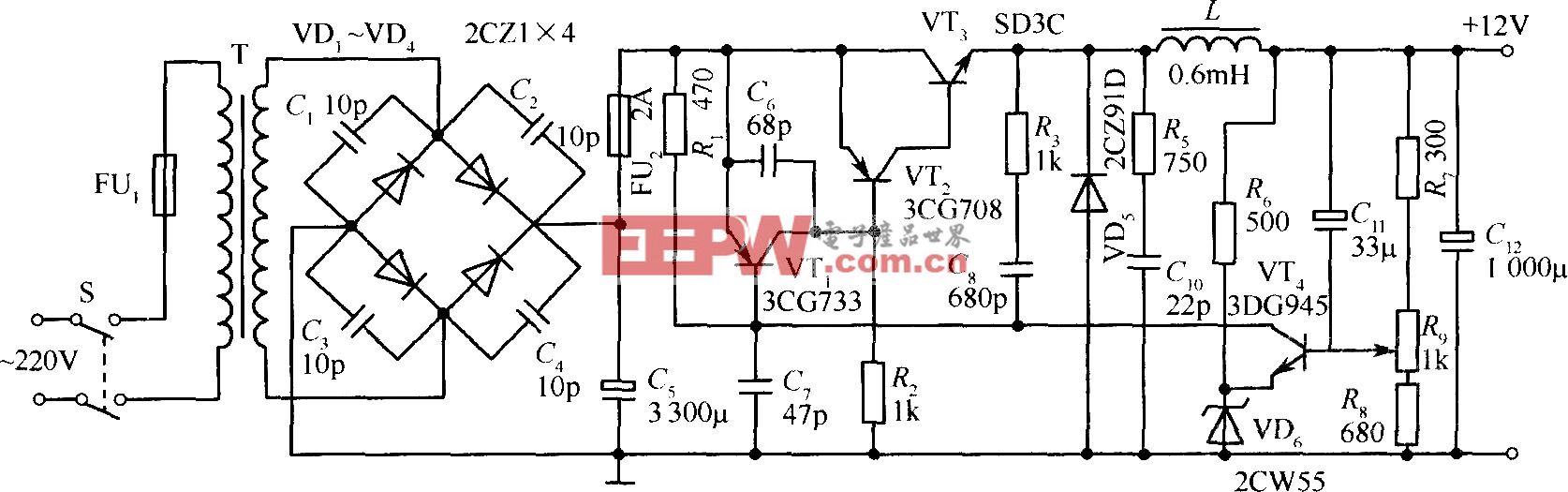

圖1比較器模塊RTL圖

圖1為程序綜合出來的四個比較器的RTL圖,當計數值小于ROM數據時,比較器輸出高電平;當計數值大于ROM數據時,比較器則輸出低電平。比較器的輸出為步進的四相輸入端提供PWM波形,從而達到PWM控制。

比較器的輸入端:

a:對應PWM _ROM模塊的輸出信號。

b:對應十六進制計數器(PWM計數器)的輸出信號。

比較器的輸出端:

agb:輸出a端信號與b端信號的比較值。

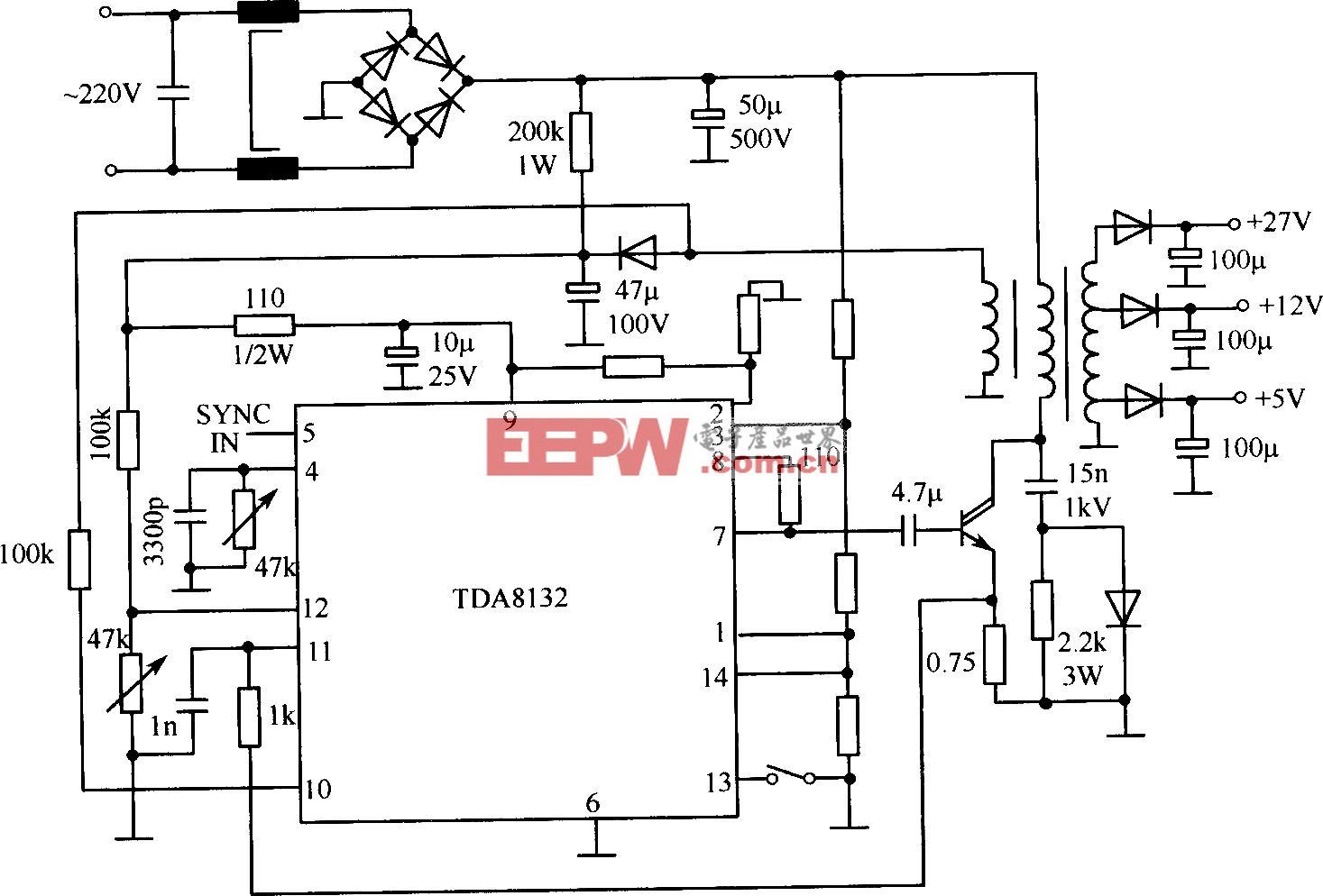

圖2比較器模塊仿真波形圖

仿真結果說明:

當a端信號大于b端信號時,比如a為15而b為0時,輸出端agb輸出高電平信號“1”;反之,輸出端agb輸出低電平信號“0”。

評論