一文讀懂光學(xué)FPGA

基于鍺離子注入的硅波導(dǎo)工藝和激光退火工藝,他們實(shí)現(xiàn)了可擦除的定向耦合器,進(jìn)而實(shí)現(xiàn)了可編程的硅基集成光路,也就是所謂的光學(xué)FPGA。

本文引用地址:http://www.104case.com/article/201807/389729.htm這篇筆記主要分享硅光芯片的一篇最新進(jìn)展。英國(guó)南開普敦大學(xué)Reed研究組最近在arXiv貼出了一篇硅光的研究進(jìn)展 arXiv 1807.01656, “Towards an optical FPGA - Programmable silicon photonic circuits“。基于鍺離子注入的硅波導(dǎo)工藝和激光退火工藝,他們實(shí)現(xiàn)了可擦除的定向耦合器,進(jìn)而實(shí)現(xiàn)了可編程的硅基集成光路,也就是所謂的光學(xué)FPGA。

集成電路中的FPGA(field programmable gate array), 即現(xiàn)場(chǎng)可編程門陣列。FPGA內(nèi)部是一些基本邏輯單元,工程師可根據(jù)需要,將這些邏輯單元按特定的方式連接起來(lái)(燒錄)。FPGA的功能可根據(jù)設(shè)計(jì)者的需求而改變。其設(shè)計(jì)周期短,開發(fā)費(fèi)用低,風(fēng)險(xiǎn)較小。

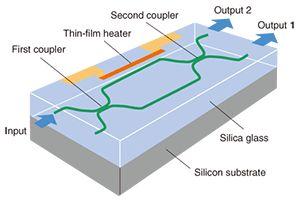

光學(xué)FPGA的出發(fā)點(diǎn)是類似的,希望構(gòu)建一些基本的邏輯單元陣列,用戶可根據(jù)自身需求定義其功能。光芯片的基本單元是定向耦合器(directional coupler, 以下簡(jiǎn)稱DC)。因而如何實(shí)現(xiàn)DC分光比的動(dòng)態(tài)可調(diào)節(jié),是需要解決的關(guān)鍵問(wèn)題。典型的做法是以兩個(gè)3dB的DC構(gòu)成一個(gè)Mach-Zehnder干涉儀,在干涉儀的一條臂上通過(guò)熱效應(yīng)調(diào)節(jié)相位,進(jìn)而達(dá)到分光比的動(dòng)態(tài)調(diào)節(jié),如下圖所示。該方法需要額外的功率輸出,當(dāng)DC的數(shù)目增大時(shí),功耗也相應(yīng)增大。另外該方法中單個(gè)邏輯單元需要兩個(gè)DC, 浪費(fèi)了較多的芯片面積,增大了產(chǎn)品成本。

(圖片來(lái)自ntt-review)

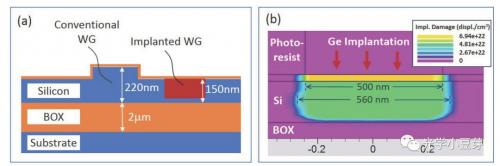

Reed研究組采用Ge離子注入的辦法制備波導(dǎo),該波導(dǎo)可通過(guò)激光退火的方法擦除。其制備藝與可擦除的光柵耦合器(硅光芯片的晶圓級(jí)測(cè)試)相似。Ge離子注入后,硅的晶格發(fā)生位移,引起波導(dǎo)有效折射率的改變。Ge離子注入后的波導(dǎo),結(jié)構(gòu)示意圖如下圖所示,Ge離子的注入深度約140nm。

(圖片來(lái)自文獻(xiàn)1)

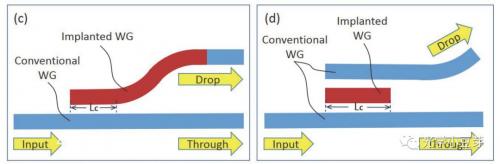

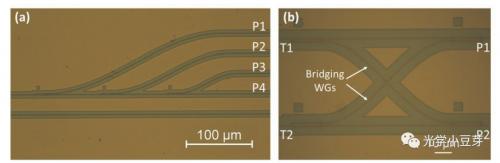

借助于Ge離子注入波導(dǎo),研究人員提出了兩種分光比可調(diào)的定向耦合器結(jié)構(gòu),如下圖所示。

(圖片來(lái)自文獻(xiàn)1)

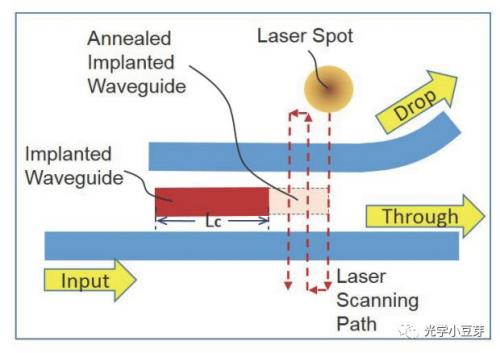

左圖是正常DC中的一根波導(dǎo)由注入波導(dǎo)代替,右圖是在兩根普通波導(dǎo)中間插入一根注入波導(dǎo),借助其實(shí)現(xiàn)光場(chǎng)的耦合。紅色區(qū)域?yàn)樽⑷氩▽?dǎo),其耦合區(qū)域的長(zhǎng)度可以通過(guò)激光退火的方法進(jìn)行改變,進(jìn)而達(dá)到對(duì)分光比的調(diào)節(jié),如下圖所示。激光束在注入波導(dǎo)區(qū)域來(lái)回掃描,可逐步減小注入波導(dǎo)的長(zhǎng)度,進(jìn)而導(dǎo)致drop端口的能量減小。

(圖片來(lái)自文獻(xiàn)1)

以此DC為基礎(chǔ),研究人員進(jìn)一步演示了1x4和2x2的光開光,如下圖所示,

(圖片來(lái)自文獻(xiàn)1)

其中1x4的光開關(guān)由三個(gè)DC構(gòu)成,2x2的光開光由四個(gè)DC構(gòu)成。這些DC的分光比都是可調(diào)節(jié)的,通過(guò)改變分光比,光場(chǎng)可以從不同端口輸出,對(duì)應(yīng)不同的邏輯門操作。

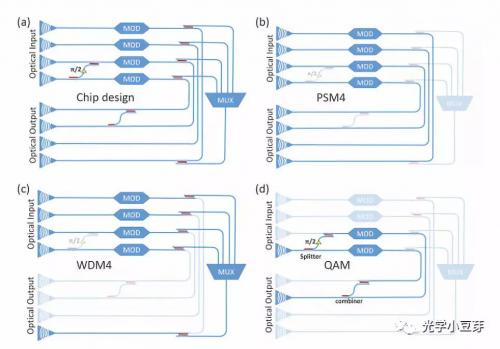

研究人員進(jìn)一步提出了一個(gè)較復(fù)雜的集成光路結(jié)構(gòu),通過(guò)DC分光比的改變,該光路可分別實(shí)現(xiàn)PSM4, WDM4和QAM的發(fā)送光路,如下圖所示,

(圖片來(lái)自文獻(xiàn)1)

最初的光路如圖a所示,改變MUX前端的DC分光比,使得光場(chǎng)不經(jīng)過(guò)MUX,直接到輸出端,對(duì)應(yīng)為PSM4;光場(chǎng)經(jīng)過(guò)MUX, 再傳輸?shù)絾蝹€(gè)GC輸出端,對(duì)應(yīng)為WDM4; 選取兩組MOD, 控制好它們間的相對(duì)相位為pi/2,就可以實(shí)現(xiàn)QAM編碼。該光路設(shè)計(jì)非常巧妙,fab只需提供給用戶類似圖a的光芯片,然后用戶再根據(jù)自身需求,自定義邏輯功能,也就是實(shí)現(xiàn)所謂的光學(xué)FPGA。由于出廠芯片里的光路一致,不需要額外定制,光芯片的成本也相應(yīng)地降低。

總體說(shuō)來(lái),該進(jìn)展的設(shè)計(jì)非常巧妙,借助于可擦除DC,實(shí)現(xiàn)了可編程的集成光路。這也許是未來(lái)集成光路的一個(gè)重點(diǎn)發(fā)展方向。但是目前來(lái)看,該方案的損耗還比較大,普通波導(dǎo)和注入波導(dǎo)的轉(zhuǎn)換損耗接近1dB, 其傳輸損耗也大于一般硅波導(dǎo)的傳輸損耗。當(dāng)多個(gè)DC組成邏輯陣列時(shí),這么大的損耗顯然會(huì)影響其進(jìn)一步的應(yīng)用與推廣。當(dāng)務(wù)之急是進(jìn)一步改進(jìn)工藝,實(shí)現(xiàn)較低的損耗,進(jìn)而實(shí)現(xiàn)較復(fù)雜的邏輯陣列。

評(píng)論