FPGA重點知識13條,助你構建完整“邏輯觀”之二

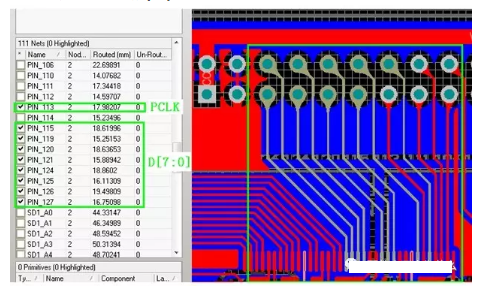

如圖所示,這是PCLK和D[7:0]在SF-CY3核心板上的走線。

本文引用地址:http://www.104case.com/article/201802/375719.htm

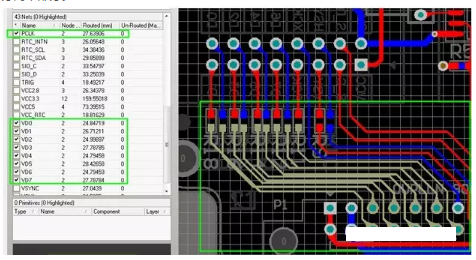

如圖所示,這是PCLK和D[7:0]在SF-SENSOR子板上的走線,在這個板子上的走線由匹配電阻分兩個部分。

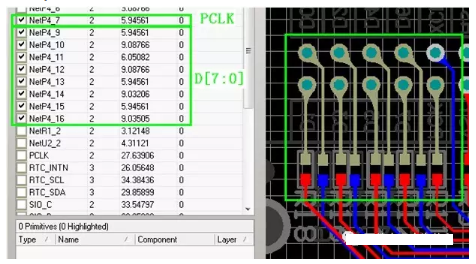

根據前面的走線長度,我們可以換算一下相應的走線延時,如下表所示。因此,我們可以得到,Tcpcb_max = 0.35ns,Tcpcb_min = 0.35ns,Tdpcb_max = 0.36ns,Tdpcb_min = 0.31ns。

將上面得到的具體數值都代入公式,得到:

Input max delay = (0 – 0.35ns) + 65ns + 0.36ns = 65.01ns

Input min delay = (0 – 0.35ns) + 8ns + 0.31ns = 7.96ns

加上一些余量,我們可以去input max delay = 66ns,input min delay = 7ns。

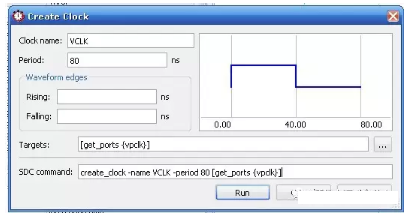

下面我們來添加時序約束,打開TimeQuest,點擊菜單欄的ContraintsàCreat Clock,做如下設置。

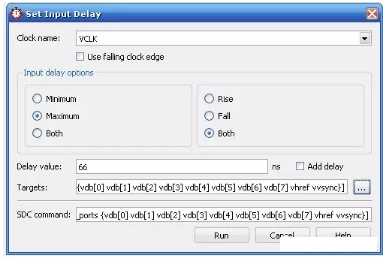

點擊ContraintsàSet Maximum Delay,對vdb[0] vdb[1] vdb[2] vdb[3] vdb[4] vdb[5] vdb[6] vdb[7] vhref的set_max_delay做如下設置。

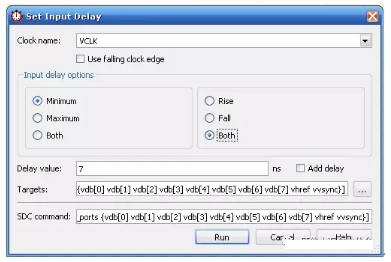

點擊ContraintsàSet Minimum Delay,對vdb[0] vdb[1] vdb[2] vdb[3] vdb[4] vdb[5] vdb[6] vdb[7] vhref的set_min_delay做如下設置。

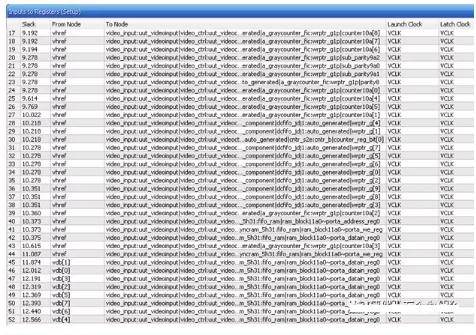

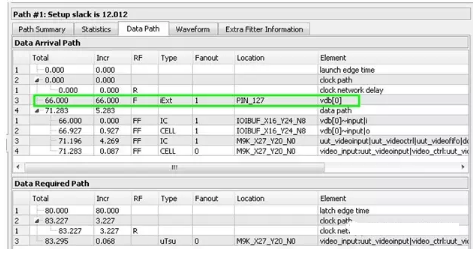

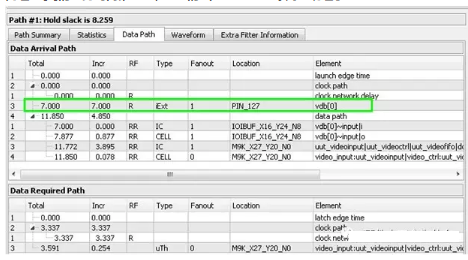

約束完成后,參照前面章節Update Timing Netlist并且Write SDC File…,接著就可以重新編譯整個工程,再來看看這個時序分析的報告。在報告中,數據的建立時間有9-13ns的余量,而保持時間也都有7-11ns的余量,可謂余量充足。

另外,我們也可以專門找一條路徑出來,看看它的具體時序路徑的分析。vd[0]這條數據線的建立時間報告中,66ns的input max delay出現在了Data Arrival Path中。

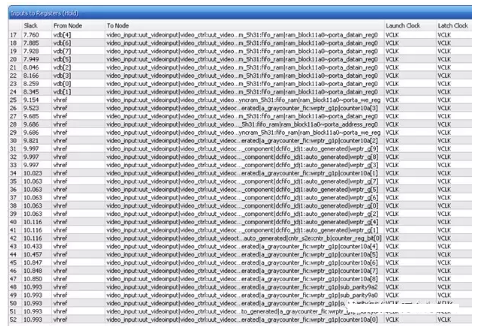

而在vd[0]的保持時間報告中,7ns的input min delay則出現在了Data Arrival Path中。

評論