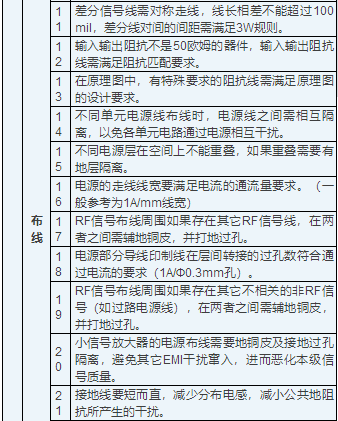

怎樣才能設計一個好的射頻電路,這些地方值得你注意

接下來我們做了表層鋪地后的同樣的仿真(800MHz-1GHz),導入的PCB文件如下圖。

本文引用地址:http://www.104case.com/article/201712/372674.htm

圖3a:0.1016 mm的射頻線(表層鋪地)

圖3b:0.35 mm的射頻線(表層鋪地)

圖3:表層鋪過地后的PCB

仿真結果如下圖:

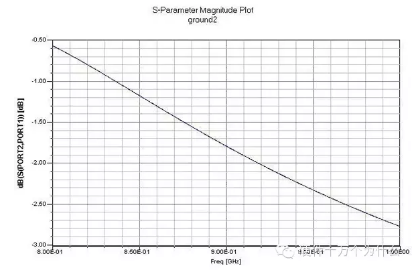

圖4a:表層鋪地后的S21 (0.1016mm)

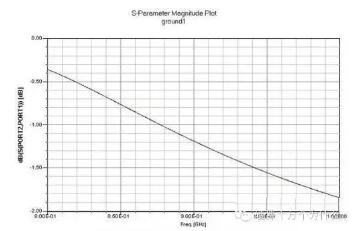

圖4b:表層鋪地后的S21 (0.35mm)

圖4:表層鋪過地后的S21

由圖中看到,仿真的數據顯示,該傳輸線的線損已經是1-2 dB的數量級了,當然0.35 mm的損耗要明顯小于0.1016 mm的。另外一個明顯的現象是相對于未鋪地的仿真結果,隨著頻率由800MHz到1GHz的增加,損耗趨大。

我們可以從仿真的結果中得到這樣一個結果:

1.射頻走線最好按50歐姆走,可以減小線損;

2.表層的鋪地事實上是將一部分RF信號能量耦合到了地上,造成了一定的損耗。因此PCB表層的鋪地應該有所講究。盡量遠離RF線。工程經驗是大于1.5倍的線寬。

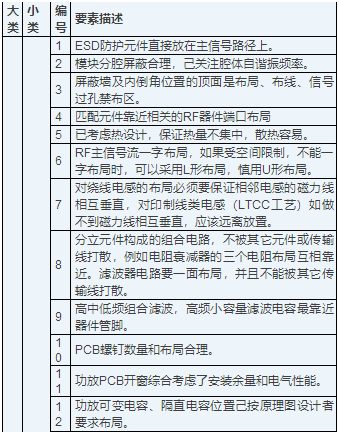

【5】設計checklist

評論