讓FPGA更好地定制化,Achronix祭出custom blocks(定制單元塊)

讓FPGA定制進ASIC/SoC

本文引用地址:http://www.104case.com/article/201711/371188.htm顧名思義,FPGA就是“可編程”邏輯陣列,特點是通用性,利用編程實現(xiàn)各種功能。但是Achronix讓它定制化了。看看Achronix怎么說。

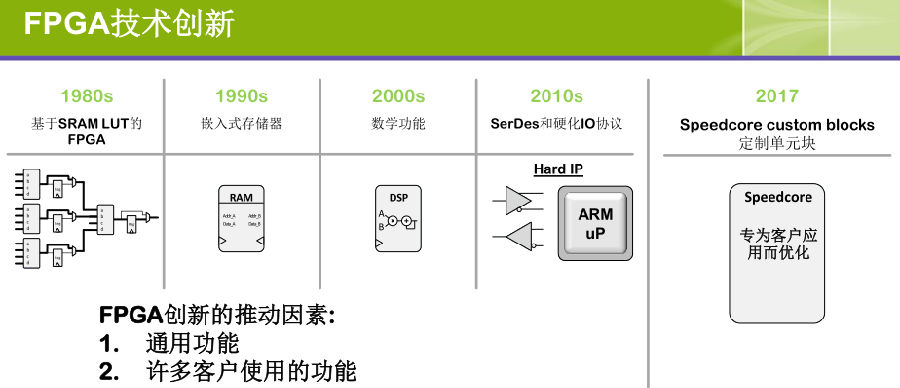

縱觀FPGA的技術(shù)創(chuàng)新史,傳統(tǒng)FPGA制造商所關(guān)注的提供通用的可編程功能,例如上世紀80年代提供基于SRAM LUT的功能,90年代推出嵌入式RAM存儲器,2000年代推出加強數(shù)學(xué)運算的DSP,2010年代加入SerDes和硬化的I/O協(xié)議。他們的共同特點是通用性強,因此一塊FPGA可以賣給不同的客戶,但是缺少定制性。

圖:FPGA的技術(shù)創(chuàng)新史

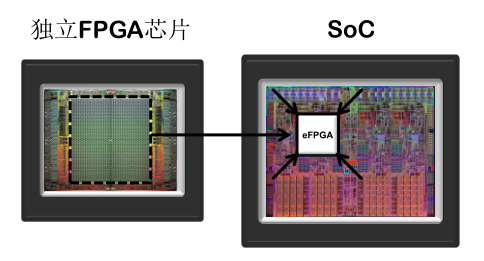

為此Achronix公司不久前推出了定制化的custom blocks(定制單元塊)。名為Speedcore Custom Blocks的IP新產(chǎn)品可加速數(shù)據(jù)密集的人工智能(AI)/機器學(xué)習(xí)、5G移動通信、汽車先進駕駛員輔助系統(tǒng)(ADAS)、數(shù)據(jù)中心和網(wǎng)絡(luò)應(yīng)用。該公司的Speedcore嵌入式FPGA(eFPGA)IP產(chǎn)品已于2016年10月問世,特點是可以把FPGA嵌入到ASIC或者SoC之中。

圖:獨立FPGA與嵌入式FPGA(eFPGA)的版圖布局

eFPGA推高Achronix營收

Achronix公司在京新聞發(fā)布會上,公司市場營銷副總裁Steve Mensor向電子產(chǎn)品世界記者介紹了這款產(chǎn)品的推出背景及新產(chǎn)品架構(gòu)。

定制單元是FPGA的一項全新創(chuàng)新,可以大大縮小芯片的面積,提升芯片的性能。通過這種客戶bolck的協(xié)議,可以分布在內(nèi)部,提供非常高的靈活度。

Archronix目前有三個產(chǎn)品系列:獨立芯片,嵌入式FPGA內(nèi)核,和客戶的芯片進行組合封裝(如下圖)。

圖:Achronix的FPGA產(chǎn)品線

Achronix將在2017年實現(xiàn)強勁的銷售收入和業(yè)務(wù)量增長,預(yù)計2017年第四季度完成后,銷售收入將超過1億美元。

其中,Speedcore是三種產(chǎn)品中增速最快的產(chǎn)品。2016年10月第一次向媒體發(fā)布,目前在公司營收中占25%份額,預(yù)計未來三年內(nèi)將為公司整體利潤貢獻50%。

Speedcore的新產(chǎn)品推出速度也很快:2016年第三季度首次向客戶供貨,基于16nm產(chǎn)品已經(jīng)量產(chǎn),目前正在開發(fā)7nm產(chǎn)品,預(yù)計2018年中可以向客戶供貨。

Achronix獨立的FPGA/Speedster和eFPGA/Speedcore都是由Achronix ACE設(shè)計工具提供支持。優(yōu)勢是完全可以定制的IP,包括LUT等資源數(shù)量、類型的比例和長短比例等。當前該版本可以支持最大2百萬個查找表(LUT)。

custom blocks怎么用

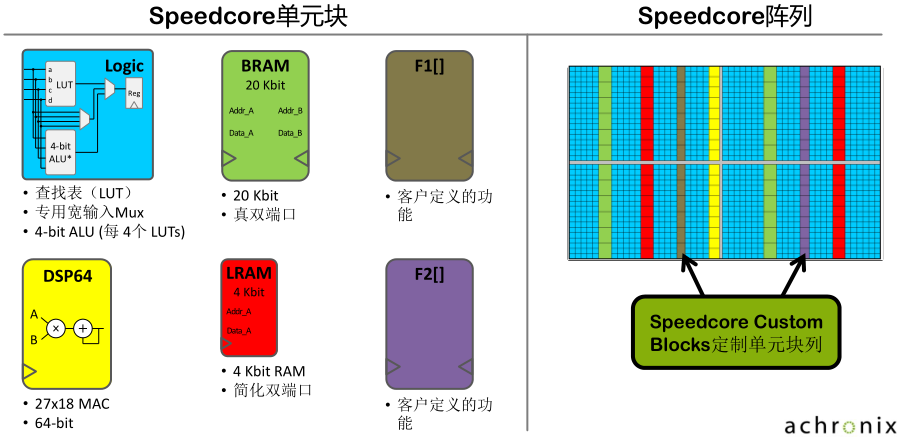

Speedcore是列形式組織,有非常高的靈活度。當前的版本成熟,支持邏輯、DSP、BRAM和LRAM。DSP適合視頻處理和無線通訊。Memory(內(nèi)存)在網(wǎng)絡(luò)中的應(yīng)用也是常見的,其中BRAM是大尺寸的內(nèi)存,LRAM是小尺寸、分布式的內(nèi)存。DSP和RAM也是列形式的組織,和邏輯的組織形式是類似的。

Speedcore Custom Blocks的組織方式和傳統(tǒng)的DSP、RAM和logic的組織方式是一致的,也是以列形式放置在架構(gòu)中。數(shù)量多少可以靈活調(diào)節(jié),如下圖的棕色和紫色單元塊是Speedcore Custom Blocks。

圖:Speedcore的列形式組織

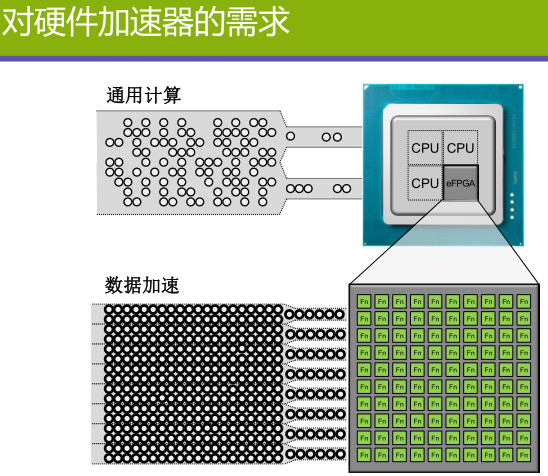

硬件加速器是應(yīng)對計算量增長的利器

當前我們正遇到計算量越來越大的挑戰(zhàn)。據(jù)Cisco的網(wǎng)絡(luò)指數(shù)分析報告,整個網(wǎng)絡(luò)中的數(shù)據(jù)量越來越大,基于此產(chǎn)生產(chǎn)生的應(yīng)用類型越來越多。因此也需要越來越強大的計算處理能力來支持這些應(yīng)用開發(fā),例如針對5G通信、高性能計算(HPC)、網(wǎng)絡(luò)加速和自動駕駛等。如果可以考慮數(shù)量量和應(yīng)用類型的增長。實際上這些應(yīng)用對計算能力的需求增長呈指數(shù)性增長。

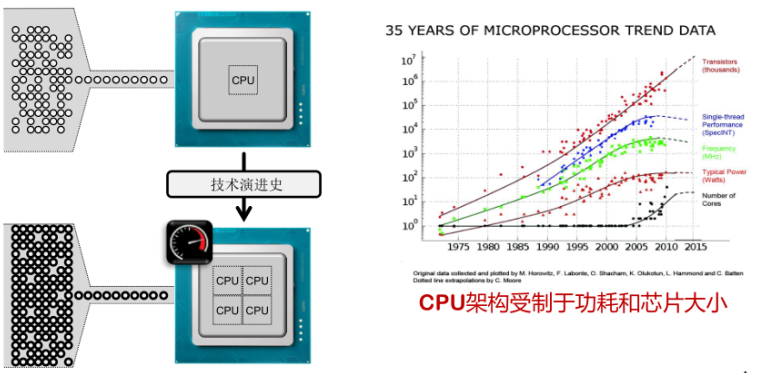

為了應(yīng)對計算能力的急速增長,會對硬件的性能提出更新的需求。過去傳統(tǒng)CPU/馮.諾依曼架構(gòu),計算能力的提升是通過提指令、取數(shù)據(jù)的串行方式來實現(xiàn)。為了提高性能,只能增加CPU/核的數(shù)量,提高單位CPU/核的頻率。但這種方式的缺陷是會在一定的物理限制(諸如功耗和面積)下會達到極限,在某一拐點上增長不會按照預(yù)期進行了(如下圖)。

圖:CPU的演進史

為了克服這種增加CPU/core的挑戰(zhàn),傳統(tǒng)行業(yè)提出了異構(gòu)計算,由外部的硬件加速來協(xié)助CPU進行數(shù)據(jù)處理。傳統(tǒng)的CPU可以作為控制流或進行較為簡單的計算,硬件加速器可以并行處理大量計算。這種組合可以大幅提升計算速度。例如下圖的eFPGA就可實現(xiàn)硬件加速器功能。

圖:硬件加速器的應(yīng)用

eFPGA的應(yīng)用案例,例如字符串(string search)查找功能,在傳統(tǒng)CPU構(gòu)架中查找一個單詞,要消耗很多CPU cylce(循環(huán)),例如需要72 cycle,如果可編程硬件加速器,1個cycle就完成了。

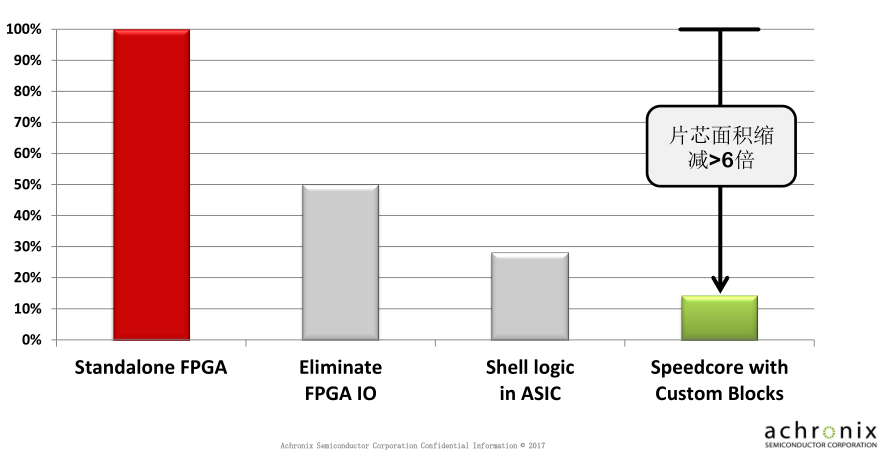

那么,如何將大型FPGA功能放入一個面積很小的片芯中呢?可以利用eFPGA的高效面積使用率,采用custom block自定義單元塊(注:與客戶一起定義的),通過這種組合,可以將相關(guān)片芯面積縮小6倍!

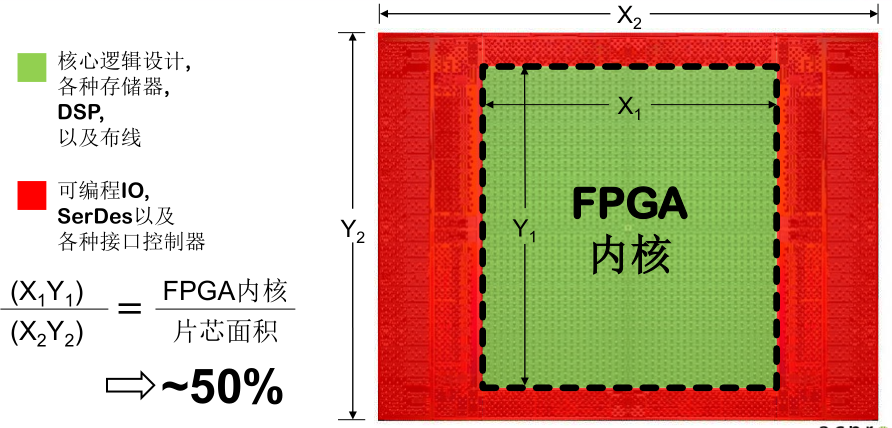

為何eFPGA比標準FPGA更高效?

主要有如下三大原因。

*原因1。如下圖,傳統(tǒng)FPGA構(gòu)架中,周圍的紅色邊框放置可編程I/O、高速SerDes及各種接口控制器,這些會占有30%~40%面積。如果做成嵌入式FPGA,這些面積可以省掉。下圖公式展示的FPGA和片芯面積的比例。

圖:核心電路與邊緣電路的比例

那么為何Speedcore比標準FPGA更高效?

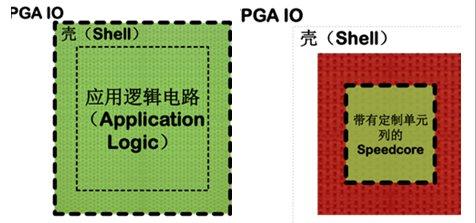

*原因2。微軟在其有關(guān)Catapulit項目(注:某云加速與計算項目)的白皮書中介紹了一種云規(guī)模的加速架構(gòu)。其中增加了一些術(shù)語,有shell(殼)和應(yīng)用。shell是I/O及電路板相關(guān)的邏輯電路,應(yīng)用是在核心邏輯上實現(xiàn)的核心應(yīng)用。

在此研究中,這些shell一旦固定到應(yīng)用中,這些可編程不能被可編程(即固定下來了)。另外,核心應(yīng)用是會改變的。因此如果拿掉shell,會節(jié)省44%的面積。

圖:如果去掉shell,會節(jié)省近一半的面積(注:左右兩圖的左上角均為“FPGA IO”)

*原因3。在把shell剝?nèi)サ幕A(chǔ)上,又增加了自定義的custom block,這是由客戶自定義的,分布在speedcore架構(gòu)之中,有了這種custom block,面積會縮小75%,同時有更低功耗和更高的性能。

基于以上三個原因,即裁剪了FPGA的可編程I/O,shell資源去掉,另外提高了custom block,因此片芯面積大大縮減(如下圖)。

圖:與獨立FPGA相比,把Speedcore的三個優(yōu)勢

小結(jié)

Achronix公司不久前推出的定制化的Speedcore custom blocks(定制模塊),可以實現(xiàn)最小的片芯面積,提供ASIC級的性能,去構(gòu)建獨立FPGA芯片無法提供的功能。

Achronix作為FPGA的后來者,今年也要跨入1億美元俱樂部。新產(chǎn)品Speedcore 推出一年已占營收1/4,未來三年將占半壁江山。在夾縫中生長,Achronix的商業(yè)模式就是不走尋常路。

評論