FT245BM與FPGA的USB接口電路設計

USB總線因其傳輸速度快、占用資源少以及真正的即插即用等諸多優點,受到了廣大開發者的青睞,已經成為很多計算機設備的一種基本配置。目前被廣泛采用的USB設備開發方案主要有以下兩種(1)利用USB設備端接口芯片加微控制器結構。如國內用的比較多的Philips公司的PDIUSBD12/ISP1581等。(2)采用USB單片機。采用這兩種方案要求開發者徹底理解USB協議的細節,并編寫出固件程序。固件的運行要占用微控制器的時間和空間資源,實際通信效率不會很高。也有人用FPGA實現固件的功能,但這種方案開發和調試的難度很大。本人在實際工作中用FPGA外部直接連接一片USB協議芯片FT245BM,實現了FPGA與PC機的USB通信,該方法不用微控制器,減少了元器件的個數,并且占用FPGA資源很少,FPGA仍然可以實現其他邏輯功能,系統設計的靈活性很大。

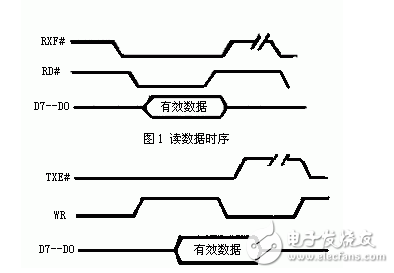

本文引用地址:http://www.104case.com/article/201710/369302.htm關于FT245BM的內部結構及詳細地引腳介紹讀者可以參考其他相關資料,在此僅對與本設計相關的內容作一個介紹。FT245BM內含兩個FIFO數據緩沖區,一個是128字節的接收緩沖區,另一個是384字節的發送緩沖區。它們用作USB 數據與并行I/O口數據的交換緩沖區。FIFO實現與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數據線D0~D7、讀寫控制線RD#和 WR#以及FIFO發送緩沖區空標志TXE#和FIFO接收緩沖區非空標志RXF來完成數據交互。TXE#為低表示當前FIFO發送緩沖區為空,為高表示當前FIFO發送緩沖區滿或者正在存儲前一個字節,禁止向緩沖區中寫數據。RXF#為低表示當前FIFO的接收緩沖區非空。RD#信號由低變高將從 FIFO緩沖區中讀取數據。當RD#變低時將數據送到數據總線。RXF#為高不能從FIFO讀數據。讀寫時序見圖1和圖2。

圖2 寫數據時序

FT245BM與FPGA的接口電路設計

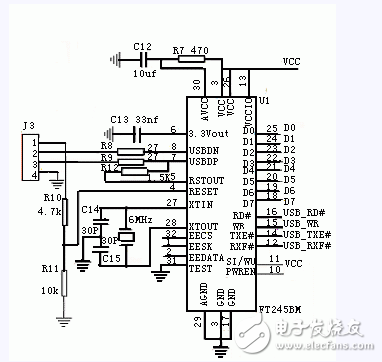

硬件電路設計

圖3是FT245BM的USB與FPGA的接口電路,FPGA選用ALTERA EPF1K50TC-144,其中D0~D7是FT245BM與FPGA交換數據的數據總線,USB_RD#、USB_WR、USB_TXE#、USB_RXF#是相關的控制總線。

圖3 FT245BM與FPGA的接口電路

評論