輸出跟蹤和時(shí)序控制幫助提高FPGA可靠性

為給DSP、ASIC、FPGA和微處理器的負(fù)載點(diǎn)供電而引起的電壓輸入軌數(shù)目的增多使得電源設(shè)計(jì)更加具有挑戰(zhàn)性。特別是由于系統(tǒng)功率和工作頻率要求的增加,造成基礎(chǔ)設(shè)施、工業(yè)和工廠自動(dòng)化設(shè)備對(duì)噪聲和其他不可預(yù)測事件更加敏感。例如,系統(tǒng)啟動(dòng)時(shí)的錯(cuò)誤輸入電壓會(huì)引起系統(tǒng)閂鎖、可靠性問題甚至系統(tǒng)故障。

本文引用地址:http://www.104case.com/article/201710/366841.htm本文討論如何針對(duì)FPGA或微處理器配置各種電壓輸出跟蹤和時(shí)序控制選項(xiàng),來幫助實(shí)現(xiàn)靈敏多電源軌系統(tǒng)的正確啟動(dòng)和關(guān)斷。我們還將分析比率和同步跟蹤設(shè)置,用于防止FPGA的內(nèi)置靜電放電二極管 (ESD) 在上升和下降輸出期間偏壓或過度受壓。這些配置可顯著提升系統(tǒng)可靠性,這對(duì)保證廣泛的基礎(chǔ)設(shè)施系統(tǒng)和工廠車間工業(yè)設(shè)備的生產(chǎn)率和正常運(yùn)行時(shí)間非常重要。

系統(tǒng)配置

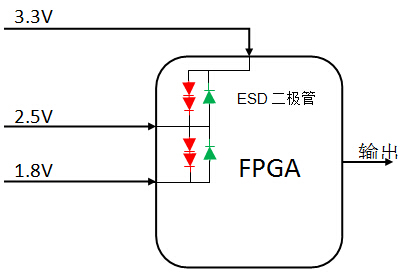

圖1顯示了針對(duì)FPGA的典型應(yīng)用電路配置。從3.3V最高輸入軌到2.5V第二輸入軌,我們發(fā)現(xiàn)一組背對(duì)背ESD二極管配置充當(dāng)內(nèi)部保護(hù)電路。另一組背對(duì)背ESD二極管配置是從第二輸入軌至第三輸入軌。

圖1. FPGA輸入框圖

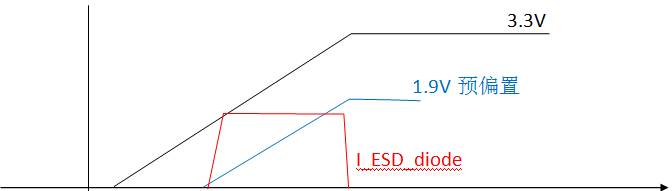

我們假設(shè)一種最高輸入軌(在這個(gè)例子中為3.3V)最先啟動(dòng)的情況。然后,其將2.5V輸出軌預(yù)偏置至約1.9V,將1.8V軌預(yù)偏置至1.2V。類似地,如果1.8V軌首先啟動(dòng),則其對(duì)2.5V和3.3V軌進(jìn)行預(yù)偏壓。在任一種情況下,ESD二極管都必須在啟動(dòng)期間導(dǎo)電。圖2顯示了3.3V輸入軌的電壓信號(hào)及其在啟動(dòng)前發(fā)送至2.5V軌的信號(hào)。流經(jīng)ESD二極管的充電電流取決于啟動(dòng)壓擺率、2.5V輸出電容以及任何負(fù)載。以1.8V輸出軌執(zhí)行相同的啟動(dòng)情景會(huì)顯示類似的電壓信號(hào)。

圖2. 3.3V和2.5V預(yù)偏置的啟動(dòng)波形

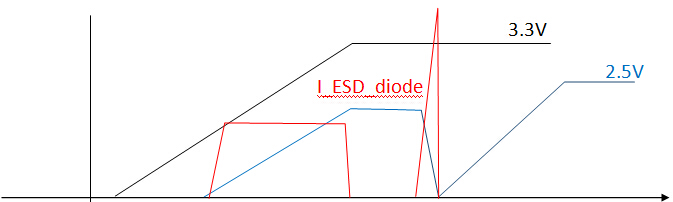

每當(dāng)ESD二極管導(dǎo)電時(shí),其可靠性就會(huì)下降。圖3顯示了當(dāng)2.5V輸入源未設(shè)定為帶有預(yù)偏置啟動(dòng)功能時(shí)3.3V和2.5V軌會(huì)發(fā)生什么情況。可以看到,F(xiàn)PGA的內(nèi)置ESD二極管在2.5V軌啟動(dòng)時(shí)受到壓力。因此,使用帶有預(yù)偏置啟動(dòng)功能的電源可避免該問題和防止系統(tǒng)可能出現(xiàn)的閂鎖。正確的配置降壓穩(wěn)壓器的輸出電壓跟蹤功能可確保所有系統(tǒng)電源軌一起正確軟啟動(dòng),并防止ESD二極管導(dǎo)電。這個(gè)簡單步驟可提升系統(tǒng)可靠性和避免任何意外的系統(tǒng)電源閂鎖。

圖3. 3.3V和2.5V的啟動(dòng)波形

集成式FET DC/DC轉(zhuǎn)換器

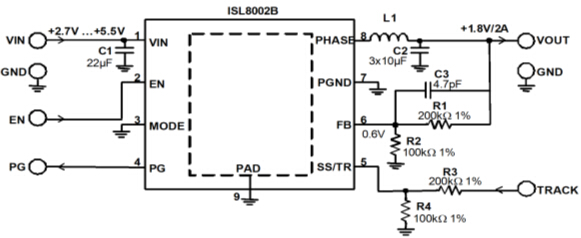

圖4顯示了輸入電壓范圍為2.7V - 5.5V的2A DC/DC轉(zhuǎn)換器的典型應(yīng)用電路。只使用了幾個(gè)外圍元件,包括需要的電阻、電容和電感。轉(zhuǎn)換器集成了補(bǔ)償電路和功率MOSFET來保證設(shè)計(jì)可靠性、最小元件數(shù)目和可達(dá)95%的高效率。

圖4. ISL8002B的典型應(yīng)用原理圖

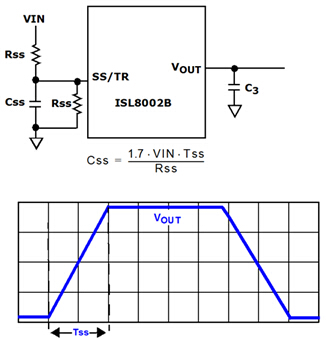

轉(zhuǎn)換器的引腳5同時(shí)提供軟啟動(dòng) (SS) 和輸出跟蹤 (TR) 功能。當(dāng)該引腳連接高電平時(shí),軟啟動(dòng)時(shí)間在內(nèi)部設(shè)置為1ms。但是,使用外圍元件可實(shí)現(xiàn)各種軟啟動(dòng)方案。圖5顯示了如何使用SS/TR功能來編程外部軟啟動(dòng)時(shí)間。

圖5. 外部軟啟動(dòng)配置

通過設(shè)置軟啟動(dòng)電阻RSS和電容CSS可調(diào)整軟啟動(dòng)時(shí)間。相應(yīng)的近似關(guān)系如式1所示:

式1

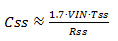

另外還可配置該軟啟動(dòng)功能來跟蹤其他輸出。圖6顯示了Vout1-Vout2的比率跟蹤配置。

圖6. Vout1-Vout2的比率跟蹤

此外,還可以通過將兩個(gè)SS/TR連接到一起來使兩個(gè)輸出電壓同時(shí)上升。類似地,關(guān)斷功能還可相互進(jìn)行比率跟蹤,如同式1中描述的軟啟動(dòng)時(shí)間一樣。

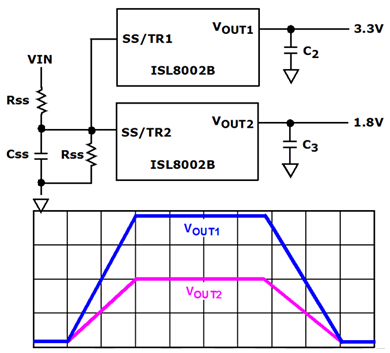

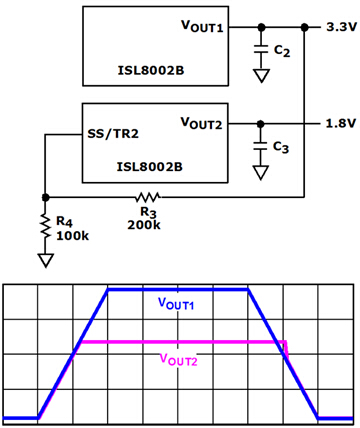

同步跟蹤配置如圖7所示。只需添加一個(gè)電阻分壓器,其比率與其在反饋回路中的輸出電壓感測分壓器的比率相同。在此情況下,所有輸出電壓按照主軌以相同的電壓和斜率上升。通常,所有其他輸出軌應(yīng)當(dāng)跟蹤最高電壓軌。然后,每個(gè)輸出將在達(dá)到其穩(wěn)定點(diǎn)后分支。通過很好地控制所有輸出軌的啟動(dòng)和關(guān)斷,可防止圖1的內(nèi)置ESD二極管導(dǎo)電或正向偏置。最重要的是,該設(shè)計(jì)技術(shù)可防止系統(tǒng)可靠性下降、閂鎖以及更壞的情況:系統(tǒng)故障。

圖7. Vout1 - Vout2的同步跟蹤

結(jié)束語

諸如ISL8002B等集成FET式步降穩(wěn)壓器,為加電和斷電期間的電壓跟蹤提供了大量易于使用的解決方案。任何系統(tǒng)電壓跟蹤需求幾乎都可以使用本文討論的電路進(jìn)行配置。這些配置不限于兩個(gè)穩(wěn)壓器,因?yàn)樗鼈兡苡糜谙到y(tǒng)中的任何數(shù)量的電壓軌。只需要將所有SS/TR引腳連接到一起即可進(jìn)行比率跟蹤。另外還可使用電阻分壓器來對(duì)系統(tǒng)進(jìn)行同步跟蹤編程。無論是比率跟蹤還是同步跟蹤方法均可防止ESD二極管承受不必要的壓力,從而提高系統(tǒng)的整體可靠性。

作者簡介

Tu Bui是Intersil公司的工業(yè)與基礎(chǔ)設(shè)施產(chǎn)品應(yīng)用工程經(jīng)理。他負(fù)責(zé)開關(guān)穩(wěn)壓器產(chǎn)品研發(fā)及所有相關(guān)客戶應(yīng)用支持工作。在加入Intersil之前,Bui先生是ATT貝爾實(shí)驗(yàn)室的Technical Staff Design Engineer成員,在那里他研發(fā)和推出了超過20種世界級(jí)產(chǎn)品及產(chǎn)品族。Bui先生擁有亞利桑那大學(xué)的電氣工程學(xué)士學(xué)位 (BSEE) 和南方衛(wèi)理公會(huì)大學(xué)的工程管理碩士學(xué)位。

評(píng)論