在FPGA開發中盡量避免全局復位的使用?(2)

在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。如果所有的觸發器都使用這一全局復位信號,則GSR信號將形成一個高扇出的網絡(有興趣的朋友可以在綜合工具中查看)。雖然在啟動順序中,它可以與一個用戶自定義的時鐘進行同步,但是想讓它與設計中的所有時鐘信號進行同步是不可能的;比如,一個Xilinx FPGA中可能含有多個DLL/DCM/PLL時鐘處理模塊,每個模塊又可以產生多個時鐘信號,在各個模塊內部進行時鐘信號的同步是可行的,然而想讓所有時鐘信號同步是完全不可行的——從DCM的分布上就可以看出來:中間相隔的長距離布線對高頻時鐘信號的延時顯著增大,進行同步自然無法做到。于是,在時鐘信號頻率越來越高的情況下,全局復位信號便開始成為時序關鍵。解釋如下:

本文引用地址:http://www.104case.com/article/201710/365660.htm

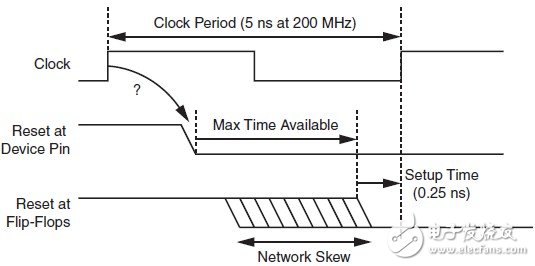

圖1被兩個時鐘信號的邊沿截斷的復位信號的時序圖

關鍵詞:

FPGA

相關推薦

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

xiaohua | 2002-09-24

-

-

-

sandman555 | 2005-02-05

-

-

-

-

-

herbertwj | 2004-08-15

-

-

評論