基于J750的S698PM芯片BSD測試方法

張志國

本文引用地址:http://www.104case.com/article/201708/363260.htm珠海歐比特控制工程股份有限公司,珠海 519080

摘要:S698PM芯片是一款抗輻照型的高性能、高可靠、高集成度、低功耗的多核并行處理器SoC芯片,其芯片內部集成了豐富的片上外設,可廣泛應用在航空航天、大容量數據處理、工業控制、船舶、測控等應用領域;而J750是業界比較認可測試結果的SOC芯片ATE(Automatic Test Equipment)測試機,市場占有率非常高。下面主要介紹在J750上開發S698PM芯片BSD測試程序及注意事項。

關鍵詞:SOC; S698PM; AMBA; ATE; BSD;

中圖分類號:TP332 文獻標識碼:A

文章編號:

Zhang Zhiguo

Zhuhai Orbita Control Engineering Co.,Ltd., Zhuhai 519080, China

Abstract: S698PM anti-radiation chip is a type of high performance, high reliability, high integration, low-power multi-core parallel processor SOC chip, J750 is the ATE machine of the industry recognized SOC chip test results; Here mainly introduce development on S698PM chip BSD test program on J750 machine。

Key words:SOC; S698PM; AMBA; ATE; BSD;

1. 概述

隨著SOC芯片系統功能越來越復雜,在一顆芯片中,通常包括有數字部分、模擬部分以及相關的存儲器件,甚至有的還有射頻模塊,這不但對ATE測試設備提出更快、更高的要求,而且還要考慮測試時間成本,因此通常客戶會要求測試程序前兩項測試項目要能夠快速判斷出SOC芯片90%常見問題的缺陷。經過多年SOC測試方法和測試原理摸索,逐漸形成前兩項測試內容標準:一個是電流功耗測試,另外一個就是BSD測試項目流程。

2. S698PM芯片簡介

S698PM芯片是一款抗輻照型的高性能、高可靠、高集成度、低功耗的多核并行處理器SoC芯片; S698PM芯片內部集成了豐富的片上外設,包括常見USB2.0主控器、I2C主控器、以太網控制器等功能模塊; S698PM芯片支持RTEMS、 eCOS、VxWorks、Linux等實時嵌入式操作系統,用戶可方便地實現嵌入式實時控制系統的高性能多核并行處理設計。

S698PM芯片采用了TMR技術對芯片內部所有邏輯單元進行了三模冗余加固,采用EDAC技術對內部與外部存儲器進行了檢錯糾錯加固,因此該芯片的具有很高的抗輻照能力。

S698PM是全球第一款量產化的對標LEON4內核版本的嵌入式SPARC V8多核SOC芯片,其在功能及性能等方面均領先了業界的同類型產品。S698PM代表了當今SPARC嵌入式SOC芯片的最高水平。

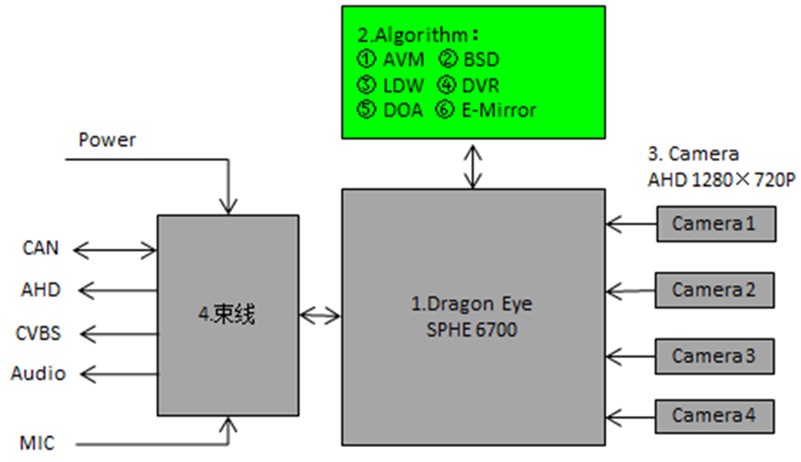

3. BSD測試項目原理

BSD(Boundary-scan Diagnostics)的測試原理主要是利用芯片里JTAG電路進行芯片管腳電路檢測是否有功能缺陷的測試方法。因此SOC芯片里的JTAG電路主要具備兩個功能,并且可通過模式選擇管腳來設定。一個功能是通過JTAG電路進行軟件配置和調試SOC芯片內核工作參數,實現軟件在線調試功能;另一個功能就是通過JTAG口灌入掃描控制信號進行芯片硬件電路的BSD測試或是MBIST測試。

在芯片設計階段,當插入JTAG電路的同時,會在芯片的所有管腳接口上插入一個帶時鐘的觸發器,并把該時鐘信號連接到JTAT_CLK信號上,同時把觸發器的輸入端和輸出端按照掃描鏈的串行互聯方式連接,并把最初的輸入端連接到JTAT_DI端,把最后的輸出端連接到JTAT_DO端,形成一個閉環的測試鏈。最后利用工具生成BSD測試程序需要的PATTERN文件,提供給測試機測試需要。

4. 基于J750的BSD測試方法

首先,BSD測試需要準備測試向量文件,該文件是由IC設計工程師在插入JTAG電路時,生成的邊界掃描向量表文件,同時生成測試機所需的TimingSet參數設置文件,這兩個文件共同決定了信號的類型及信號隨時鐘周期的變化。

信號的常見類型有RH、RL、NR、ROFF、SBC、SBH、SBL等,一般時鐘信號的類型為SBL,這樣時鐘的周期可設、脈沖寬度可控,方便測試機控制該關鍵信號;其他信號類型一般為NR,方便J750測試機監測。

第二步驟,利用J750測試軟件Patter Compiler功能模塊,把標準PATTERN文件轉化成J750識別的格式文件,如下圖1所示:

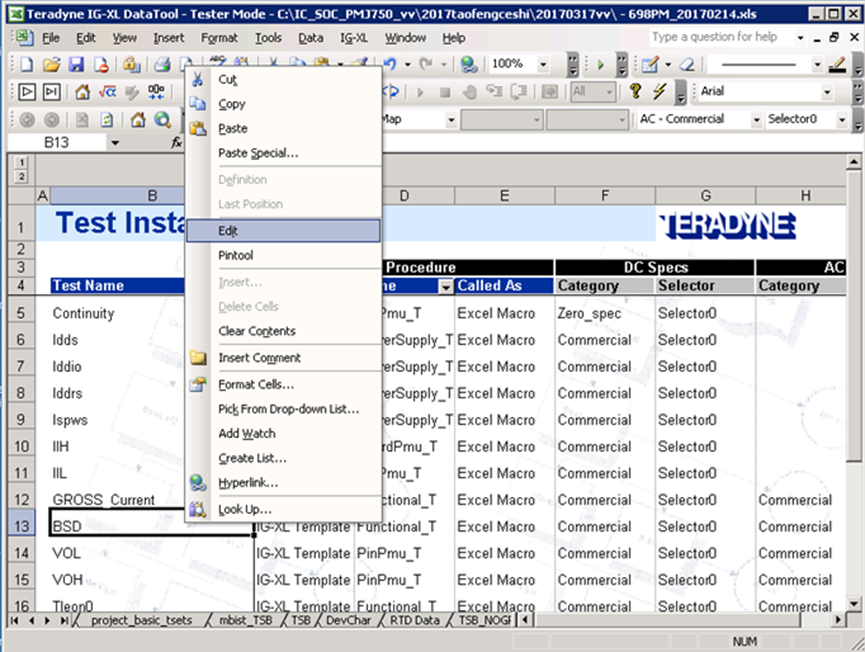

第三步驟,利用J750的測試程序導入功能,將上述兩個文件導入到程序里,完成測試機的TimingSet參數等參數設定, 并根據測試機特性及S698PM時序要求可以微調參數,如下圖2所示:

第四步驟,設定BSD Function Test功能模塊參數,調用BSD測試程序所需的直流和交流參數,以及PATTERN文件。如下圖3所示:

第五步驟,執行BSD function Test命令,在測試過程中,如果結果不滿足要求,可進行TimingSet表格中的時間參數微調,測試結果報告如下圖4所示:

5. 結束語

本文簡要介紹了采用 Teradyne-J750EX 自動測試設備來測試嵌入式SoC 芯片S698PM 的BSD測試原理及注意事項。從測試效果來看,因BSD測試方法與芯片內部電路沒有太大關系,可以快速判讀出芯片管腳電路是否有缺陷,大大地縮短測試時間,從而節省了測試時間,降低了測試成本,因此該BSD測試方法值得推廣。

參考文獻

[1] 顏軍. SPARC 嵌入式系統設計與開發-S698系列處理器實用教程[M].中國標準出版社, 2013.

[2] JTAG標準協議IEEE1149.1-1990

[3] grip.pdf/grmon-2.0.pdf http://www.gaisler.com

[4] J750 Basic Programming Student Manual

[5] S698PM芯片用戶手冊

評論