設計心得:用FPGA打造最強網絡防火墻系統,小心避過這些坑

項目背景及可行性分析

- 項目名稱、項目的主要內容及目前的進展情況

基于FPGA的防火墻系統設計。基于FPGA平臺,設計一個具有防火墻功能的系統,具備對進出網絡數據包解析、過濾等功能。目前正處于總體設計與論證階段。

- 項目關鍵技術及創新點的論述;

關鍵技術有并行運算,狀態檢測,CAM,規則匹配,及PowerPC嵌入式系統。本項目的創新點是將傳統的軟件防火墻系統移植到硬件平臺,充分利用FPGA的優勢,軟硬件相結合,提高處理速度和性能。

- 技術成熟性和可靠性論述:

硬件防火墻開發模式就國內來說主要存在三類。一類是通過網絡處理器(網絡芯片), 一類是通過專用的FPGA編程,第三類是設計專用的ASIC芯片。相對于各種網絡處理器,FPGA是設計ASIC芯片最重要的步驟之一。基于FPGA芯片的片上防火墻系統優勢。框架結構靈活高效。開發者針對防火墻產品需求,有針對性定義數據通路、緩存單元、處理單元、內存總線、總線仲裁單元及其耦合構架,使之達到最優性能。數據線速處理。精心設計的框架結構,使得FPGA芯片的天然并行處理優勢發揮到極致。數據在芯片內始終處于流動狀態,多個處理單元在不同節點并行完成數據分析、處理、替換等操作,從原理上保證了數據線速處理。硬件可升級。最終產品保留FPGA芯片升級接口,隨著網絡應用環境與用戶需求變化,更新芯片設計后,為用戶提供硬件升級服務,最大程度保護用戶投資。開發優勢。所有功能集成在片內完成, 兼之FPGA I/O資源豐富特性,使得系統硬件布局極為簡單,將網卡芯片、內存芯片與時鐘直接與FPGA芯片連接即可,省卻了傳統主板繁雜的控制器、總線等結構,使得系統成本大幅下降。加之在FPGA中嵌入PowerPC硬核,使得片上系統的性能進一步提升。

項目實施方案

1.方案基本功能框圖及描述

用框圖的方式并加以簡單的描述簡述實施本項目的技術方案。

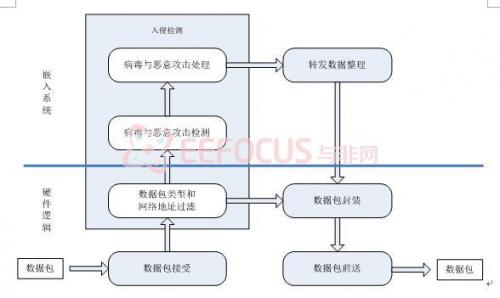

圖1 方案基本功能流程框圖

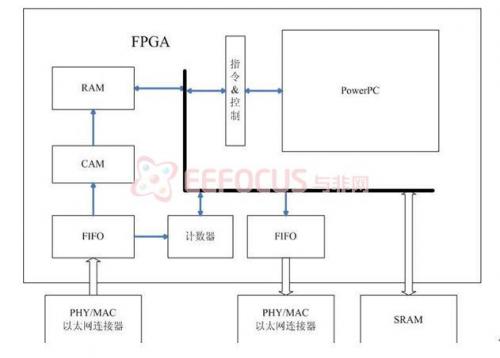

圖2 系統結構框圖

該方案采用FPGA硬件邏輯和嵌入系統的兩層分層結構,如圖1所示。

FPGA硬件邏輯及外圍硬件主要實現的功能是:數據包收發、五元組(協議類型、源/目的IP地址、源/目的端口號)的數據分類以及固定字段模式匹配、轉發數據的封裝。

嵌入式系統實現的主要功能是:病毒與惡意攻擊的檢測、病毒與惡意攻擊的處理、過濾規則管理、轉發數據整理。

方案的核心部分是由實現入侵檢測的三個模塊組成。利用硬件匹配和數據負載匹配認別病毒和惡意攻擊,為網絡提供安全保護。

2.需要的開發平臺

實現本方案所需要的基本功能、功能、接口,FPGA,PowerPC,雙網口(一個采用開發板上的網口,另需一網絡擴展板),SRAM,

所需要的目標FPGA開發平臺,簡述為什么需要此平臺

高級板-Virtex-2 Pro

是否需要其它配套的開發工具

配套的下載,調試工具

2.方案實施過程中需要開發的模塊

在本方案中需要研制、開發的功能主要模塊,以及開發的方式

見圖1、圖2所示

3.系統最終要達到的性能指標

論述本項目最終完成時所設想達到的目標。

實現一個具有防火墻功能的系統。

需要的其它資源

1.設計輸入輸出功能子板

子板功能描述、接口說明、時間、方式

網絡擴展板,RJ45,2007年10月

2.測試設備

列出在方案實施過程中所需要的測試設備

萬用表、示波器、頻譜儀、邏輯分析儀等

3.方針、開發工具

列出在方案實施過程中所需要的仿真、開發工具等。

ModelSim、Xilinx ISE,Sinffer

評論