用最新工具解決FPGA設(shè)計(jì)中的時(shí)序問題

時(shí)序問題的惱人之處在于沒有哪種方法能夠解決所有類型的問題。由于客戶對(duì)于和現(xiàn)場(chǎng)應(yīng)用工程師共享源代碼通常非常敏感,因此我們通常都是通過將工具的潛力發(fā)揮到極致來幫助客戶解決其時(shí)序問題。當(dāng)然好消息就是通過這種方法以及優(yōu)化RTL代碼,可以解決大多數(shù)時(shí)序問題。

但在深入探討之前,我們首先需要對(duì)時(shí)序問題進(jìn)行一點(diǎn)基本分析。這里的目標(biāo)是首先排除明顯的問題,如將時(shí)鐘引腳置于器件的上部、在器件下部驅(qū)動(dòng)數(shù)字時(shí)鐘管理器(DCM),然后再在器件上部驅(qū)動(dòng)全局緩沖(BUFG)。

有時(shí),此類引腳布局會(huì)導(dǎo)致根本沒有辦法滿足時(shí)序要求。通過察看時(shí)序報(bào)告中的延遲,通常可以發(fā)現(xiàn)這些明顯的時(shí)序問題。在這些情況下,為了解決這些明顯的問題,都需要利用底層規(guī)劃工具“floorplanner”將造成問題的部分鎖定在適當(dāng)?shù)奈恢谩5讓硬季忠?guī)劃工具還可以幫助以可視的方式來理解時(shí)序問題。

用最新工具進(jìn)行時(shí)序分析

假設(shè)問題并非這么明顯,那么為了鎖定問題所在,需要了解所使用的器件系列以及軟件版本。通常,每種器件系列對(duì)應(yīng)一種最優(yōu)的軟件版本。如Xilinx Virtex-4器件對(duì)應(yīng)的最佳軟件是ISE軟件9.2i版,而對(duì)Virtex-5 FPGA則是ISE軟件10.1版。

綜合工具的版本也很重要,因此當(dāng)采用最新的器件架構(gòu)時(shí),下載并使用最新版軟件非常重要。軟件開發(fā)幾乎總是滯后于硬件功能,因此我不提倡使用舊版軟件進(jìn)行基于新器件的設(shè)計(jì)。

然而,有些客戶由于擔(dān)心新的和未知的軟件缺陷而不愿意升級(jí)軟件。但是,在使用最新的器件時(shí),如果希望更好地處理時(shí)序挑戰(zhàn),強(qiáng)烈建議下載最新版軟件。

擁有了最適用于目標(biāo)器件系列的軟件,還需要確定最佳的實(shí)現(xiàn)選項(xiàng)。可惜,并沒有適用于所有情況的超級(jí)選項(xiàng)組合。對(duì)于設(shè)計(jì)實(shí)現(xiàn)工具來說,有成千上萬種不同的實(shí)現(xiàn)選項(xiàng)組合。根據(jù)所使用的實(shí)現(xiàn)選項(xiàng)不同,時(shí)序分?jǐn)?shù)(即所有存在錯(cuò)誤的時(shí)序路徑與時(shí)序要求的差異總和,以皮秒表示)也會(huì)有很大不同。

賽靈思的幾款工具可幫助確定適用于特定設(shè)計(jì)的最佳實(shí)現(xiàn)選項(xiàng)。ISE軟件現(xiàn)在包括兩個(gè)工具:Xplorer以及最近發(fā)布的SmartXplorer。SmartXplorer可充分發(fā)揮多處理器優(yōu)點(diǎn),能夠以不同選項(xiàng)組合運(yùn)行多個(gè)實(shí)施實(shí)例。

SmartXplorer需要Linux支持,但使用非常容易。其命令行很簡(jiǎn)單:smartxplorer designname.edn -p xc5vlx110t-1ff1136.

只要用戶約束文件(UCF)和網(wǎng)表約束文件(NCF)文件名相同,SmartXplorer會(huì)自動(dòng)使用正確的選項(xiàng)。唯一需要做的是編輯主機(jī)列表文件。

SmartXplorer可以通過SSH/rsh安全shell登錄到其他機(jī)器。只需要在名為smartxplorer.hostlist的文件中將每臺(tái)機(jī)器一行將機(jī)器名字添加進(jìn)去就可以了。如果機(jī)器有兩個(gè)處理器,請(qǐng)將機(jī)器列出兩次。

PlanAhead軟件也包括了與SmartXplorer類似的稱為ExploreAhead的功能。ExploreAhead支持同時(shí)在多臺(tái) Linux機(jī)器上分布式運(yùn)行布局布線任務(wù)。所有這些工具的目的都是類似的:確定實(shí)現(xiàn)工具的最佳選項(xiàng)組合,以獲得最好的時(shí)序得分。

請(qǐng)注意選項(xiàng)的不同組合對(duì)于時(shí)序得分和運(yùn)行時(shí)間的巨大影響。仔細(xì)調(diào)整綜合選項(xiàng)也非常重要。例如,在綜合選項(xiàng)中關(guān)閉結(jié)構(gòu)層次(hierarchy)通常會(huì)大大提高性能。綜合過程中的約束條件好壞在滿足時(shí)序方面的作用也很突出。

用PlanAhead分析時(shí)序

在了解實(shí)現(xiàn)選項(xiàng)對(duì)最佳時(shí)序分值的影響之后,現(xiàn)在可以開始有效地分析時(shí)序問題了。這時(shí)候,PlanAhead是一款非常有價(jià)值的工具,可以視覺化顯示布局布線后的設(shè)計(jì)。利用它,還可以導(dǎo)入時(shí)序約束并在已布局窗口交叉探查(cross-probe)時(shí)序失敗的路徑。

當(dāng)工具本身的決策不好時(shí),則可以通過平面布局模塊或通過手工布局部分組件的方式來糾正。這一過程通常需要反復(fù)多次,才能夠確定時(shí)序優(yōu)化的最佳設(shè)計(jì)布局方式。PlanAhead軟件的可視化功能確實(shí)使這一工作的完成更容易了。

利用PlanAhead軟件,首先創(chuàng)建項(xiàng)目(project),然后將HDL或網(wǎng)表文件導(dǎo)入工具中。一旦創(chuàng)建了一個(gè)項(xiàng)目,就可以選擇 “File→Import Placement”。選擇時(shí)序優(yōu)化效果最佳的布局布線后(ncd)文件,將布局布線信息導(dǎo)入PlanAhead軟件項(xiàng)目。

本文引用地址:http://www.104case.com/article/201706/349418.htm

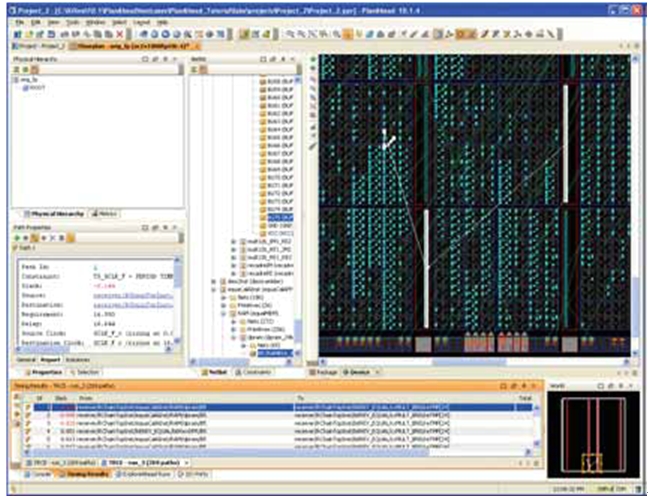

軟件會(huì)將PlanAhead項(xiàng)目組織到幾個(gè)不同的窗口。左上窗口是物理分層窗口,描述了設(shè)計(jì)中的當(dāng)前區(qū)域組。選定窗口在下面,包含了當(dāng)前選定的數(shù)據(jù)詳細(xì)信息。中間窗口是網(wǎng)表窗口,給出了整個(gè)網(wǎng)表的分層結(jié)構(gòu)。最右側(cè)窗口是器件觀察窗(Device view),里面已經(jīng)充滿了設(shè)計(jì)實(shí)施完成后的邏輯。

然后,將時(shí)序分析報(bào)告(TWR/TWX)導(dǎo)入到PlanAhead工具中。選擇“File→Import TRCE Report”。這一步將時(shí)序報(bào)告數(shù)據(jù)添加到底部窗口。按照時(shí)序余量(timing slack)對(duì)這一窗口進(jìn)行排序可以將焦點(diǎn)首先集中于違反時(shí)序要求最多的地方。經(jīng)常的情況是解決了這些時(shí)序偏差最大的地方所存在的問題也就解決了整個(gè)設(shè)計(jì)的時(shí)序問題。

一旦選擇了一條時(shí)序失敗的路徑,PlanAhead軟件就會(huì)選定時(shí)序失敗路徑上的實(shí)例和連接。按F9鍵放大顯示選定的部分。

這兒的事情顯得有些復(fù)雜。必須進(jìn)行一定的審查和思考才能夠明顯布局布線工具將基本單元(primitive)放在某個(gè)地方,以及為什么對(duì)于當(dāng)前的特定設(shè)計(jì)來說還有更好的方法。

可以放大顯示任何高亮的基本單元。鼠標(biāo)點(diǎn)擊一個(gè)基本單元并拖動(dòng),可以更好地觀察其連接情況。在網(wǎng)表窗口,還可以移動(dòng)到包含了所選實(shí)例的頂層模塊。鼠標(biāo)右擊模塊名稱并為選定的實(shí)例選擇顏色,這樣就可以顯示出這一模塊在芯片中的布局,以及組內(nèi)單元是靠近還是散開的。

可能發(fā)現(xiàn)有時(shí)需要更好地鎖定特定的基本單元。Block RAM和DSP模塊的自動(dòng)布局是導(dǎo)致時(shí)序失敗的常見原因。很容易發(fā)現(xiàn)布局布線工具將Mult18安排的位置很不好。時(shí)序失敗路徑中的塊RAM輸出連接到 Mult18,后者的輸出又饋送到進(jìn)位鏈。塊RAM在上部、Mult18在下部,而邏輯部分又位于上部。如果布線不需要上上下下、邊邊角角地來回繞,該路徑應(yīng)當(dāng)可以滿足時(shí)序要求。

時(shí)序問題不同,在PlanAhead軟件中處理這些時(shí)序問題的解決方案也跟著變化。在PlanAhead設(shè)計(jì)工具中解決時(shí)序問題需要不斷實(shí)踐。該解決方案體現(xiàn)以下操作步驟中:

1. 選擇高亮顯示失敗的時(shí)序路徑。

2. 右擊路徑上的某個(gè)實(shí)例,選擇“Highlight With →color of choice”。

3. 在左側(cè)欄中,將底部第二個(gè)Mult18釋放。右擊“Unplace。這將為時(shí)序失敗的塊RAM騰出空間。

4. 點(diǎn)擊拖動(dòng)底部的Mult18向左上移動(dòng)一個(gè)位置。

5. 點(diǎn)擊拖動(dòng)右邊的塊RAM到底部左側(cè)的自由塊RAM位置。

6. 選定失敗的時(shí)序路徑,確認(rèn)路徑看起來是優(yōu)化的。

7. 選擇“Tools→Clear PlacementConstraints”。點(diǎn)擊第一個(gè)選項(xiàng)中的“Next”。

8. 選擇“Unplace All But SelectedInstances”。在余下的向?qū)Р襟E點(diǎn)擊“Next”。

9. 如果希望在“PlanAhead軟件外運(yùn)行實(shí)施流程,選擇“File →Export Floorplan”。

10. 工具會(huì)輸出一個(gè)新的文件名為“top.ucf”的UCF文件。你可直接使用這一文件,或者將文件中的約束加入到原始UCF中。

11. 另一個(gè)選擇是在PlanAhead軟件內(nèi)運(yùn)行實(shí)施工具。

選擇“Tool→Run ISE Place Route with ExploreAhead。

ExploreAhead提供了許多很好的功能,包括:自動(dòng)從器件觀察窗導(dǎo)入約束到UCF;簡(jiǎn)化了從ExploreAhead中運(yùn)行的布局和時(shí)序結(jié)果的導(dǎo)入。

Pblock和底層規(guī)劃

如果發(fā)現(xiàn)布局中有許多時(shí)序失敗路徑,手工布局調(diào)整通常無法解決問題。反過來,應(yīng)當(dāng)創(chuàng)建區(qū)域組。創(chuàng)建區(qū)域組(Pblock)的方式之一是在網(wǎng)表窗口中右擊模塊名字并選擇“Draw Pblock”。然后在器件觀察窗中希望放置區(qū)域組的地方畫一個(gè)長(zhǎng)方形。

工具會(huì)創(chuàng)建一個(gè)Pblock,同時(shí)會(huì)顯示有關(guān)的詳細(xì)信息。屬性窗口會(huì)顯示Pblock需要的邏輯資源以及畫出的長(zhǎng)方形區(qū)域組中可用的資源。

設(shè)計(jì)的底層規(guī)劃是一個(gè)需要深度交互的過程。你可能會(huì)發(fā)現(xiàn)需要反復(fù)多次調(diào)整區(qū)域組才能夠達(dá)到目標(biāo)。請(qǐng)記住有時(shí)創(chuàng)建的區(qū)域組越小越少越好。你并不是總需要將整個(gè)模塊固定為區(qū)域組。集中于時(shí)序失敗的基本單元,將它們組合為區(qū)域組并單獨(dú)為其進(jìn)行底層規(guī)劃。

在此過程中,應(yīng)當(dāng)利用Pblock指標(biāo)(Metrics)來更好地理解有關(guān)功能,如區(qū)域組中可配置的邏輯塊(CLB)的利用情況如何(可以在 PlanAhead軟件左上窗口中點(diǎn)擊Metrics標(biāo)簽來查看可用的指標(biāo))。這可幫助確定是否某個(gè)特定區(qū)域中太擁擠以致妨礙布線。如果確實(shí)比較擁擠,可能需要通過平面規(guī)劃將設(shè)計(jì)邏輯放得散開一些。

一旦利用PlanAhead軟件獲得盡可能好的時(shí)序分?jǐn)?shù),最后的任務(wù)就是優(yōu)化代碼。PlanAhead設(shè)計(jì)工具現(xiàn)在支持HDL源文件。根據(jù)你導(dǎo)入的源文件不同,你可以從時(shí)序問題出發(fā)通過交叉探查功能回查到網(wǎng)表或HDL。

利用原理圖觀察窗(Schematic view),可以察看整個(gè)時(shí)序路徑。只需要從時(shí)序結(jié)果中選擇時(shí)序路徑并按F4。仔細(xì)觀察從其他模塊扇入扇出的邏輯。由于外部接口要求,工具可能經(jīng)常需要將模塊在芯片上散開部署。如果是這樣,可能需要使用流水線。

Block RAM和DSP輸出時(shí)序是引起時(shí)序問題的常見原因。通過在這些模塊的輸出進(jìn)行存儲(chǔ),通常可以恢復(fù)一納秒甚至更多的時(shí)間。

評(píng)論