用FPGA實現FIR濾波器

基礎和主要參數

也許你在聽FIR濾波器課時不夠專注。這里做一個快速的復習,最簡單的形式是, FIR 濾波器的輸出 y(n)是求采樣數據x(n) 的N個輸入的平均值。 存儲的每個采樣稱為抽頭。 當然大多數設計都比這個復雜, 要提供優化的濾波器 特性,要用系數乘 每個抽頭, 或者對 h(i) 進行加權。

圖1 典型的FIR濾波器結構(完全并行)

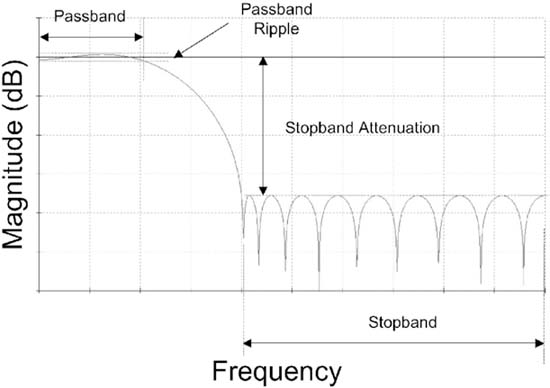

用于FIR濾波器的主要參數是通帶、阻帶、阻帶衰減和通帶波紋。對于某些應用,阻帶波紋也許是重要的和規定的。然而對大多數應用,阻帶衰減是適當的。還有輸入采樣率,以及與輸入數據分辨率一起的所要求的輸出采樣率。

你也許只是接受任務,而由你自己選擇設計規范。當然應用項目定義了許多規范。這里有一些指導意見,幫助你縮小各種可能性,評估權衡設計。

通常通帶越接近阻帶,設計就越具挑戰性。同樣,指定通帶很低的波紋,或者很高的阻帶衰減增加了設計的復雜性。必須牢記,指定波紋和衰減為數據的分辨率,你必須滿足設計要求。指定衰減的要點是小于輸入數據的最低位。同樣在滿標度中指定小于1位的通帶波紋是不必要的。如同其它的濾波器,FIR濾波器可構成低通、高通和帶通濾波器。

輸入至輸出的采樣率也會影響你的設計。在簡單的設計中,輸入速率和輸出速率是相等的。然而,在許多低通濾波器設計中,輸出以輸入的速率運行是不經濟的,因為傳輸信息不要求高的輸出率。取十分之一速率的FIR是合適的。其它要求較高輸出率的設計,則采樣內插FIR。

進行設計

選擇FIR濾波器的系數有兩種方法。Parks-McClellan方法(執行Remez算法)和進行沖擊響應的窗口操作。窗口方法依賴于一個事實,要求頻率響應的離散Fourier反變換代表FIR濾波器的系數。理想的頻率響應用作起始點,于是應用窗功能減少系數的數目,成形頻率響應。通用的窗功能包括矩形、三角、Hanning、Hamming、Kaiser 和Blackman。

沒有必要對數學進行深究,有許多免費的低成本工具幫助你進行設計。如果使用MATLAB,MathWorks有各種工具可用于FIR設計。如果你不用這些包,用Internet搜索“FIR濾波器設計工具”將展現一些免費的低成本工具。

首先應做出采用哪種設計方法的決策。大多數設計者采用Park-McClellan 方法,因為設計輸入是濾波器的要求,這個方法通常滿足具有最少抽頭的濾波器要求。假設采用這個方法,你可以簡便地把要求輸入至所選的工具中。大多數設計工具會給出頻率響應、沖擊響應和濾波器系數。如果選擇窗口方法,只要做些實驗。要輸入截止頻率、窗口方法和抽頭數目至設計工具。于是設計工具會給出頻率響應。如果頻率響應不是你所要的,你可以改變輸入參數和迭代過程。

因此,你已經用設計工具產生了系數,檢驗了頻率響應。那么現在是否可以移開這個工具,而在FPGA中實現這個設計呢?并非如此,還要考慮一些事情。首先要確定頻率響應,數據不是無限精確的。大多數設計工具讓你定義一個量化級別并觀察結果。倘若級別的精度是合理的,那就不需要做改動。然而,最好是現在發現這些問題而不是在實驗室。下一步是研究其它的濾波器設計,諸如Lth帶(或者Nyquist)濾波器,這些濾波器大約有一半的系數設置為0,因此減少了數學上的復雜性。

在FPGA中實現設計

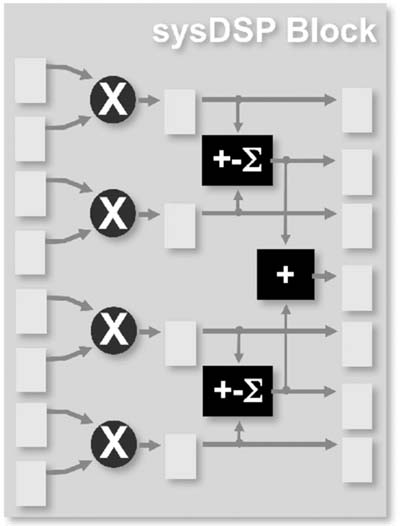

你設置了系數之后,現在打算在FPGA中實現這個設計。再次要做出若干決定。首先是選擇實現乘法器單元的方法,決定它們能運行多快。通常有兩個選擇:用在FPGA內實現邏輯的查找表(LUT)來實現乘法器,或者用FPGA內的專用的DSP單元。為了說明這些選擇,考慮LatticeECP2 FPGA系列,在這個FPGA內用sysDSP塊實現一個18x18乘法器不占用LUT,運行速度高于400MHz。用LUT完成相同的功能其性能大約是100MHz,并要占用許多LUT。專門的DSP塊擁有高速并使用少的LUT,通常選擇這個方法,除非你保留DSP塊準備留作它用。

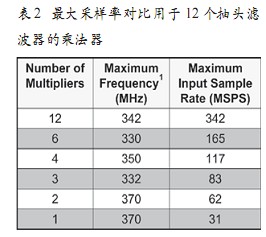

接下來要做的事是決定使用多少個乘法器。對于最快的速度,乘法器的數目等于FIR濾波器中抽頭的數目。這種類型的濾波器完全用并行形式來實現。然而在許多情況下,并不需要性能的級別,允許乘法器時間共享。一種快速計算揭示了使用的乘法器的數目。首先做一個簡化,以采樣率除速度,你認為適中的復雜設計可以運行于所選的FPGA,然后對這個數進行四舍五入至最接近的整數。通過這個計算因子,可以減少乘法器的數目。作為一個例子,假設要在LatticeECP2 FPGA中實現12個抽頭,75MSPS,12位的濾波器。用這個器件,300MHz的濾波器比較容易實現,減少因子為4,需要3個乘法器。

在做出最后決定之前,要考慮最終的實現。例如,使用Lattice提供的FIR產生器,這個工具用sysDSP塊內的加法樹實現FIR濾波器。因為這個加法樹的范圍是4個乘法器,沒有有效的資源與指定的3個乘法器聯系在一起。此外,如果指定了4個乘法器,設計要求的工作速度會略有降低。

現在有了系數,乘法器實現的方法,以及知道需要多少個乘法器。許多供應商,包括Lattice提供自動產生FIR的工具。最后一步是把系數輸入工具,指定乘法器的數目。產生濾波器之后要進行時序分析,確定是否假設的速度是正確的。在使用的例子中,工具報告了350MHz的最大速度,高于假設的300MHz。如果速度非常接近,你應該進行調整并再試。

評論