用低成本FPGA實(shí)現(xiàn)低延遲變化的CPRI

引言

本文引用地址:http://www.104case.com/article/201706/349341.htm無(wú)線TEM(電信設(shè)備制造商)正受到布署基站架構(gòu)的壓力,這就是用更小體積、更低功耗、更低制造成本來(lái)建立,部署和運(yùn)營(yíng)。達(dá)到此目的的關(guān)鍵策略是從基站中分離出RF接收器和功率放大器,用它們來(lái)直接驅(qū)動(dòng)各自的天線。這稱為射頻拉遠(yuǎn)技術(shù)(RRH)。通過(guò)基于SERDES的公共無(wú)線接口(CPRI)將基帶數(shù)據(jù)傳回到基站。本文主要闡述特定的低延遲變化的設(shè)計(jì)思想,在低成本FPGA上利用嵌入式SERDES收發(fā)器和CPRI IP(知識(shí)產(chǎn)權(quán))核實(shí)現(xiàn)。

RRH的部署

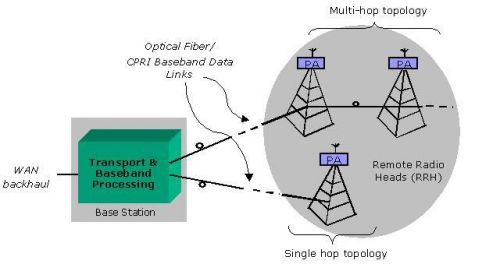

從“Hotel”基站分離射率(RF)收發(fā)器和功率放大器的優(yōu)點(diǎn)已經(jīng)寫(xiě)得很多了,如圖1所示。但最引人注目的是RRH在功耗、靈活部署、小的固定體積,以及整個(gè)低成本方面的優(yōu)點(diǎn)。

圖1 射頻拉遠(yuǎn)技術(shù)(RRH)方案

隨著RRH從基站里分散出來(lái),運(yùn)營(yíng)商必須確保能夠校準(zhǔn)無(wú)線頭和hotel BTS之間的系統(tǒng)延時(shí),因?yàn)檠訒r(shí)信息是用于系統(tǒng)校準(zhǔn)的,必須使整個(gè)來(lái)回行程延時(shí)最短。隨著級(jí)聯(lián)的RRH,添加了每個(gè)RRH跳的變化,因此這個(gè)要求相應(yīng)增加,針對(duì)單程和來(lái)回行程,CPRI規(guī)范處理這些鏈路時(shí)序的精確性。

針對(duì)低延遲變化的FPGA實(shí)現(xiàn)

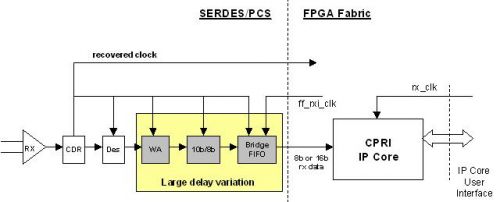

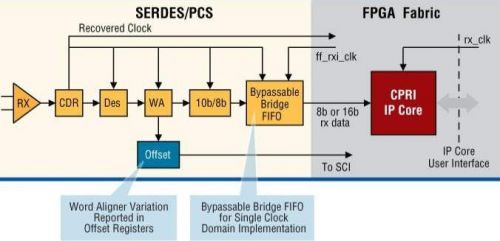

圖2展示了現(xiàn)有的在傳統(tǒng)SERDES/PCS實(shí)現(xiàn)中的主要功能塊,加亮的部分突出了引起延時(shí)變化的主要部分(如例子中展示的RX路徑)

圖2 傳統(tǒng)的CPRI接收器實(shí)現(xiàn)方案

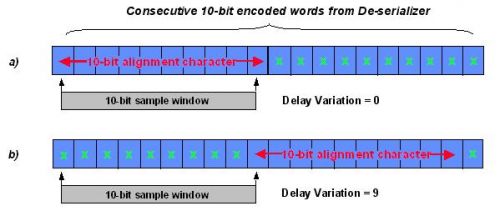

延時(shí)變化來(lái)自幾個(gè)單元,諸如模擬SERDES和數(shù)字PCS邏輯,以及實(shí)際的軟IP本身。模擬SERDES有相對(duì)緊湊的時(shí)序;然而,字對(duì)齊和 橋接FIFO是兩個(gè)主要的引起大的延時(shí)變化的原因。提出一個(gè)解決方案前,重要的是理解為什么字對(duì)齊和橋接FIFO有這么大的影響。如圖3所示,字對(duì)齊功能會(huì)導(dǎo)致多達(dá)9位周期的延時(shí)變化,這取決于10位周期內(nèi)字對(duì)齊指針的初始位置。如果10位采樣窗很好地捕獲了對(duì)齊字符,例如圖3中的a)那就沒(méi)有延時(shí)。然而如果采樣窗沒(méi)有與字符對(duì)齊,導(dǎo)致多達(dá)9位周期的延時(shí),如圖3中的b)所示。

圖3 字對(duì)齊的延時(shí)變化

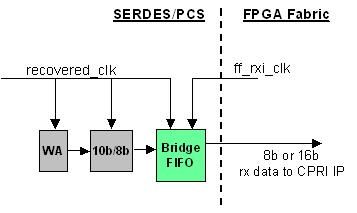

第二,采用基于SERDES的FPGA混合結(jié)構(gòu),還需要橋接FIFO(圖4)來(lái)支持時(shí)鐘域的轉(zhuǎn)換,從高速PCS時(shí)鐘到FPGA時(shí)鐘域,可以引進(jìn)多達(dá)2個(gè)并行時(shí)鐘周期的延時(shí)變化。2.488Gbps的速率,PCS時(shí)鐘以十分之一的速率運(yùn)行,這個(gè)速率產(chǎn)生4ns左右的時(shí)鐘周期。因此,可以看到在FIFO (Tx Rx)的每個(gè)方向有+/-8ns變化的最壞情況,導(dǎo)致總的+/-16ns的變化。

圖4 源于橋接FIFO的延時(shí)變化

設(shè)計(jì)者沒(méi)有看到到這些延時(shí)變化時(shí),這個(gè)情況會(huì)更糟糕。因?yàn)樗鼈冃枰谙到y(tǒng)級(jí)進(jìn)行補(bǔ)償,以支持多種Tx和GPS服務(wù)。

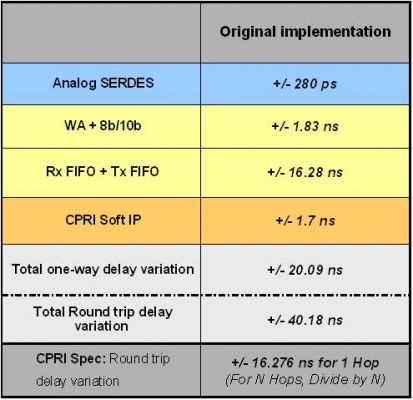

表1對(duì)CPRI規(guī)范(3.5節(jié))做了延時(shí)變化的比較。可以很清楚地看到字對(duì)齊和橋接FIFO對(duì)大的延時(shí)變化起的主要作用,導(dǎo)致來(lái)回行程延時(shí)容差超過(guò)CPRI規(guī)范。

表1 在原設(shè)計(jì)中延時(shí)變化的元件

一旦確定了問(wèn)題,就可以做一些較小的修改。某些實(shí)現(xiàn)中,通過(guò)訪問(wèn)寄存器的方式可以獲得PCS中字對(duì)齊測(cè)量得到的延時(shí)信息,可以繞過(guò)時(shí)鐘域FIFO,用FPGA邏輯來(lái)實(shí)現(xiàn),在系統(tǒng)級(jí)可以針對(duì)延時(shí)變化進(jìn)行補(bǔ)償。圖5說(shuō)明了具有可補(bǔ)償?shù)年P(guān)鍵延時(shí)變化的低延時(shí)設(shè)計(jì)。

圖5 低延遲時(shí)間實(shí)現(xiàn)

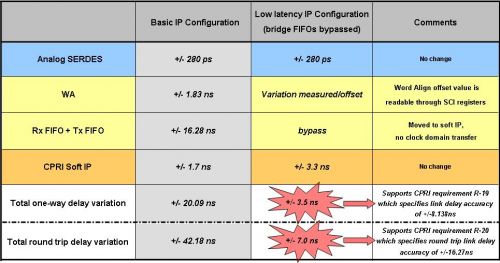

現(xiàn)在做一個(gè)總結(jié),當(dāng)使用所推薦的實(shí)現(xiàn)方法時(shí),引起大的延時(shí)變化的單元消失了,可以利用系統(tǒng)級(jí)補(bǔ)償,以確保在傳輸期間預(yù)期的延時(shí)。當(dāng)然模擬SERDES 和IP,或者客戶設(shè)計(jì)仍然有延時(shí),但是已經(jīng)大大改進(jìn)了整個(gè)精確性,現(xiàn)在可以在多跳應(yīng)用中使用。表2說(shuō)明了在這個(gè)配置中新的延時(shí)變化。現(xiàn)在時(shí)序滿足了來(lái)回行程CPRI延時(shí)規(guī)范,對(duì)支持多跳的應(yīng)用來(lái)說(shuō)是足夠的短。

表2 在低延遲實(shí)現(xiàn)中的延時(shí)變化

使用FPGA的另外一些優(yōu)點(diǎn)

許多年來(lái)FPGA是無(wú)線工業(yè)獲得成功的一部分。從簡(jiǎn)單的粘合邏輯功能到更復(fù)雜的功能,例如在如今RRH設(shè)計(jì)中所需要的數(shù)字上變頻、數(shù)字下變頻、峰值因子衰減和數(shù)字預(yù)失真,充分利用了FPGA的靈活性和產(chǎn)品快速上市的優(yōu)點(diǎn)。支持CPRI互聯(lián)的特性,諸如嵌入式DSP塊、嵌入式存儲(chǔ)器和高速串行I/O (SERDES)的特性已與無(wú)線設(shè)備供應(yīng)商的新需求完美地吻合。現(xiàn)在基站設(shè)計(jì)者可以在低成本、低功耗可編程平臺(tái)上,如用Lattice ECP3 FPGA集成系統(tǒng)級(jí)的功能。

總結(jié)

遠(yuǎn)程基站拓?fù)浣Y(jié)構(gòu)為系統(tǒng)供應(yīng)商提供了許多優(yōu)點(diǎn),F(xiàn)PGA對(duì)實(shí)現(xiàn)這些需要是理想的方法。因此,使用可編程、低功耗、低成本中檔FPGA解決方案是下一代BTS開(kāi)發(fā)的最好的方法。

發(fā)布者:小宇

評(píng)論