基于FPGA的半導體激光器自動功率控制系統設計

自從激光器在1960年發明以來,在激光通信中已經成為了不可或缺的關鍵設備,半導體激光器(LD)是用于高速率光傳輸系統的有吸引力的光源,然而,遺憾的是LD的閾值隨溫度和壽命變化,且因器件的不同表現出現較大的差異。LD的閾值隨著溫度的升高而明顯增大。LD閾值的漂移,給使用帶來很大的不便,如果采用固定的偏流,則必然引起輸出光脈沖峰值功率的浮動,而且,閾值的漂移破壞了已經設計好的工作點,從而引起有害光電延遲、張弛振蕩等現象。在LD高速工作時,這種現象的危害是不可忽視的。為了克服這些弊病,必須對輸出功率進行控制,使LD的工作能夠維持在正確的工作點上。

姚嘉陵等曾設計基于模擬電路的APC自動激光功率控制電路,通過反饋來自動調整預偏置電流來達到穩定LD輸出功率的控制。基本原理是一方面將LD背向輸出的光功率經背向光探測器PD進行檢測,然后經過放大器1進行放大,送到比較器的反相輸入端;另一方面,輸入信號和從直流穩壓電源中取出的直流參考電壓經過放大器2放大后送入比較器的同相輸入端,比較器的輸出作為反饋被送到LD的驅動端,調節偏流,達到穩定LD輸出功率的目的。

模擬電路方法實現的優點是增益控制比較穩定,缺點是需要加入的器件較多,且隨著使用時間的增加,模擬器件老化會影響反饋控制的誤差,另外,輸出的激光功率固定不可變,不能實現多級功率的控制。

筆者提出一種基于FPGA的全數字激光器功率自動控制系統,不但可以大大簡化電路結構,減少成本,同時消除由器件老化帶來誤差,還可以方便的改變激光器的輸出功率和實現激光器多級功率的控制。

1 自動功率控制系統整體結構

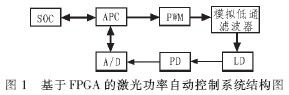

基于FPGA的激光功率自動控制系統結構如圖1所示其工作原理是:將半導體激光器LD背向輸出的光功率經背向光探測器PD進行檢測后,轉換成模擬電壓信號,該模擬電壓信號經過A/D轉換芯片的采樣和轉換,轉換成代表LD實際輸出功率的數字信號,該數字信號被送入FPGA芯片中的APC(自動功率控制模塊)進行分類、比較和處理,最終輸出調整后的激光器數字偏流信號,數字偏流信號經過FPGA內部的PWM模塊和外部的模擬低通濾波器轉換成模擬信號,來驅動半導體激光器LD。SOC用于設置多級激光器輸出功率設置,APC的工作、停止等控制。

如圖1所示,本文所設計的全數字激光器自動功率控制系統由A/D轉換器、FPGA功能設計模塊和模擬低通濾波器3個部分組成。

2 FPGA模塊設計

本設計使用的是Avnet Design Services公司設計的FPGA評估板,該評估板使用的是Xilinx公司XC4VLX25-FF668型FPGA芯片。同時,板上還有32MB的DDR SDRAM和8MB的Intel StrataFlash,10/100M自適應以太網接口、USB2.0接口和RS232串行接口,128x64的OLED(Organic Light Emitting Diode)圖形顯示,3組140針通用I/O連接器(AvBus)等硬件結構組成。

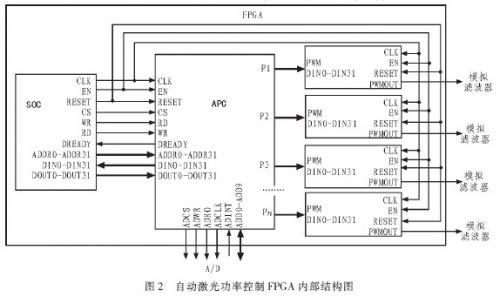

如圖2所示,本文中FPGA設計包括3個部分,SOC、APC和PWM。

SOC是采用的由GaislerResearch公司于2003年研制完成的一款32位、符合IEEE-1754(SPARCVS)結構的免費CPU處理器核Leon2。它的前身是歐空局研制的Leon以及ERC32。Leon2的目標主要是權衡性能和價格、高的可靠性、可移植性、可擴展性、軟件兼容性等,其內部硬件資源可裁剪(可配置)、主要面向嵌入式系統,可以用FPGA/CPLD和ASIC等技術實現。Leon2處理器的片上資源如下:分離的指令和數據Cache、硬件乘法器和除法器、中斷控制器、具有跟蹤緩沖器的調試支持單元(DSU)、2個24位定時器、2個通用異步串口(UART)、低功耗模式、看門狗電路、16位I/O端口、靈活的存儲控制器、以太網MAC和PCI接口。Leon2的VHDL模塊可以在大多數綜合工具上進行綜合,可以在任何符合VHDL-87標準的仿真器上進行仿真;采用AMBA AHB/APB總線結構的用戶設計新模塊,可以很容易加入到Leon2中,完成用戶的定制應用。其結構如圖3所示。

文中SOC主要實現的功能是控制各個子系統的復位(RESET)與使能(EN),為各個子系統提供時鐘信號(CLK),并可以通過讀(RD)、寫(WR)、片選(CS)3個控制信號、32位的數據輸入總線(DIN0~DIN31)、32位的輸出數據總線(DOUT0~DOUT31)、32位的地址總線(ADDR0~ADDR31)與各個子系統進行讀、寫操作。對于APC子系統,SOC主要完成APC模塊和PWM模塊的系統復位、使能,為APC模塊、PWM模塊提供時鐘,設置APC模塊的控制、狀態寄存器等功能。

APC結構是激光功率自動控制系統的主體結構。主要功能有兩個:1)完成對A/D芯片的控制,包括A/D芯片工作方式的設定(通過設置A/D芯片的控制寄存器)、A/D芯片的控制信號的產生(時鐘信號ADCLK、使能信號ADCS、讀控制信號ADRD、寫控制信號ADWR、并接收A/D轉換完成信號ADINT和A/D轉換結果ADD0~ADD9);2)對A/D轉換的結果(ADD0~ADD9)進行處理,即將采樣并轉換的激光發射器的輸出功率與設置的多級功率進行比較,區分出功率等級,再將標準等級的功率值與實際采樣轉換功率值進行比較,并根據比較結果給出新的LD驅動功率值。

PWM是根據APC模塊輸出的新的LD驅動功率值,通過調制方波的占空比來改變輸出的直流分量,經過低通濾波器后得到需要的模擬電壓信號,來驅動LD。使用PWM模塊一可以用數字電路設計取代昂貴的D/A轉換器,二是可以靈活的增加或減少被控制LD的數量。

3 自動激光功率控制設計的A/D轉換模塊設計

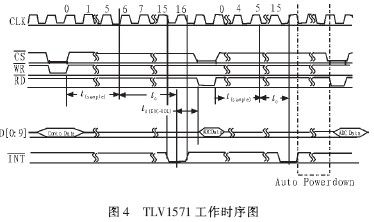

本設計中的模/數轉換芯片選用的是TI公司生產的TLV1571芯片,TLV1571是一款10位單通道模擬輸入的模/數轉換器,內部有兩個8位的控制寄存器CR0、CR1來控制ADC的工作模式,包括軟件轉換或硬件轉換開始選擇、內部或外部時鐘選擇、二進制或二進制補碼輸出、硬件或軟件配置等工作模式。本設計通過將TLV1571的兩個控制寄存器設置在外部時鐘信號,軟件控制轉換工作方式,其工作時序如圖4所示。

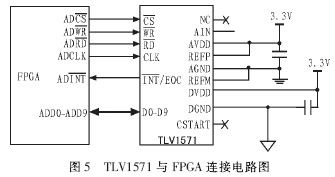

當CS和WR信號均為低電平時,寫TLV1571的控制寄存器,設置完TLV1571的控制寄存器后,在WR的上升沿開始A/D采樣,采樣持續6個時鐘周期后,自動進行A/D轉換,轉換需要10個時鐘周期,轉換完成后,INT變低,通知FPGAA/D轉換已經完成,同時,將AD轉換后的數字信號在D0~D9數據總線上準備好,在RD信號的下降沿,數據被讀入FPGA內進行下一步處理。TLV1571的時鐘信號CLK、CS、WR、RD均由FPGA產生。D0~D9與FPGA的10個雙向I/O端口相連,用于完成TLV1571兩個控制寄存器的設置以及A/D轉換結果的傳遞。圖5為TLV1571與FPGA連接電路圖。

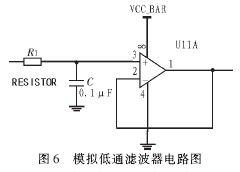

4 模擬低通濾波器的設計

本設計的模擬低通濾波器采用簡單的一階有源濾波器,其電路結構如圖6所示。

5 結束語

選擇半導體激光器LC25,設定輸出功率要求為2 W,PD采用InGaAs PIN光電探測器,PD檢測的結果既用于自動功率控制的輸入,還作為自動功率控制的結果檢驗。如果自動功率控制良好,則PD的輸出將穩定在額定值上。利用泰克示波器對PD檢測信號進行檢測,本文設計的自動功率控制實現了對半導體激光器輸出功率的穩定控制。

本文設計的新型全數字自動激光功率控制設計應用FPGA設計使用硬件資源少,節約成本;可以通過設置相應功率等級寄存器的值就可以很容易的改變功率等級劃分的標準,大大增加了功率控制的靈活性;通過增加PWM模塊和簡單的模擬器件,就可以實現多個激光器的控制,大大縮短設計周期。

評論