基于Xilinx FPGA的DCM動態重配置方法研究及實現

在復雜的電子系統應用中,系統的主時鐘經常需要根據不同的應用環境,采用不同頻率、不同相位的高速時鐘,以滿足系統的不同性能要求。在星載系統中,其不同接口的數據輸入速率不同,為了實現FPGA對不同接口輸入數據的實時復用處理,需要電子系統產生對應的時鐘頻率。DCM(Digital Clock Manager)被廣泛應用于電子系統中以產生所需的各種時鐘頻率,所以在系統動態可變時鐘的過程中,DCM的重配置設計很重要。

DCM的配置分為簡單的靜態配置和復雜的動態重配置兩種:靜態配置是指DCM的輸出頻率是事先確定好的,在系統的整個運行過程中不會改變,若要改變,必須停止系統對其進行重新手動設置,這對于星載系統而言,難度非常大;而動態重配置是指在系統運行過程中,通過發送指令便可以實時地通過改變DCM屬性來產生特定需要的時鐘頻率,這對于星載系統而言,具有十分重要的實際意義。文中結合作者的項目研發體會,對Xilinx公司的Virtex-4系列FPGA(Field Programmable Gate Array)的數字時鐘管理器DCM的性能特點作了介紹,并給出進行DCM動態重配置的方法,從而使系統時鐘具有較高的靈活性和適應性。

1 DCM概述

Virtex-4系列FPGA是Xilinx公司推出的新一代大容量、高性能FPGA。在Virtex-4系列FPGA內部最多集成了20個時鐘管理器DCM模塊,DCM提供了一個完整的可以供片內和片外使用的時鐘發生器。DCM使用完全數字延遲線技術,允許高精度地控制時鐘的相位和頻率;使用完全的數字反饋系統,可以動態補償由于溫度和電壓偏移引起的時鐘相位和頻率的偏差。DCM主要具有數字時鐘同步、數字頻率合成、數字相位移動和動態重配置4個基本功能。

Virtex-4的DCM基本單元分為DCM_BASE和DCM_ADV兩種,如圖1所示,而DCM_ADV具有時鐘動態重配置功能。

DCM_BASE基本單元包含常用的DCM基本功能,簡化了用戶接口。使用DCM_BASE,可以完成對時鐘去歪斜、進行頻率合成和固定相移的功能。

DCM_ADV基本單元除包含DCM_BASE中所有DCM功能和可用端口之外,還包含具有動態重配置功能的端口。DCM_ADV基本單元是DCM_BASE基本單元的擴展。DCM_ADV包括所有DCM功能,包括時鐘去歪斜、頻率合成、固定或可變相移以及動態重配置。

2 DCM動態重配置的設計和實現

通過DCM的一組數據和地址總線,在不必重新配置器件其他部分的情況下,改變DCM的屬性。用于動態重配置DCM功能的引腳有:輸入引腳DADDR[6:0],DI[15:0],DWE,DEN和DCLK;輸出引腳DO[15:0]和DRDY。動態重配置可以根據目前的配置設定實現修改DCM的屬性,改變其相移、倍頻系數M或分頻系數D。

2.1 動態重配置DCM的原理

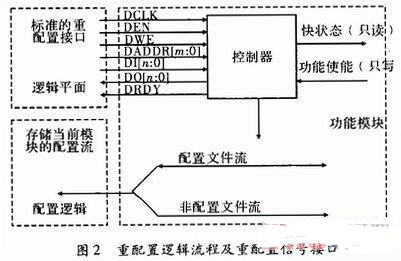

DCM的動態重配置功能通過動態重配置引腳(Dynamic Reconfiguration Ports,DRP)控制器完成,其不僅可以配置DCM,而且可以配置FPGA的其他邏輯。動態重配置邏輯塊的重配置流程和配置信號接口如圖2所示。

對于Virtex-4的DCM,倍頻系數M的值是通過DRP往指定地址(DADDR[6:0])50h中寫數DI[15:0]來實現的,分頻系數D的值是通過DRP往指定地址(DADDR[6:0])52h中寫數DI[15:0]來實現的。在寫控制字的過程中,DCM必須保持Reset狀態。地址(DADDR[6:0])41h的位6(DI[5])用于設置DFS的頻率模式,0是低頻工作模式,1是高頻工作模式;地址58h的位7和位8(DI[7:6])用于設置DLL的頻率模式,00是低頻模式,11是高頻模式;地址00h用于存儲DCM的默認輸出狀態。

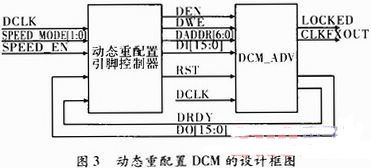

2.2 系統設計

如圖3是系統設計的邏輯框圖。它由動態重配置引腳控制器和DCM_ADV組成。其動態重配置引腳控制器的輸入簡單,包括時鐘輸入信號、使能信號以及兩根時鐘模式控制線,它可以控制DCM動態的輸出最多4種不同頻率的時鐘。時鐘模式控制線可以擴展為多位,從而產生多種不同頻率的時鐘,在這里只采用兩根模式控制線產生4個時鐘模式值。

該系統的工作原理:動態重配置引腳控制器不斷地輸入DCLK頻率采樣時鐘等級值,當SPEED_MODE[1:0]有有效地輸入并且SPEED_EN使能信號為高電平時,動態重置引腳控制器開始產生對應的DCM重配置輸入參數。DCM根據重配置參數來動態的產生所需的時鐘頻率,并向動態重置引腳控制器反饋動態重配置就緒信號和動態重配置數據輸出信號,從而為下一次的時鐘配置做好就緒準備。DCM_ADV模塊的CLKFX_OUT是動態重配置后DCM的輸出時鐘,LOCKED信號出指示DCM時鐘輸出是否有效,即是否輸出正確的頻率和相位。這樣只需改變輸入的時鐘模式值而不需其他改動,便可產生所需的時鐘頻率,從而使得系統時鐘具有較高的靈活性和適應性。

2.3 動態DCM重配置的時序設計

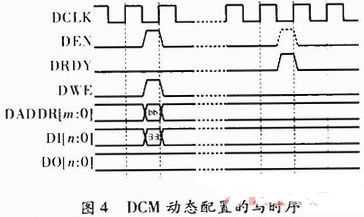

在整個系統中,配置接口的時序設計是最關鍵的。在ISE10.1軟件設計環境下,使用VerilogHDL硬件描述語言以自頂向下的方式進行設計。圖4是DCM模塊接口動態重配置的寫時序。

其中,DCLK是其他接口信號的驅動時鐘,在上升沿同步工作;DEN是其他接口的使能信號;DWE是讀/寫控制信號,如果DWE是低電平,為讀操作,否則就是寫操作;DADDR是讀/寫地址總線;DI是數據輸入總線,只有當DEN和DWE同時有效時數據輸入有效,而且實際的寫操作是在DRDY返回之前的某個時刻發生的;DO是數據輸出總線;DRDY是與DEN對應的一個信號,標志著一個DRP操作周期的完成,DO總線數據要在DRDY有效時間內DCLK的上升沿讀取才有效。

動態重配置引腳模塊的總體設計包括DCLK產生、重配置引腳的產生、RST信號產生。DCLK的產生是通過對輸入時鐘100 MHz的晶振進行2.5分頻得到,作為后一級DCM模塊的動態重配置時鐘40 MHz;重配置引腳的產生是根據輸入的時鐘等級值來產生的,在不同的時鐘等級值下產生對應的DEN、DWE、DADDR[6:0]、DI[15:0];RST信號的產生是根據DEN來產生的,這里使它持續的時間比DEN稍長即可。由于對應的時鐘等級值300 MHz是屬于高頻模式,而200 MHz、100 MHz、50 MHz是屬于低頻模式,故在改變其時鐘等級值的同時還需要對對應時鐘等級值的頻率模式進行改變。

對于可重配置功能,在操作時要注意兩點:一是需要動態改變的CLKFX的乘數M和除數D的值要先減去1,例如希望分頻比是5/2,就需要載入M/D=4/1;在寫入動態控制字時,要保持DCM處于復位狀態,直到控制字寫完后才釋放復位狀態。

3 在線采集波形

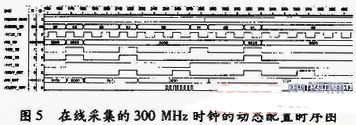

以上的各模塊在ISE 10.1開發平臺上進行設計輸入,經綜合、實現后下載到XC4VFX100中去。在動態配置300 MHz時鐘頻率時,通過ChipScope實際在線采集波形如圖5所示,對應其他的頻率等級的重配置類似。

在對300 MHz的頻率進行時鐘等級值配置時,先向地址50h中寫入倍頻系數0002h,再向地址52h中寫入分頻系數0000h;在對頻率模式配置時,對地址(DADDR『6:0])41h的位6(DI[5])置為數1。在向地址中寫數期間保持DEN、DWE的電平為高,并且在對時鐘等級配置和頻率模式配置時,保持DCM的復位信號處于復位狀態。從圖5中可以看出,在輸入速度等級值時,被DCLK正確采樣后,動態重配置控制器便產生相對應的引腳參數,這時對DCM開始重配置。DRDY信號反饋顯示上次的動態重配置完畢,可以進行下一次的重配置。在配置完成后,CLKFX_OUT是動態重配置的輸出時鐘。通過ChipScope的實際在線采集,其動態重配置后的時鐘頻率CLKFX_OUT符合預期重配置結果。

系統時延和相移都默認設置為零,經實際測試,整個動態變頻過程最多只需要20個DCLK周期就可以完成,DCLK采用的是40 MHz,所以只需要不到1μs的時間便可對DCM重配置完畢,體現了系統很強的實時性。

4 兩種DCM配置方法的分析比較

對于該系統而言,若想通過靜態配置來產生300 MHz、200 MHz、100 MHz、50 MHz的輸出時鐘頻率,由于300 MHz是高頻模式,而200 MHz、100 MHz、50 MHz的時鐘是低頻模式。為得到這幾種時鐘頻率,則需要兩個DCM來實現,一個采用低頻模式,另一個采用高頻模式,通過DCM事先設定好的倍頻和分頻來實現,并且還需要根據輸入數據頻率的不同來選擇對應的時鐘頻率。這種方法靈活性差,并且在數據分時復用處理時還需要根據輸入時鐘頻率的情況進行時鐘控制和選擇,其可調節能力非常的弱,并且耗費的資源較多,在數據處理的分時復用時會有時鐘閑置的情況,不利于系統節能的要求。此外對系統時鐘的控制,其時鐘頻率穩定性較差,且時鐘的質量較差。

通過DCM重配置生成的時鐘頻率,可以按需要成比例地調節,不必對時鐘的控制和選擇便可滿足實際的需要,系統具體需要什么樣的時鐘頻率便產生對應的時鐘,這對于有多種時鐘頻率的產生更具有重要的實際意義,并且可以通過發送指令來改變時鐘頻率的相位情況,方便易操作。通過DCM的動態重配置,可以實現對FPGA資源的利用較少,資源的利用少有利于系統的節能,這對于星載系統而言是具有重要的實際意義。目前該系統已應用于某星載系統,其運行狀態穩定且良好,具有較強的實時性和靈活性。

5 結束語

動態重配置DCM在FPGA電路設計領域有著廣泛的應用,文中系統介紹了基于Virtex-4的DCM動態重配置設計方案,給出了一個在工程中可以廣泛應用的實際系統實例。對該動態重配置系統在不同輸入時鐘等級值下的輸出時鐘信號頻率進行了在線采集測試,信號的波形和頻率達到系統要求的性能指標,并且對其性能做出了比較分析。

評論