FPGA最小系統(tǒng)之:硬件系統(tǒng)的調(diào)試方法

隨著FPGA芯片的密度和性能不斷提高,調(diào)試的復(fù)雜程度也越來(lái)越高。BGA封裝的大量使用更增加了板子調(diào)試的難度。所以在調(diào)試FPGA電路時(shí)要遵循一定的原則和技巧,才能減少調(diào)試時(shí)間,避免誤操作損壞電路。

本文引用地址:http://www.104case.com/article/201706/348849.htm一般情況下,可以參考以下步驟進(jìn)行FPGA硬件系統(tǒng)的調(diào)試。

(1)首先在焊接硬件電路時(shí),只焊接電源部分。使用萬(wàn)用表進(jìn)行測(cè)試,排除電源短路等情況后,上電測(cè)量電壓是否正確。

(2)然后焊接FPGA及相關(guān)的下載電路。再次測(cè)量電源地之間是否有短路現(xiàn)象,上電測(cè)試電壓是否正確,然后將手排除靜電后觸摸FPGA有無(wú)發(fā)燙現(xiàn)象。

如果此時(shí)出現(xiàn)短路,一般是去耦電容短路造成,所以在焊接時(shí)一般先不焊去耦電容。FPGA的管腳粘連也可能造成短路,這時(shí)需要對(duì)比電路圖和焊接仔細(xì)查找有無(wú)管腳粘連。

如果出現(xiàn)電壓值錯(cuò)誤,一般是電源芯片的外圍調(diào)壓電阻焊錯(cuò),或者電源的承載力不夠造成的。若是后者,則需要選用負(fù)載能力更強(qiáng)的電源模塊進(jìn)行替換。如果FPGA的I/O管腳與電源管腳粘連,也可能出現(xiàn)電壓值錯(cuò)誤的現(xiàn)象。

如果出現(xiàn)FPGA發(fā)燙,一般是出現(xiàn)總線沖突的現(xiàn)象。這種情況下需要仔細(xì)檢查外圍總線是否出現(xiàn)競(jìng)爭(zhēng)問題。特別是多片存儲(chǔ)器共用總線時(shí)候,比如ASRAM和Flash芯片復(fù)用一套總線,如果片選信號(hào)同時(shí)有效就出現(xiàn)總線的沖突。

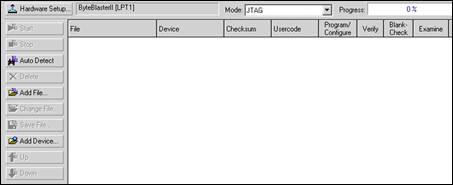

(3)以上步驟均通過(guò)后,將電路板上電運(yùn)行。然后把下載電纜接到JTAG接口上,在主機(jī)中運(yùn)行Quartus II軟件,并打開Programmer編程器,單擊其中的“Auto Detect”按鈕進(jìn)行FPGA下載鏈路自動(dòng)檢測(cè)。若能正確檢測(cè)到FPGA,說(shuō)明配置電路是正確連接的。

自動(dòng)檢測(cè)FPGA下載鏈路如圖2.28所示。

圖2.28 自動(dòng)檢測(cè)FPGA下載鏈路

(4)焊接時(shí)鐘電路、復(fù)位電路及數(shù)碼管電路,并向FPGA下載一個(gè)數(shù)碼管跑馬燈程序。若程序能夠正確運(yùn)行,說(shuō)明FPGA已經(jīng)可以正常工作了。

(5)最后焊接所有其他電路,并進(jìn)行整體功能測(cè)試。

評(píng)論