FPGA設計開發軟件Quartus II的使用技巧之: LogicLock邏輯鎖定工具使用技巧

5.8LogicLock邏輯鎖定工具使用技巧

5.8.1邏輯鎖定方法學

邏輯鎖定方法學(LogicLockMethodology)內容就是在設計時采用邏輯鎖定的基于模塊設計流程(LogicLockblock-baseddesignflow),來達到固定單模塊優化的目的。這種設計方法學中第一次引入了高效團隊合作方法:它可以讓每個單模塊設計者獨立優化他的設計,并把所用資源鎖定。

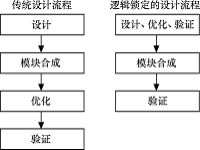

本文引用地址:http://www.104case.com/article/201706/348819.htm這樣在合成頂層設計時就可以保持每個模塊的性能,而且它還讓邏輯模塊可重復使用,提高了資源利用率,縮短了設計周期。邏輯鎖定的基于模塊設計流程與傳統設計流程對比如圖5.37所示。

圖5.37兩種設計流程比較

5.8.2邏輯鎖定優勢

性能不變,而設計周期更短。使用LogicLock約束,邏輯模塊只需優化一次。通過約束達到性能要求后,LogicLock區域的回傳機制將此性能指標保持不變。例如,設計人員可以在設計中使用一個PCI宏函數,鎖定布局和性能指標。在設計中,加入其他邏輯模塊或者在其他區域中改變邏輯都不會影響PCI核的性能。LogicLock流程減少了完成一個工程所需的設計周期數量。

更強的分層次設計流程。設計人員通過LogicLock流程,可以保持每個模塊的特性不變,通過分層次區域實施很快地達到性能指標。采用LogicLock方法學,設計人員或者設計團隊可以在設計中獨立工作,完成布局布線,優化和對每個設計模塊的驗證。在集成階段,只需對整個系統進行驗證。布局和每個模塊的性能保持不變。

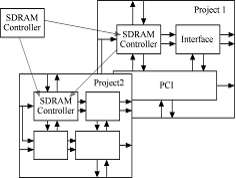

優化的設計重復使用流程。LogicLock約束可以由外部輸入。由于LogicLock方法允許將單個約束過的設計模塊輸入到多個設計中去,因此設計可以方便地重復使用。如圖5.38所示為工程師獨立開發的模塊在多個工程中使用的例子,模塊在每個實施中都有相同的性能。

圖5.38LogicLock設計的重復使用

5.8.3邏輯鎖定參數設置

LogicLock區域參數設置在LogicLock區域中,設計人員可以控制布局。這些區域為真正的分層次設計提供基本構架,設計中改變一個模塊不會影響到區域中其他模塊的性能。表5.4所示為控制LogicLock區域行為的各種參數含義。默認的選項分別是浮動、自動、關閉和硬區域。

表5.4 LogicLock區域參數

參數 | 選項 | 特征 |

狀態 | 浮動、鎖定 | 浮動區允許QuartusII軟件決定器件上的區域位置。鎖定區是區域中用戶定義的位置,在圖形平面配置圖上以實線邊界標出,鎖定區必須有固定的大小 |

大小 | 自動、固定 | 自動大小區允許QuartusII軟件決定區域的合適大小,固定區域含有用戶定義的形狀和大小 |

保留 | 關閉、打開 | 保留特性允許用戶定義區域中的資源能否用于沒有分配給區域的實體。如果保留打開,則只有分配給區域的項目才可以在區域內布放 |

執行 | 硬、軟 | 軟區域有更寬松的時間約束,允許總設計的性能提高后,將一些實體置于區域之外。硬區域不允許將內容放置在區域邊界之外 |

原點 | 平面配置圖的任一位置 | 原點定義為LogicLock區域放置在平面配置圖上時其左上角位置 |

5.8.4邏輯鎖定流程

首先,分析整體資源利用率,如果采用的FPGA芯片容量足夠,理論上只要保證重點模塊的資源利用率,就能保證整體設計的性能;然后采用邏輯鎖定的基于模塊設計流程(LogicLockblock-baseddesignflow)進行設計,步驟如下。

(1)在Quartus®中綜合單個底層模塊。

(2)優化重點模塊,進行邏輯鎖定。

(3)反標(back-annotaing)。

(4)導出模塊邏輯鎖定約束信息,包括原級網表(atomnetlist)文件(.vqm)、布局信息(placementinformation)文件(qsf)和布線信息(routinginformation)文件(.rcf)。

(5)將這些約束文件導入頂層(top-level)工程中。

(6)編譯和驗證整個頂層設計。

(7)編譯完成后,查看時序分析界面是否達到要求。

以上介紹的邏輯鎖定的具體方法可以參照5.11小節。

通過應用一種新的設計方法學——邏輯鎖定方法學(LogicLockMethodology),采用了模塊化、團隊化的設計流程,對重點模塊進行優化,解決了傳統設計流程無法解決的問題,同時對其他FPGA設計工程中類似的問題提供了可借鑒的思路。

評論