基于FPGA的片上可編程系統(SOPC)設計之:典型實例-基于NIOS II處理器的“Hello LED”程序設計

8.4典型實例14:基于NIOSII處理器的“HelloLED”程序設計

8.4.1實例的內容及目標

1.實例的主要內容

本節旨在通過給定的工程實例——“HelloLED”來熟悉Altera軟嵌入式系統的軟硬件設計方法。同時使用基于AlteraFPGA的開發板將該實例進行下載驗證,完成工程設計的硬件實現。本節主要講解下面一些知識點。

·QuartusIISOPCBuilder使用方法。

·NIOSIIIDE軟件開發流程。

通過這些知識點,按照本節實例的實現過程,讀者可以迅速掌握Altera軟嵌入式軟硬件設計方法。

2.實例目標

通過詳細的流程講解,讀者應達到下面的目標。

·熟悉QuartusIISOPCbuilder使用方法。

·熟悉NIOSIIIDE軟件設計方法。

8.4.2實例詳解

本實例使用圖解的方式將整個流程一步一步展現給讀者,使讀者能夠輕松掌握開發的流程。

本實例重點在于熟悉使用QuartusⅡ和SOPCBuilder來創建一個NiosⅡ嵌入式處理器系統,并通過軟件編程實現對實驗板上面的LED燈的控制,具體實現過程如下。

(1)新建工程。

新建一個工程目錄“sopc_led”,在此目錄下建立一個名為“sopc_led”的QuartusII工程,并新建一個頂層圖,保存于工程中。

(2)SOPCBuilder定制NIOSII處理器。

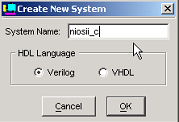

用SOPCBuilder定制NiosII處理器及其外設。打開“Tools”/“SOPCBuilder”,如圖8.30所示。

圖8.30打開Tools--SOPCBuilder

指定系統名字,本例中我們輸入niosii_c。單擊“OK”按鈕進入SOPC定制界面。

圖8.31SOPCBuilder界面

為“Target”選擇“UnspecifiedBoard”,為“Clock(MHz)”選擇時鐘頻率為50.0,為“TargetDeviceFamily”選擇目標器件系列為Cyclone。

在SOPC定制界面的左邊,我們可以看到有很多功能模塊,用戶可以按照需要將這些模塊添加到所設計的系統中。

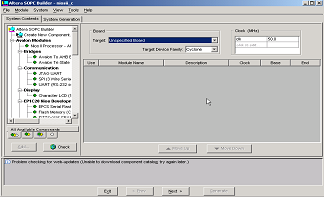

首先,我們需要一個CPU。選擇“NiosIIProcessor”/“AlteraCorporation”,彈出AlteraNiosII對話框,我們選擇一個經濟型的CPU核,即NiosII/e,如圖8.32所示。

圖8.32加入NIOSIICPU

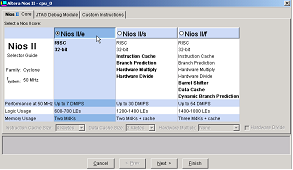

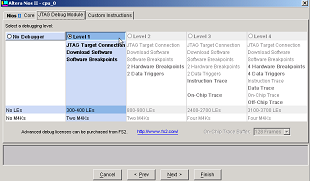

單擊“JTAGDebugModule”標簽頁,選擇第一級調試支持Level1:特點是占用邏輯資源少,編譯速度快,不包括緩存,如圖8.33所示。

圖8.33設置CPU調試模型

單擊“Finish”按鈕完成NiosIICPU的配置工作。項目中會增加一個NiosII處理器,名字為cpu_0,為了簡便起見,沒有將它改名。改名的方法是:單擊右鍵,選擇“Rename”,輸入名字后回車即可,如圖8.34。

圖8.34定制CPU完成圖

(3)SOPCBuilder定制JTAG串口。

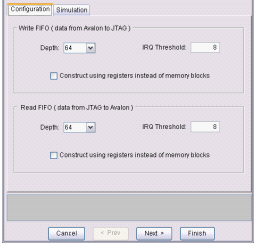

在左側器件池中雙擊“JTAGUARTInterface”,使用默認參數設置,如圖8.35所示。

它是NiosII系統嵌入式處理器新添加的接口元件,通過內嵌在AlteraFPGA內部的聯合測試行動組(JTAG)電路,在PC主機和FPGA之間進行串行字符流通信。特點是在運行時在調試區輸入信息可以與FPGA進行交互。

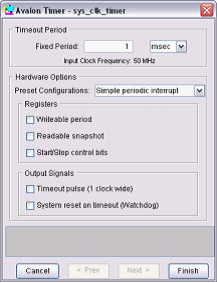

(4)SOPCBuilder定制計時器。

在左側器件池中雙擊“IntervalTimer”。定時器對于HAL系統庫中的器件驅動非常有用,比如JTAGUART驅動使用定時器來實現10s的暫停。選擇“IntervalTimer”,在設置向導中周期選擇1msec,預設置中選擇Full-featured,如圖8.36所示。

圖8.35JTAGUART參數設置 圖8.36計時器設置

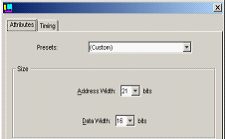

(5)SOPCBuilder定制外部Flash。

在左側器件池中雙擊“CompactFlashInterface”。在“Presets”中選自定義Custom,地址寬度21bits,帶寬16bits。由于Flash是通用設備,所以時序標簽使用默認設置。如圖8.37和8.38所示。

圖8.37Flash帶寬設參數置界面 圖8.38Flash時序參數設置界面

(6)SOPCBuilder定制外部SDRAM。

通常的系統都需要用戶指定一個內存空間,這個內存是指RAM,可以是片上的,也可以是片外的SDRAM或SRAM等。如果用戶程序較大,超出了FPGA所能定制的最大片上RAM容量,則也可以將程序放在SDRAM中運行。在左側器件池中雙擊“SDRAMcontroller”。

在“Presets”中選擇“micronMT48LC4M32B2-7chip”,其他的參數設置可以使用系統的默認選項,如圖8.39所示。

(7)SOPCBuilder定制外部RAM總線。

添加外部RAM總線(AvalonTri-StateBridge)。軟件使用Avalon接口來連接片上元件和Avalon主從端口。

圖8.39SDRAM參數設置

在Nios開發板上,要實現Nios系統與FPGA片外存儲器通信,就必須在Avalon總線和連接外部存儲器的總線之間添加一個橋,這個橋就是Avalon三態總線,如圖8.40所示。

圖8.40添加外部RAM總線

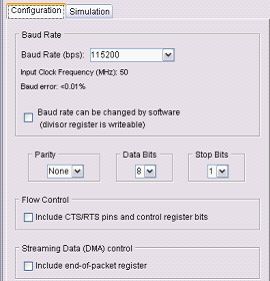

(8)SOPCBuilder定制串行通信設備UART。

通用串行總線RS-232協議是我們最常用的通信協議,所以把它也添加到我們的系統里。注意選擇所需的數據幀格式,如圖8.41所示。

(9)SOPCBuilder定制LCD液晶模塊。

使用標準16027字符型液晶顯示器。

(10)SOPCBuilder定制systemid。

在SOPCBuilder中使用默認定制的systemid。

(11)SOPCBuilder定制PIO。

添加4個LED和輸入設備按鍵開關PIO,這是一個標準SOPC一般所需要的設備。

(12)SOPCBuilder指定基地址和中斷編號。

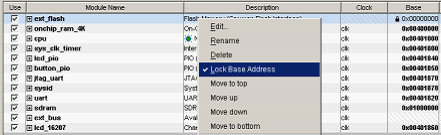

首先修改Flash的基地址為0x00000000,之后在Flash上單擊右鍵鎖定基地址,如圖8.42所示。

圖8.41串行通信設備UART參數設置

圖8.42鎖定Flash基地址

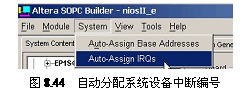

然后,選擇“System”/“Auto-AssignBaseAddresses”,讓系統自動分配基地址,如圖8.43所示。

圖8.43自動分配系統設備地址

最后,選擇“System”/“Auto-AssignIRQs”,讓系統自動分配中斷,如圖8.44所示。

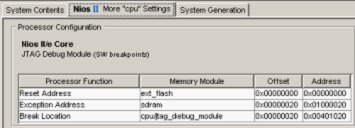

(13)SOPCBuilderNIOSIICPU其他設置。

單擊“NiosIIMore“cpu_0”Settings”選項卡,進行處理器設定。在本實例中,將“ResetAddress”修改為“ext_flash”,“ExceptionAddress”修改為“sdram”,“BreakLocation”使用默認值,如圖8.45所示。

圖8.45自動分配系統設備中斷編號

(14)生成軟嵌入式系統IP核。

單擊“SystemGeneration”選項卡,進行最后的設定并生成系統。選中“HDLGeneratesystemmodulelogicinVerilog”。如果需要仿真,也選擇“SimulationCreateModelSim(tm)projectfiles”,然后單擊“Generate”按鈕,執行系統生成的任務。

然后,耐心地等待系統的生成。一般沒有問題的話,可以看到系統提示“SUCCESS:SYSTEMGENERATIONCOMPLETED”。如果看到此信息,則說明系統被正確生成了。如果失敗,請返回并檢查、修改。

(15)在QuartusII工程中添加上述NIOS系統。

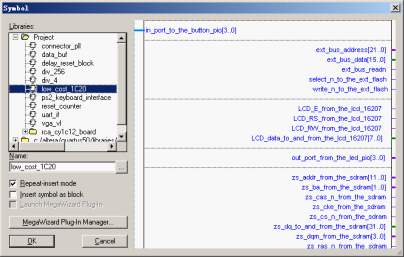

類似向QuartusII工程添加功能模塊一樣,將所定制的NiosII軟核CPU添加到本例工程中。雙擊工程頂層圖空白處,彈出“Symbol”對話框,在“Project”下面可以找到剛才建立的niosii_c模塊,如圖8.46所示。

圖8.46在QuartusII中添加IP核

單擊“OK”按鈕將其niosii_c添加到頂層圖中。

(16)在QuartusII工程中添加端口分配管腳編譯。

首先在QuartusII中將NIOS等端口添加至工程中,并為工程添加相應的管腳約束,然后即可對工程進行編譯。

(17)設計該工程軟件。

首先在AlteraSOPCBuilder中,點擊RunNiosIIIDE,啟動NiosIIIDE,如圖8.47所示。

圖8.47打開NIOSIIIDE軟件

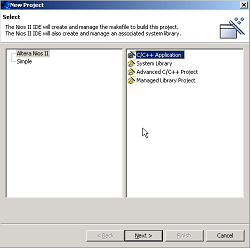

接下來我們要設計該工程的軟件。運行NiosIDE,在NiosIIIDE中,選擇“File”/“New”/“Project”選項,開啟“NewProject”對話框,選擇“C/C++Application”,如圖8.48所示。

圖8.48新建軟件工程

然后單擊“Next”按鈕,進入下一步,在模板中選擇“HelloLED”,如圖8.49所示。

單擊“SOPCBuilderSystem”右邊的“Browse”按鈕打開目錄對話框,從該工程目錄下找到“niosii_c.ptf”,因為NiosIIIDE必須從這個文件獲取該系統的相關信息。單擊“Finish”按鈕,即建立一個名為Hello_LED_0的模板。

打開項目中的文件:hello_led.c,根據需要進行修改。在本實例程序中,“PIO_0_BASE”名稱中的“PIO_0”應改為SOPCBuilder定義時的名稱,如圖8.49中的“Hello_LED_0”。

圖8.49采用設計模板

(18)編譯軟件。

右鍵單擊“hello_led_0”,在彈出的菜單中選擇“BuildProject”。(為使編譯過程更加順利,此時最好關閉殺毒軟件和其他占用電腦資源較大的軟件)。

如果無誤,可以看到以下信息:Buildcompleted。如果看到了這條提示,表示軟件編譯成功,可以看到程序占用空間等信息。

(19)下載驗證。

最后我們還要回到QuartusⅡ里面選擇“Tools”菜單里面的“Programmer”,下載整個配置到FPGA中去。

然后在NiosII環境中單擊“RunAsNiosIIHardware”按鈕將C程序下載到實驗板中。

本實例最終的硬件實現現象是led跑馬燈。

8.4.3小結

本節講解了一個完整的軟嵌入式設計流程。雖然此實例實現的功能比較簡單,但對于初學者來說,是一個不錯的入門實例。其中硬件設計部分(SoPCbuilder)包括開發板上所有設備,以后讀者可以在此硬件平臺上建立多個軟件運行。

評論