高速PCI信號采集卡設計與實現綜合實例之:樣機的調試方法和技巧

13.8樣機的調試方法和技巧

不管是復雜的電子系統還是簡單的電路,樣機的調試都是有一些基本步驟的。對于本案例的信號采集設備同樣如此。

最先進行的就是電源系統的調試,包括是否有短路、斷路,是否有虛焊,各電壓系統是否正常,電源模塊輸出電流是否足夠驅動負載等。只有電源系統正常工作,才能談得上實現系統功能。

完成了電源系統的調試后,PCI信號采集卡的下一個工作就是對PCI954進行配置。用戶可以通過編程器或者PLXMon工具在線進行燒寫。這個配置過程保證主機操作系統能夠識別出硬件設備。

主機能夠正確地識別硬件設備后,需要進行設備驅動程序的安裝。

通過上述步驟,主機已經可以正確地識別設備,并為用戶提供了可供操作的API接口。接下來要做的調試工作就是硬件工程師要完成的FPGA邏輯設計和軟件工程師要完成的應用軟件設計。但這兩部分并不能絕對分開進行設計,因為不管是對設備的I/O操作還是DMA操作都需要進行地址空間映射,因此都需要在軟件和硬件上進行相應的設計。

在本系統的FPGA調試和軟件聯調中,我們使用了兩個簡單的例子來驗證系統是否能夠正常的工作。一個是直接用FPGA控制的跑馬燈實例,另一個是通過應用軟件控制的跑馬燈實例。

13.8.1沒有PCI控制的跑馬燈

本實例僅用FPGA內部邏輯對LED進行控制,實現跑馬燈。通過本實例可以檢驗FPGA的兩種配置模式是否正常工作,同時可以學習使用QuartusII軟件開發和配置FPGA的流程。

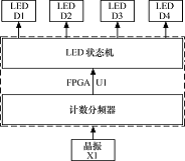

如圖13.23是本實例的系統框圖。

圖13.23跑馬燈系統框圖

其中計數分頻器是通過計數器將晶振的40MHz時鐘進行分頻,產生的低頻時鐘作為LED狀態機的控制時鐘。LED狀態機使用4個狀態分別表示4個LED的亮滅,狀態轉換通過狀態機的時鐘上升沿觸發,實現跑馬燈。

下面是這個實例FPGA內的主要Verilog源代碼。

//--計數分頻-------------------------------------

always@(posedgeclkin)

count=count+1; //分頻計數器

assignclk=count[24]; //狀態機時鐘

//--LED控制--------------------------------

always@(posedgeclk)begin

case(state)//跑馬燈狀態控制量

2d0: led=4b0001; //D1亮

2d1: led=4b0010; //D2亮

2d2: led=4b0100; //D3亮

2d3: led=4b1000; //D4亮

endcase

state=state+1;//跑馬燈狀態變化

end

13.8.2基于PCI控制的跑馬燈

本實例使用應用程序通過PCI總線(PCI9054)來對FPGA內部邏輯參數進行配置,實現對LED的控制。通過本實例可以檢驗開發板的驅動以及PCI的實時控制,同時學習應用程序和PCI9054進行通信的方法。

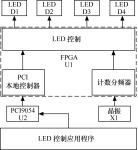

如圖13.24所示為本實例的系統框圖。

圖13.24基于PCI控制的跑馬燈系統框圖

其中PCI本地控制器實現與PCI9054的接口通信,獲取LED控制應用程序發出的觸發信號。LED控制器包含LED狀態機并接受PCI本地控制器的觸發信號,通過判別LED觸發的類型決定啟動單個LED控制或LED狀態機。

下面是這個范例FPGA內的主要Verilog源代碼。

//--計數分頻-------------------------------------

always@(posedgeclkin)

count=count+1; //分頻計數器

assignclk=count[24]; //狀態機時鐘

//--LED控制--------------------------------

always@(posedgeclk)begin

case(LEDByControl) //狀態控制量

8d1: led=4b0001; //PCI控制D1亮

8d2: led=4b0010; //PCI控制D2亮

8d3: led=4b0100; //PCI控制D3亮

8d4: led=4b1000; //PCI控制D4亮

8d5: case(state) //跑馬燈狀態控制量

2b00: led=4b0001; //跑馬燈D1亮

2b01: led=4b0010; //跑馬燈D2亮

2b10: led=4b0100; //跑馬燈D3亮

2b11: led=4b1000; //跑馬燈D4亮

endcase

default:led=4b0000; //跑馬燈全滅

endcase

state=state+1; //跑馬燈狀態變化

end

//--PCI本地控制器-------------------------------

always@(posedgeclkin)

lholda=lhold; //PCI本地總線占用請求及應答

always@(posedgeclkinornegedgelrst)begin

if(!lrst)begin//PCI9054復位

readyflag=1b0;

LEDByControl[7:0]=8b0;

end

elseif(!adslwrblastla[13:0]==14b1)

readyflag=1b1;//開始發起LED控制字IO配置

elseif(adslwrblastreadyflag==1b1la[13:0]==14b1)

readyflag=1b1;//捕獲發起操作

elseif(adslwr!blastreadyflag==1b1la[13:0]==14b1)begin

LEDByControl[7:0]=ld[31:24];//進行LED控制字IO配置操作

readyflag=1b0;

end

else begin

LEDByControl[7:0]=LEDByControl[7:0];//保持LED控制字

readyflag=1b0;

end

end

在進行FPGA的邏輯設計時,采用一種叫做虛擬邏輯分析儀的技術,可以增強我們診斷系統的能力。AlteraFPGA提供的虛擬邏輯分析儀稱為SignalTap,Xilinx中也有同樣功能的產品稱為ChipScope。

SignalTapII邏輯分析儀是Altera第二代系統級調試工具,能夠獲取、顯示可編程片上系統(SOPC)的實時信號,幫助工程師在其系統設計中觀察硬件和軟件的交互作用。在可編程邏輯市場上,SignalTapII邏輯分析儀專用于QuartusII軟件,與其他嵌入式邏輯分析儀相比,它支持的通道數最多,抽樣深度最大,時鐘速率最高。

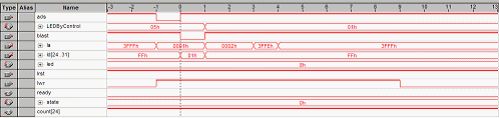

如圖13.25所示為控制其中一個LED時的PCI本地時序圖。

圖13.25控制1個LED的PCI本地時序圖

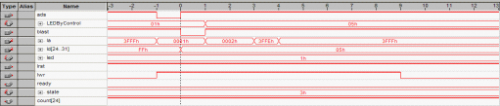

如圖13.26所示為控制4個LED進行跑馬燈時的PCI本地時序圖。

圖13.26控制4個LED跑馬燈的PCI本地時序圖

評論