信號去直流方法

利用FPGA進行數(shù)字信號處理時,信號中的直流分量通常需要去除,而直流分量在AD前段就存在,如果采用模擬電路去除直流分量比較復雜,因此通常在AD后端數(shù)字域去除直流分量。在FPGA中,常規(guī)去直流的方法是先對信號進行累加,然后對累加值進行移位即可得到直流分量,如累加8192個數(shù)據(jù),則直流分量可由累加值右移13位得到。

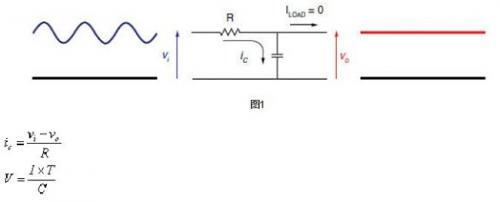

本文介紹一種根據(jù)Xilinx FPGA中DSP48E1資源設(shè)計的去直流模塊,其基本原理采用一階濾波器,如圖1所示,通過一個一階RC電路,在V0端可等效一個低通濾波器,得到直流分量。

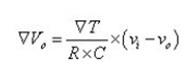

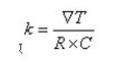

由上式可推導出,

定義系數(shù),

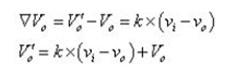

由此可得到下式:

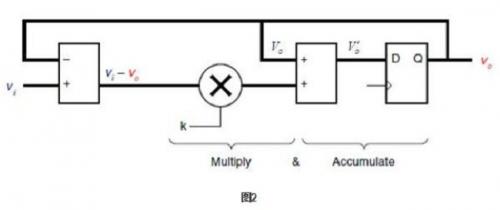

由上式可得到如圖2所示結(jié)構(gòu)

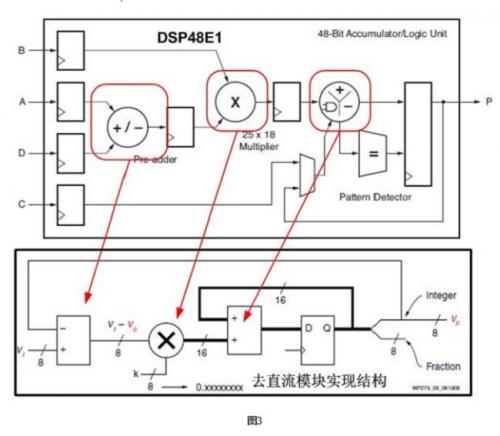

仔細觀察發(fā)現(xiàn)圖2中結(jié)構(gòu)與Xilinx FPGA的DSP48E1結(jié)構(gòu)十分相似,如圖3所示,兩個結(jié)構(gòu)做了類比,其中Vi - Vo的減法可由DSP48E1中的Pre-Adder實現(xiàn),k*(vi - vo)的乘法可由DSP48E1中的Multipler實現(xiàn),而Vo + k*(vi - vo)加法可由DSP48E1中的Accumulator實現(xiàn)。因此實現(xiàn)這個去直流模塊只需1個DSP48E1資源,并且在Xilinx 7系列FPGA中,DSP48E1最大支持25-bit的Pre-adder、25*18-bit的Multipler和48-bit的Accumulator,基本可滿足常規(guī)處理。

具體實現(xiàn):

在ISE的HDL language template中可以找到DSP48的宏定義,這邊需要用到ADDMACC_MACRO,只需要將這個宏模板拷貝到程序中直接例化即可調(diào)用DSP48,去直流模塊的DSP48E1實現(xiàn)代碼如下所示:

module DCOff_DSP(

input clk,

input rst,

input [15:0] din,

output [15:0] dc

);

wire signed [31:0] PRODUCT;

wire signed [15:0] K;

wire signed [31:0] ACOUT;

assign K=16h0085;

ADDMACC_MACRO #(

.DEVICE(7SERIES), // Target Device: VIRTEX6, SPARTAN6, 7SERIES

.LATENCY(4), // Desired clock cycle latency, 0-4

.WIDTH_PREADD(16), // Pre-adder input width, 1-25

.WIDTH_MULTIPLIER(16), // Multiplier input width, 1-18

.WIDTH_PRODUCT(32) // MACC output width, 1-48

) ADDMACC_MACRO_inst (

.PRODUCT(PRODUCT), // MACC result output, width defined by WIDTH_PRODUCT parameter

.CARRYIN(1b0), // 1-bit carry-in input

.CLK(clk), // 1-bit clock input

.CE(1b1), // 1-bit clock enable input

.LOAD(1b1), // 1-bit accumulator load input

.LOAD_DATA(PRODUCT), // Accumulator load data input, width defined by WIDTH_PRODUCT parameter

.MULTIPLIER(K), // Multiplier data input, width defined by WIDTH_MULTIPLIER parameter

.PREADD2(-PRODUCT[31:16]), // Preadder data input, width defined by WIDTH_PREADD parameter

.PREADD1(din), // Preadder data input, width defined by WIDTH_PREADD parameter

.RST(rst) // 1-bit active high synchronous reset

);

assign dc=PRODUCT[31:16];

endmodule

以下是得到的綜合報告,主要就使用了1個DSP48E1資源,并且最高時鐘頻率高達552MHz,可滿足通信系統(tǒng)中頻數(shù)據(jù)處理。

Selected Device : 7k325tfbg676-3

Slice Logic Utilization:

Number of Slice LUTs : 16 out of 203800 0%

Number used as Logic: 16 out of 203800 0%

Number of DSP48E1s: 1 out of 840 0%

Timing Summary:

Minimum period: 1.811ns (Maximum Frequency: 552.273MHz)

Minimum input arrival time before clock: 0.694ns

Maximum output required time after clock: 0.568ns

如圖4所示為去直流模塊的仿真波形,輸入為有直流偏置的正弦波,從圖中可看出輸出直流分量隨著濾波數(shù)據(jù)的增加慢慢收斂,而這個收斂速度取決于系數(shù)k,根據(jù)k的表達式可得,k的值取決于采樣周期和RC值,如果采樣頻率固定為245.76MHz,則RC值決定了k的取值。

根據(jù)多次仿真的到k的不同取值對模塊的影響:

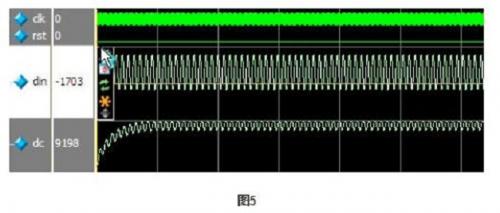

k取值越大,DC值收斂得越快;k取值越小,DC值越穩(wěn)定、越平滑。因此,不是k取值越大越好,收斂快但是波動比較大,如圖5所示,這樣直流分量肯定是濾不干凈的。

究其原因,得從原理上著手,翻看了一下信號與系統(tǒng)書(這些基本概念長時間不用都還給老師了,平時還得多注意復習一下基礎(chǔ)知識),原來k的值決定了這個低通濾波器的截止頻率,輸出直流分量的波動性不僅僅跟k值有關(guān),還與輸入信號頻率和采樣頻率有關(guān),在本文實例中,輸入信號頻率為5MHz,采樣頻率為245.76MHz,在圖4中k=0x85,圖5中k=0x400,如圖6所式為k的兩個取值得到濾波器的幅頻特性,并且標出了輸入信號所在頻點(5MHz/245.76*2=0.04068)的幅度特性,分別為-29.98dB和-12.6dB,相差了近20dB。因此在設(shè)計去直流模塊時應(yīng)根據(jù)實際應(yīng)用情況決定k的取值。

本文介紹了一種信號去直流的新方法,但不是所有場合都試用,如果FPGA平臺DSP資源比較少,如SPARTAN系列,建議采用常規(guī)累加+移位的方法。而本文實例中采用Kintex7系列FPGA,有豐富的DSP資源,而采用此方法整個模塊只需要1個DSP48E1,并且能高速處理,因此非常適用。

評論