基于FPGA的IIR數(shù)字濾波器的設(shè)計(jì)方案

1.引言

數(shù)字濾波器在通信、自動(dòng)控制、雷達(dá)、軍事、航空航天、醫(yī)療、家用電器等眾多領(lǐng)域得到了廣泛的應(yīng)用。其中IIR數(shù)字濾波器和FIR數(shù)字濾波器是目前人們使用較多的兩種。數(shù)字濾波器通常采用計(jì)算機(jī)軟件、專用數(shù)字濾波器、DSP器件或可編程邏輯器件(如FPGA)實(shí)現(xiàn)。因?yàn)椋?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/FPGA">FPGA實(shí)現(xiàn)數(shù)字濾波器具有實(shí)時(shí)性強(qiáng)、靈活性高、處理速度快以及小批量生產(chǎn)成本低等優(yōu)點(diǎn),所以得到了較為廣泛的應(yīng)用。本文以巴特沃思數(shù)字帶通濾波器為例,較為詳細(xì)地介紹了其設(shè)計(jì)和實(shí)現(xiàn)方法。給定巴特沃茲數(shù)字帶通濾波器的抽樣頻率為500Hz,上、下邊帶截止頻率分別為150Hz和30Hz。

2.濾波器的系統(tǒng)模型

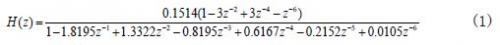

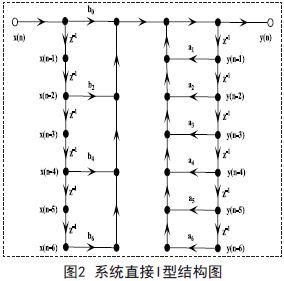

雙線性變換法是在低通濾波器的基礎(chǔ)上采用頻率變換法把低通濾波器轉(zhuǎn)換成所需要濾波器的。據(jù)此方法,我們得到如下濾波器的系統(tǒng)模型:

3.Matlab仿真

針對(duì)式(1)所描述的系統(tǒng)模型,利用Matlab軟件工具箱函數(shù)freqz(b,a,N,F(xiàn)s)繪制出其幅頻特性和相頻特性,以檢驗(yàn)參數(shù)的正確性。該濾波器的幅相頻率特性如圖1所示。

由圖1可見(jiàn),系統(tǒng)的上、下邊帶分別為150Hz和30Hz,滿足系統(tǒng)設(shè)計(jì)要求。

4.FPGA設(shè)計(jì)

4.1濾波器的結(jié)構(gòu)

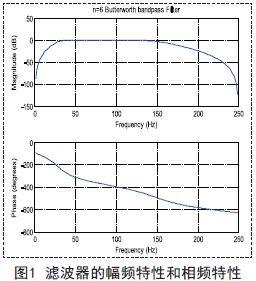

同一系統(tǒng)函數(shù)的IIR濾波器可以用不同的結(jié)構(gòu)來(lái)實(shí)現(xiàn),如直接I型、直接II型(典范型)、級(jí)聯(lián)型和并聯(lián)型。不同的結(jié)構(gòu)有不同的特點(diǎn),為便于硬件實(shí)現(xiàn)及容易確定數(shù)據(jù)位數(shù),本文選用直接I型這一結(jié)構(gòu)形式。

系統(tǒng)的直接I型結(jié)構(gòu)如圖2所示。

4.2 FPGA主要模塊

(1)D觸發(fā)器模塊

使用D觸發(fā)器來(lái)實(shí)現(xiàn)圖2中所需的延時(shí)功能。每當(dāng)時(shí)鐘上升沿到來(lái)時(shí),便對(duì)輸入的數(shù)據(jù)進(jìn)行鎖存。D觸發(fā)器可以利用Quartus II軟件中LPM宏模塊定制實(shí)現(xiàn)。

(2)乘累加模塊

由式(1)所描述的濾波器的系統(tǒng)模型,可得所對(duì)應(yīng)的差分方程如下:

乘累加模塊承擔(dān)式(2)中乘累加的計(jì)算工作。

5.系統(tǒng)框圖及實(shí)驗(yàn)波形圖

利用數(shù)字濾波器實(shí)現(xiàn)模擬信號(hào)濾波的系統(tǒng)結(jié)構(gòu)框圖如圖3所示。

模擬輸入信號(hào)經(jīng)A/D轉(zhuǎn)換器轉(zhuǎn)換為數(shù)字信號(hào),用FPGA數(shù)字濾波器進(jìn)行濾波處理,再經(jīng)D/A轉(zhuǎn)換器轉(zhuǎn)換為模擬輸出信號(hào),完成模擬信號(hào)的濾波處理。FPGA芯片采用的是Cyclone II系列EP2C5T144C8型FPGA.A/D和D/A轉(zhuǎn)換器采用的康芯高速ADC/DAC模塊。

輸入峰峰值為5V的正弦信號(hào),周期分別為10Hz、100Hz和200Hz,經(jīng)濾波系統(tǒng)處理后所得輸出信號(hào)波形分別如圖4、5、6所示,輸出信號(hào)幅度分別為400mV、2.32V、1.2V。

6.結(jié)語(yǔ)

本方案利用FPGA實(shí)現(xiàn)了巴特沃茲IIR數(shù)字帶通濾波器,并給出較為詳細(xì)的方案設(shè)計(jì)過(guò)程。實(shí)驗(yàn)結(jié)果證明了所設(shè)計(jì)的濾波器完全滿足預(yù)定設(shè)計(jì)要求,從而也證實(shí)了本方案的有效性、可行性。

評(píng)論