面向 FPGA 的 ESL 工具

邏輯設計領域正在發生根本變化。新一代設計工具幫助軟件開發者將其算法表達直接轉換成硬件,而無需學習傳統的硬件設計技術。

這些工具及相關設計方法學一起被歸類為電子系統級 (ESL|0">ESL) 設計,廣泛地指從比目前主流的寄存器傳輸級 (RTL) 更高的抽象級別上開始的系統設計與驗證方法學。與硬件語言如 Verilog 和 VHDL比起來,ESL 設計語言在語法和語義上與流行的 ANSI C 比較接近。

ESL 與 FPGA 有何關系?

ESL 工具已經存在了一段時間,而許多人覺得這些工具主要專注于 ASIC 設計流程。然而事實上,越來越多的 ESL 工具提供商正在專注于可編程邏輯;目前,市場上有多種工具支持專為賽靈思® FPGA 而優化的系統設計流程。ESL 流程是對 FPGA 設計工具的一種自然演進,可以使更多和更廣泛以軟件為中心的用戶群更容易地使用可編程硬件的靈活性。

我們來考慮一些由 ESL 和 FPGA 構成重大組合的情景:

- ESL 工具和可編程硬件一起構成一個基于桌面的硬件開發環境,符合軟件開發者的工作流程模型。工具可提供針對特定的基于 FPGA 的參考板的優化支持,軟件開發者可以利用這些支持啟動項目評估或原型構建。這些板及相應的參考應用程序均使用更高級別的語言編寫,這使創建定制的、硬件加速的系統更為快速和容易。實際上,現在軟件程序員能夠以使用微處理器參考板及工具大體相同的方式,使用基于 FPGA 的參考板及工具。

- 通過使用現在FPGA 中已很普遍的高性能嵌入式處理器,軟件和硬件設計組件可以裝入到一個器件中。從系統的軟件描述開始,您可以根據應用程序的性能要求,將每個設計塊用硬件或軟件來實現。ESL 工具支持智能分割和軟件功能到等效硬件功能的自動導出,從而增加了價值。

ESL 提升了“探測式設計和優化”的概念。ESL 方法學與可編程硬件的結合使用,使嘗試大量可能的應用實現以及對極大不同的軟件/硬件分割策略快速進行實驗成為可能。這種實驗的能力——嘗試新方法和快速分析性能與尺寸平衡——使 ESL/FPGA 用戶能夠比使用傳統的 RTL 方法以更短的時間實現更高的總體性能。

此外,通過在更抽象的級別上工作,您可以使用更少的擊鍵和更少的代碼行來表達您的意圖。這通常意味著快得多的設計完成,和更少的犯錯機會,而這些錯誤將需要繁雜的、低級調試。

ESL 的目標受眾

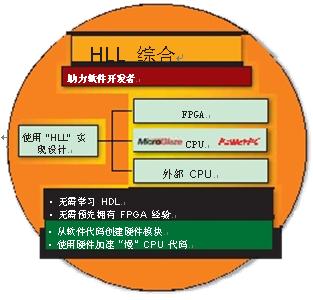

ESL 流程對預期 FPGA 用戶的主要好處是其生產率和易用性。通過將產生硬件電路的實現細節進行抽象,這些工具向以軟件為中心的用戶群(圖 1)發出了召喚。在更高的抽象級別上工作,使擁有 C 語言等傳統軟件編程語言技能的設計者能夠更快地以硬件探究其想法。在大多數情況下,您可以無需經驗豐富的硬件設計者的幫助而完成整個設計的硬件實現。

以軟件為中心的應用程序和算法開發者已將該方法的優點應用于 FPGA,他們包括系統工程師、科學家、數學家、和嵌入式與固件開發者。

適合 ESL 方法學的應用程序的特征包括具有大量內循環的計算密集型算法。這些應用程序可以通過硬件中的并發并行執行實現巨大加速。ESL 工具已在音頻/視頻/圖像處理、加密、信號與分組處理、基因排列、生物信息、地球物理和天體物理等應用領域成功幫助進行了項目部署。

ESL 設計流程

與 FPGA 相關的 ESL 工具包含兩個主要設計流程:

1、高級語言 (HLL) 綜合。HLL 綜合覆蓋算法或行為綜合,可從 C 或C類的軟件語言生成硬件電路。各種合作伙伴解決方案采用不同的方法將高級設計描述轉換為 FPGA 實現。如何完成這一點構成了各種 ESL 產品之間的根本不同。

您可以將 HLL 綜合用于各種應用情況,包括:

- 模塊生成。在這種使用模式下,HLL 編譯器可以將以 C 表示的功能塊(例如一個 C 子程序)轉換成相應的硬件塊。生成的硬件塊隨后被收入整個硬件/軟件設計。這樣,HLL 編譯器生成了整個設計的一個子模塊。

模塊生成通過快速生成,然后集成算法硬件組件,允許軟件工程師參與整個系統的設計。那些尋求以更快的方式構建新的、以計算為導向的硬件塊的硬件工程師們,也可以使用模塊生成。 - 處理器加速。在這種使用模式下,HLL 編譯器允許通過在 FPGA 的可編程結構中創建定制加速器塊,來加速在處理器中運行的時間關鍵功能或瓶頸功能。

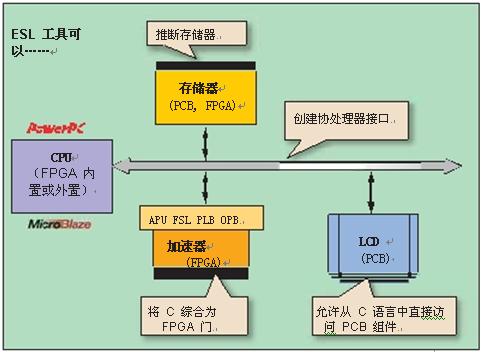

除創建加速器外,這些工具還可以自動推斷存儲器并生成所需的硬件-軟件接口電路,以及實現處理器與硬件加速器塊之間通信的軟件設備驅動程序(圖 2)。與運行在 CPU 中的代碼相比,FPGA 加速的代碼其運行速度可以快幾個數量級,而消耗的功率則大大降低。

2、系統建模。對于大型設計,或處理器用作整個設計的一部分時,使用傳統的 RTL 模型進行系統仿真可能會非常慢。一種流行的新興 ESL 方法采用了高速事務級模型,通常使用 C++ 編寫,以大大加快系統仿真速度。

ESL 工具為您提供了一種基于虛擬平臺的驗證環境,您可以在其中分析和調整設計的功能和性能屬性。這意味著可以更早使用系統的虛擬表示,實現更大的設計探索和假設分析。

您可以評估和改進性能問題,如延遲、吞吐率和帶寬,以及選擇性的軟件/硬件分割策略。一旦設計滿足性能目標,就可將其付諸硅實現。

|

圖 1:大多數用于 FPGA 的 ESL 工具均針對以軟件為中心的用戶群。 |

|

圖 2:ESL 工具抽象了在 FPGA 中加速處理器應用程序有關的細節。 |

ESL 工具提供商面臨的挑戰

相對而言,面向 FPGA 的 ESL 工具對市場來說是新生事物;客戶接受仍然是一個關鍵挑戰。ESL 工具提供商面臨的最大挑戰之一,是需要克服人們對 ESL 和 FPGA 能夠做什么,已存在哪些解決方案和功能,以及該技術的實際用途和優點等問題的普遍性認識不足。其他挑戰還包括用戶對結果質量的理解和關注以及與 ESL 接受相關的學習曲線。

盡管一些如由 ESL 引入的范例轉換,需要長時間才可為現有 FPGA 用戶社區完全接受,我們仍需要解決目前阻礙接受的一些關鍵問題。這一點尤為重要,因為今天的 ESL 技術已做好準備,向潛在的大量目標受眾提供重大實踐價值。

賽靈思 ESL 倡議

賽靈思認為 ESL 工具具有極大地改變硬件和軟件設計者創建、優化和驗證復雜電子系統方式的潛力。為了將這一新興技術的全部優點帶給客戶,和建立一種適用于特別針對 FPGA 的 ESL 技術的公共平臺,賽靈思積極聯絡其生態系統合作伙伴,成立了協作性的聯合 ESL 倡議(表 1)。

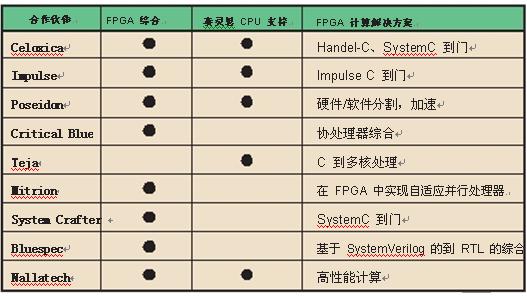

|

表 1:賽靈思 ESL 合作伙伴采用從高級語言到 FPGA 實現的不同方法。 |

該倡議的宗旨是加快針對 FPGA 的 ESL 創新步伐,和使該技術更貼近以軟件為中心的用戶群的需求。作為倡議的一部分,有以下兩個重點:

- 工程協作。賽靈思將與合作伙伴緊密合作,繼續進一步提升 ESL 產品陣營的價值。這將包括改進編譯器結果質量和增強工具互操作性及總體易用性等工作。

- ESL 認識與宣傳。賽靈思將向當前及預期新客戶宣傳面向 FPGA 的 ESL 流程的價值和優點。該計劃將試圖告知和教育用戶有關目前已有 ESL 解決方案類型的知識,以及各種產品如何提供解決現有問題的更好方法。目的是幫助用戶就各種合作伙伴 ESL 產品滿足其專用需求的適合性做出信息全面的決策。更大的認識將導致客戶接受度提高,反過來又會促進可持續的面向 FPGA 的合作伙伴 ESL 生態系統。

開始使用 ESL

作為構筑各種面向 FPGA 的 ESL 努力的更大認識的第一步,賽靈思已組合各種資源推出了一個全面的 ESL 網站。其內容涵蓋目前市場上每個合作伙伴 ESL 解決方案的專門及獨特方面,旨在幫助您決定哪個(若有的話)可用解決方案最適合您的應用。要開始您的 ESL 導向,請訪問 www.xilinx.com/esl。

此外,賽靈思還開設了一個新的面向 FPGA 的 ESL 論壇,地址為:http://toolbox.xilinx.com/cgi-bin/forum。在這里,您可以參與針與面向 FPGA 的 ESL 設計有關的各種主題的討論。

結論

面向 FPGA 的 ESL 工具為您提供了通過可編程硬件探索您的想法而無需學習與硬件設計有關的低層細節的能力。今天,您有機會從廣泛的創新和生產率增強解決方案中選擇專門針對賽靈思 FPGA 優化的解決方案。隨著 ESL 倡議的正式發布,賽靈思全面投入與第三方生態系統的合作,力圖為當前及潛在未來客戶提供最佳的 ESL 工具。面向持續更新和新開發隨時做好準備。

作者:Milan Saini 技術營銷經理 賽靈思公司 @xilinx.com">milan.saini@xilinx.com

評論